运算器组成实验(计算机组成原理)

1、熟悉逻辑测试笔的使用方法;

2、熟悉LK-TEC-9模型计算机的节拍脉冲T1、T3、T3;

3、熟悉双端口通用寄存器组的读写操作;

4、熟悉运算器的数据传送通路;

5、验证74LS181的加、减、与、或功能;

6、按给定的数据,完成几种指定的算术、逻辑运算

2.1.2实验内容

(1) 运算器组成实验:为程序控制方式

1.实验准备 将控制器转换开关拨到微程序位置,将编程开关设置为正常位置,将开关 DP 拨到向上 位置。打开电源。

2.用逻辑测试笔测试节拍脉冲信号 T1、T2、T3

⑴将逻辑测试笔的一端插入 TEC-8 实验台上的“逻辑测试笔”上面的插孔中,另一端插 入“T1”上方的插孔中。

⑵按复位按钮 CLR,使时序信号发生器复位。

⑶按一次逻辑测试笔框内的 Reset 按钮,使逻辑测试笔上的脉冲计数器复位,2 个黄灯 D1、D0 均灭。

⑷按一次启动按钮 QD,这时指示灯 D1、D0 的状态应为 01B,指示产生了一个 T1 脉冲; 如果再按一次 QD 按钮,则指示灯 D1、D0 的状态应当为 10B,表示又产生了一个 T1 脉冲; 继续按 QD 按钮,可以看到在单周期运行方式下,每按一次 QD 按钮,就产生一个 T1 脉冲。

⑸用同样的方法测试 T2、T3。 3.进行加、减、与、或实验 ⑴设置加、减、与、或实验模式按复位按钮 CLR,使 TEC-8 实验系统复位。指示灯 µA5~µA0 显示 00H。将操作模式开关 设置为 SWC=1、SWB=0、SWA=1,准备进入加、减、与、或实验。按一次 QD 按钮,产生一组节拍脉冲信号 T1、T2、T3,进入加、减、与、或实验。

⑵设置数 A 指示灯 µA5~µA0 显示 0BH。在数据开关 SD7~SD0 上设置数 A。在数据总线 DBUS 指示灯 D7~D0 上可以看到数据设置的正确不正确,发现错误需及时改正。设置数据正确后,按一次 QD 按钮,将 SD7~SD0 上的数据写入 R0,进入下一步。

⑶设置数 B 指示灯 µA5~µA0 显示 15H。这时R0 已经写入,在指示灯 B7~B0 上可以观察到 R0 的值。在数据开关 SD7~SD0 上设置数 B。设置数据正确后,按一次 QD 按钮,将 SD7~SD0 上的数据 写入 R1,进入下一步。

⑷进行加法运算 指示灯 µA5~µA0 显示 16H。指示灯A7~A0 显示被加数 A(R0),指示灯 B7~B0 显示加数 B(R1),D7~D0 指示灯显示运算结果 A+B。按一次 QD 按钮,进入下一步。

⑸进行减法运算 指示灯 µA5~µA0 显示 17H。这时指示灯 C(红色)显示加法运算得到的进位 C,指示灯 Z(绿 色)显示加法运算得到的结果为 0 信号。指示灯 A7~A0 显示被减数 A(R0),指示灯 B7~B0 显 示减数 B(R1),指示灯 D7~D0 显示运算结果 A-B。按一次 QD 按钮,进入下一步。

⑹进行与运算 指示灯 µA5~µA0 显示 18H。这时指示灯 C(红色)显示减法运算得到的进位 C,指示灯 Z(绿 色)显示减法运算得到的结果为 0 信号。 指示灯 A7~A0 显示数A(R0),指示灯 B7~B0 显示数 B(R1),指示灯 D7~D0 显示运算结果 A and B。按一次 QD 按钮,进入下一步。

⑺进行或运算 指示灯 µA5~µA0 显示 19H。这时指示灯 Z(绿色)显示与运算得到的结果为 0 信号。指示 灯 C 保持不变。指示灯 A7~A0 显示数 A(R0),指示灯B7~B0 显示数 B(R1),指示灯 D7~D0 显示运算结果 A or B。按一次 QD 按钮,进入下一步。

⑻结束运算 21 指示灯 µA5~µA0 显示00H。这时指示灯 Z(绿色)显示或运算得到的结果为 0 信号。指示 灯 C 保持不变。 按照上述步骤,对要求的 7 组数据进行运算。

|

3.用双踪示波器和逻辑测试笔测试节拍脉冲信号 T1、T2、T3。 2.对下述 7 组数据进行加、减、与、或运算。 ⑴A=F0H,B=10H ⑵A=FFH,B=AAH ⑶A=10H,B=F0H ⑷A=55H,B=AAH ⑸A=03H,B=05H ⑹A=C5H,B=61H ⑺A=0AH,B=0AH

(2) 运算器组成实验:独立控制方式

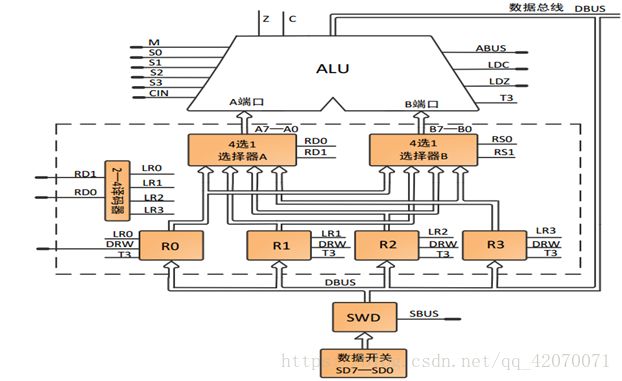

上图 2.3 标识出了本实验所用的运算器数据通路图。参与运算的数据首先通过试验 台操作板上的8 个二进制数据开关 SD7-SD0 来设置,然后输入到双端口通用寄存器堆 RF 中。 双端口寄存器堆 RF 由1 个 ALTERA EPM 7064 实现,功能相当于 4 个八位通用寄存器,用于保存参与运算的数据,运算后的结果也要送到双端口通用寄存器堆 RF 中保存。 双端口寄存器堆模块 RF 的控制信号中 RD1、RD0 用于选择送 ALU 的 A 端口(左端口)的通 用寄存器。RS1、RS0 用于选择送 ALU 的 B 端口(右端口)的通用寄存器。

(2) 实验任务 1.按图所示,将运算器模块与实验台操作板上的线路进行连接。由于运算器模块内部的连线已经由印制电路板连接好,故接线任务仅仅是完成数据开关、控制信号模拟开关、与运算 模块的外部连线。特别注意:为了建立清楚的整机概念,培养严谨的科研能力,手工连线时绝对有必要的。

2.用开关 K15-K0 向通用寄存器堆 RF 内的 R3-R0 寄存器置数据。然后读出 R3-R0 的数据,在 数据总线 DBUS 上显示出来。 3.验证 ALU 的正逻辑算术、逻辑运算功能。 注意:进位信号 C 是运算器 ALU 最高进 Cn+4的反,既有进位为 1,无进位为 0。

|

选择方式 |

|

M=1逻辑运算 |

M=0算术运算 |

|

S3 |

S2 |

S1 |

S0 |

逻辑运算 |

CN=1【有进位】 |

0 |

0 |

0 |

0 |

F=/A |

F=A |

0 |

0 |

0 |

1 |

F=/(A+B) |

F=(A+B) |

0 |

0 |

1 |

0 |

F=(/A)B |

F=A+/B |

0 |

0 |

1 |

1 |

F=0 |

F=-1(补码形式) |

0 |

1 |

0 |

0 |

F=/(AB) |

F=A加A(/B) |

0 |

1 |

0 |

1 |

F=/B |

F=(A+B)加A/B |

0 |

1 |

1 |

0 |

|

F=A减B减1 |

0 |

1 |

1 |

1 |

F=A/B |

F=(AB/)减1 |

1 |

0 |

0 |

0 |

F=/A+B |

F=A加AB |

1 |

0 |

0 |

1 |

|

F=A加B |

1 |

0 |

1 |

0 |

F=B |

F=(A+/B)加AB |

1 |

0 |

1 |

1 |

F=AB |

F=AB减1 |

1 |

1 |

0 |

0 |

F=1 |

F=A加A |

1 |

1 |

0 |

1 |

F=A+/B |

F=(A+B)加A |

1 |

1 |

1 |

0 |

F=A+B |

F=(A+/B)加A |

1 |

1 |

1 |

1 |

F=A |

F=A减1 |

2.1.3 实验记录

实验数据 |

实验结果 |

||||||||||||

数A |

数B |

加 |

减 |

乘 |

除 |

||||||||

数据结果 |

C |

Z |

数据结果 |

C |

Z |

数据结果 |

Z |

数据结果 |

C

|

||||

F0H |

10H |

00000000B |

1 |

1 |

11100000B |

1 |

1 |

00010000B |

1 |

11110000B |

1 |

||

FFH |

AAH |

00000000B |

1 |

1 |

00100000B |

1 |

1 |

00010000B |

1 |

11110000B |

1 |

||

10H |

F0H |

00010100B |

1 |

1 |

11111110B |

1 |

1 |

000000001B |

1 |

00000111B |

1 |

||

55H |

AAH |

00010100 |

1 |

1 |

00000000B |

1 |

1 |

00001010B |

1 |

00001010B |

1 |

||

03H |

05H |

10101001B |

1 |

1 |

01010101B |

1 |

1 |

10101010B |

1 |

11111111B |

1 |

||

C5H |

61H |

11111111B |

1 |

1 |

10101011B |

1 |

1 |

00000000B |

1 |

11111111B |

1 |

||

0AH |

0AH |

00100010B |

1 |

1 |

01100100B |

1 |

1 |

01000000B |

1 |

111000101B |

1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

on代表灯亮off代表灯灭.