TMS320F28335之默认中断系统

中断系统原理

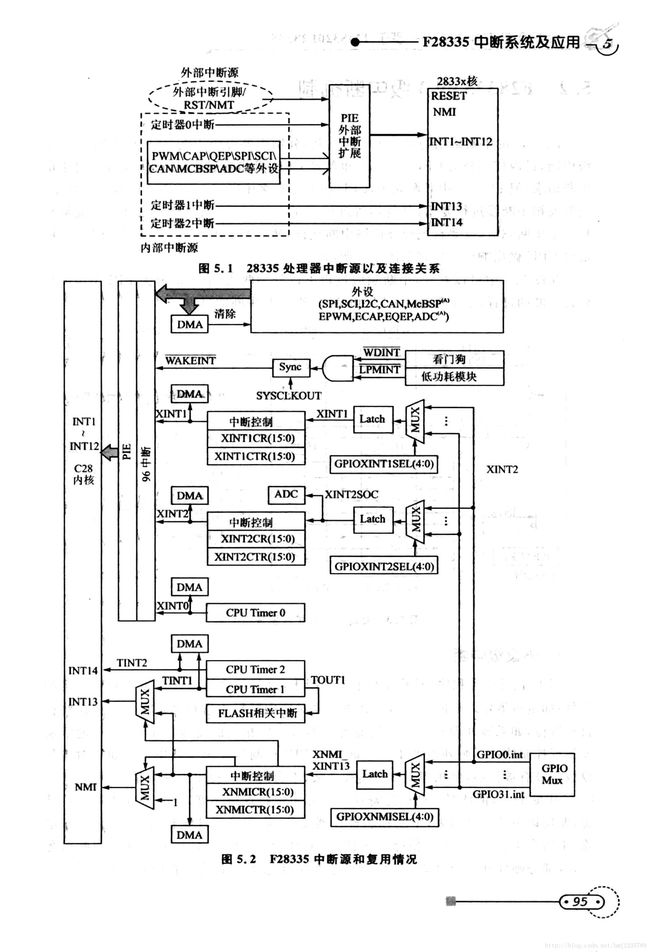

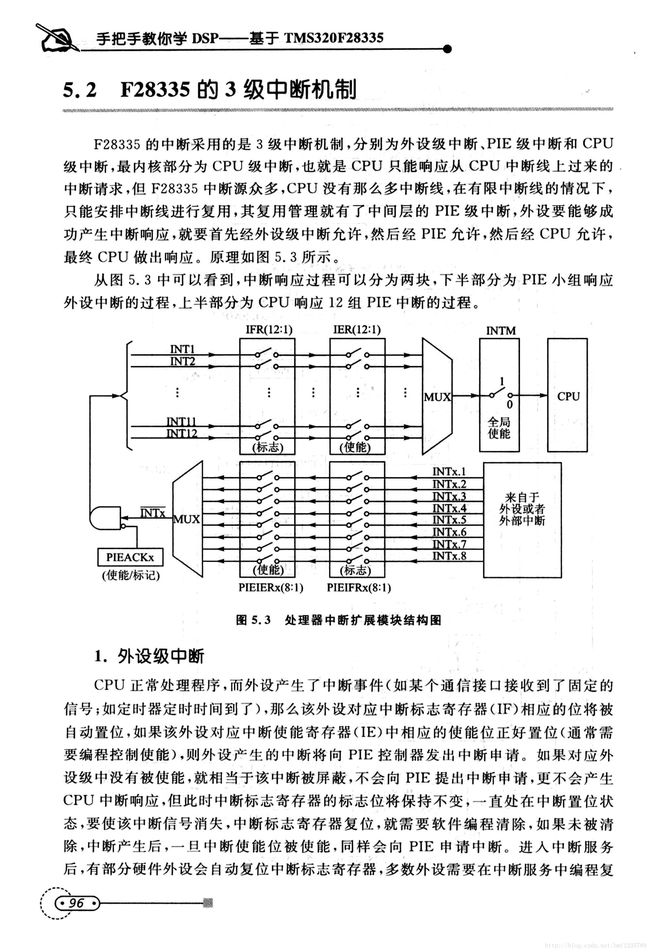

整个中断系统的过程如上所示:

1、外设级

外设产生中断时,该中断事件相关的中断标志位(IF)置1。此时,如果该中断相应的中断使能寄存器(IE)也置为1,外设就会向PIE控制器发出一个中断请求。如果外设级中断没有被使能(相应的使能位为0),那么外设就不会向PIE发出中断请求,相应的中断标志位会一直保持置1状态,除非用软件清除。当然,在中断标志位保持在1的时候,一旦该中断被使能了,那么外设立马会向PIE发出中断申请。不管在什么情况下,外设寄存器中的中断标志位必须采用软件进行清除。

小结:外设中断的屏蔽,需要将与该中断相关的外设寄存中的中断使能位置0。

外设中断标志位的清除,需要将与该中断相关的外设寄存中的中断标志位 置1。

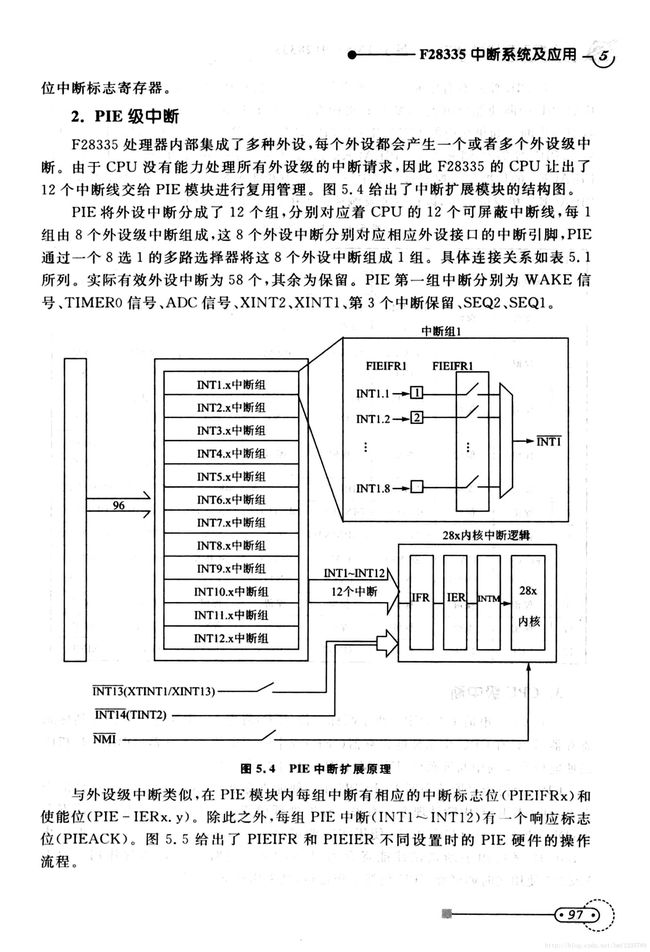

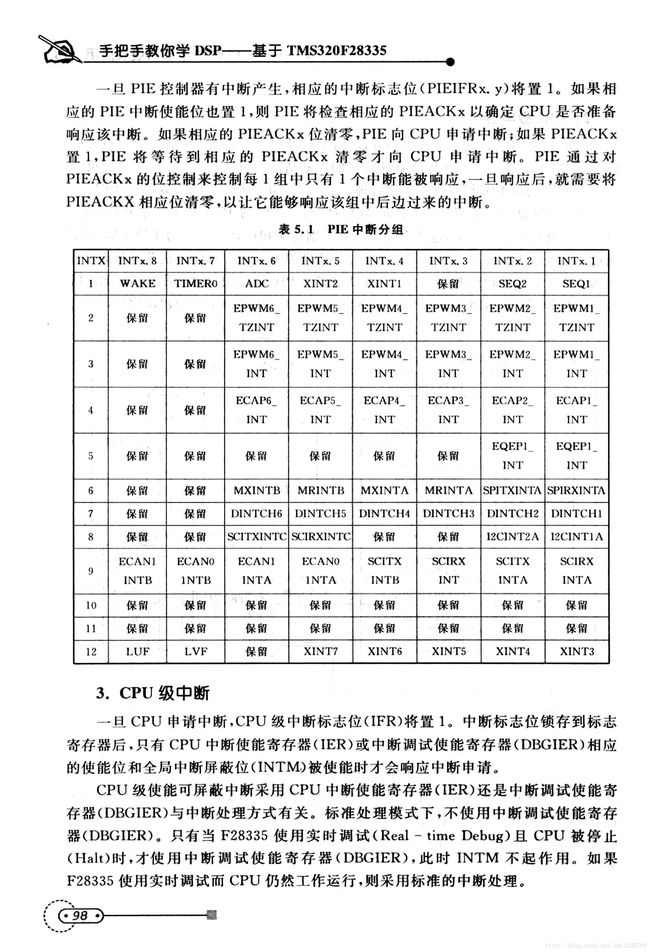

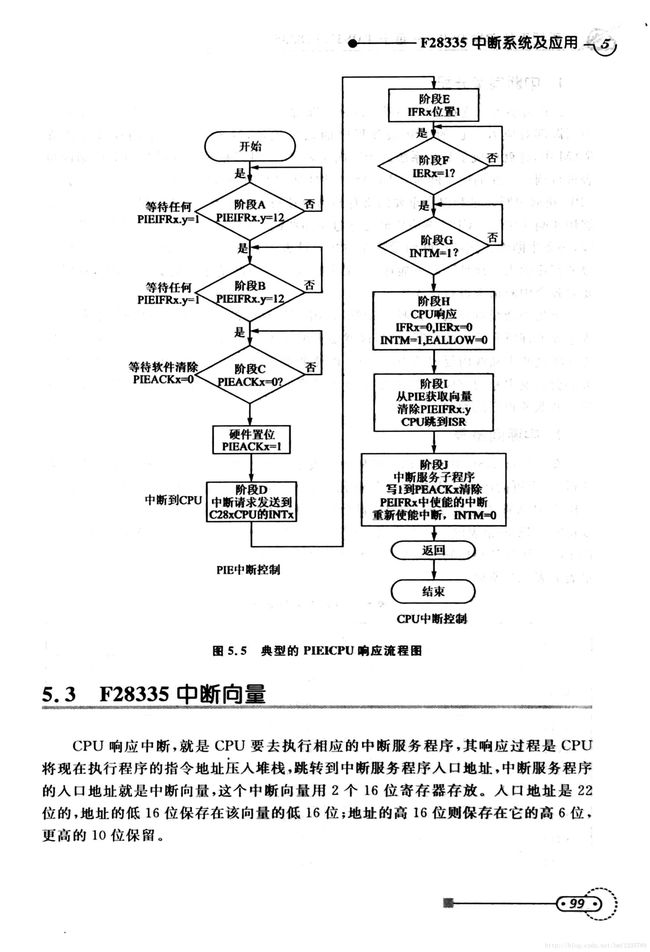

2、PIE级

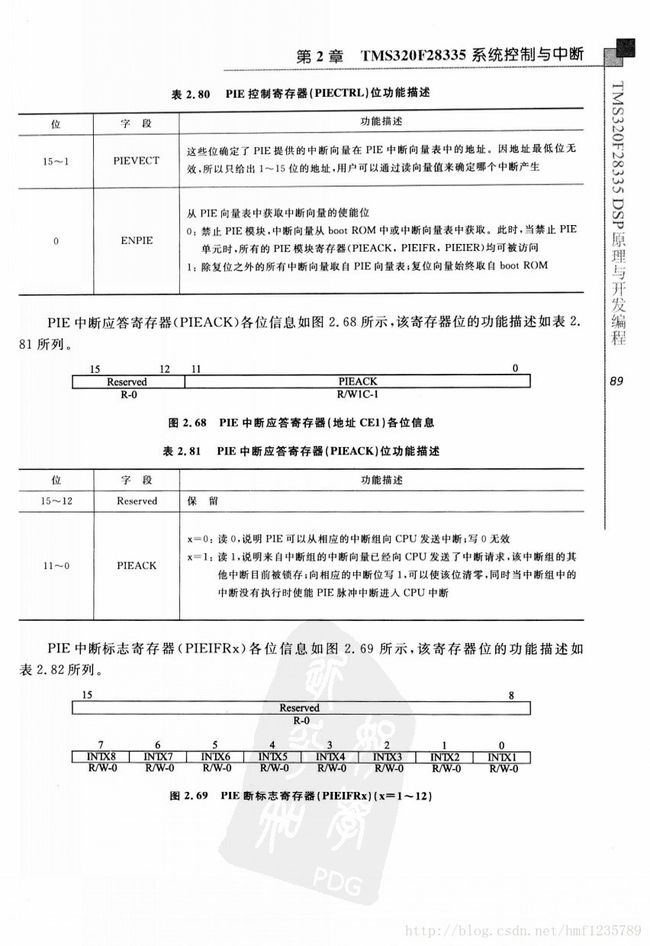

当外设产生中断事件,相关中断标志位置位,中断使能位使能之后,外设就会把中断请求提交给我们的PIE模块。PIE模块将96个外设和外部引脚的中断进行了分组,分为12组,每组8个中断,分别是PIE1-PIE12。每个组的中断被多路汇集进入1个CPU中断,例如PDPINDA,PDPINDB,XINT1,XINT2,ADCINT,TINT0,WAKEINT这7个中断都在PIE1组内,这些中断都汇集到CPU中断的INT1。 和外设级类似的,PIE控制器中的每个组都会有一个中断标志寄存器PIEIFRx和和中断使能寄存器PIEIERx,当然x=1…..12。每个寄存器的低8位对应于8个外设中断,高8位保留。

小结:

PIE中断的使能。就得将其相应组的使能寄存器PIEIERx的相应位进行置位。

PIE中断的屏蔽。这是和使能相反的操作。

PIE应答寄存器 PIEACK相关位的清除,以使得CPU能够响应同组的其他中断。

PIE级的中断和外设级的中断比较,外设中断的中断标志位是需要软件清除的,而PIE级的中断标志位都是自动置位或者清除的。但是PIE多了一个PIEACK寄存器,同一时间只能放一个中断过去,只有等到这个中断被响应,给PIEACK置位,才能让同组的下一个中断过去,被CPU响应,而PIEACK当响应一次中断后就会自动置位,因此需要软件写1清0。

3、CPU级

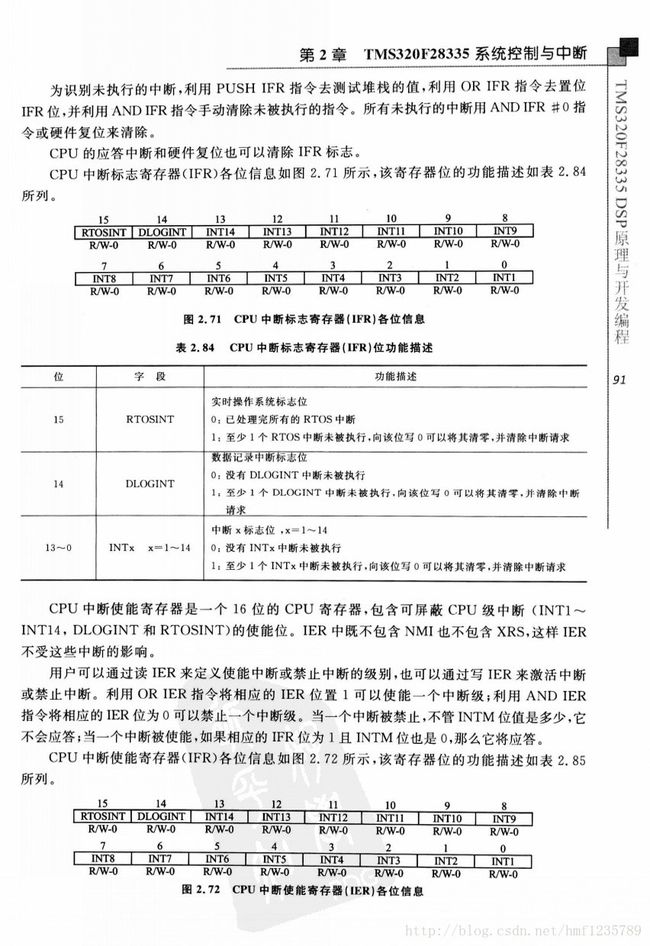

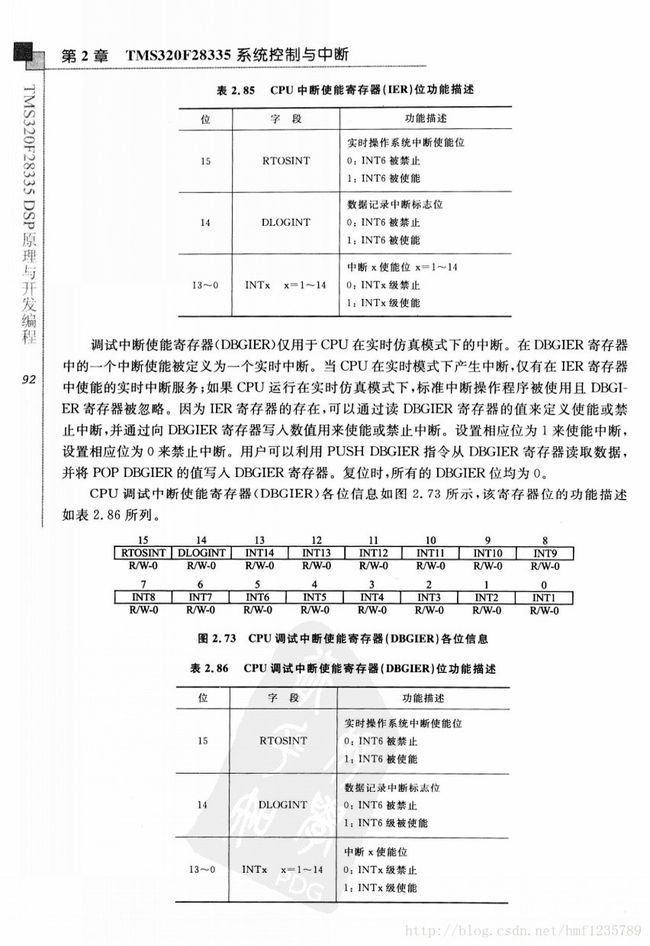

CPU也有标志寄存器IFR和使能寄存器IER。当某一个外设中断请求通过PIE发送到CPU时,CPU级中与INTx相关的中断标志位就会被置位。例如,T1的周期中断T1PINT的请求到达CPU这边时,与其相关的INT2的标志位就会被置位。这时候,该标志位就会被所存在IFR中,这时候,CPU不会马上去执行相应的中断,而是等待CPU使能IER寄存器的相关位,并且对CPU寄存器ST1中的全局中断屏蔽位做适当的使能。如果IER中的相关位被置位了,并且INTM的值为0,则中断就会被CPU响应。在T1PINT里,当IER的第2位即INT2被置位,INTM为0,则CPU就会响应定时器T1的周期中断。 CPU接到了终端的请求,就得暂停正在执行的程序,转而去响应中断程序,但是此时,它必须得做一些准备工作,以便于执行完中断程序之后回过头来还能找到原来的地方和原来的状态。CPU会将相应的IER和IFR位进行清除,EALLOW也被清除,INTM被置位,就是不能响应其他中断了,CPU向其他中断发出了通知,正在忙,没空来处理你们的请求了,得等到处理完手上的中断之后才能再来处理你们的请求。然后,CPU会存储返回地址并自动保存相关的信息,例如将正在处理的数据放入堆栈等等,做好这些准备工作之后,CPU会从PIE块中取出对应的中断向量ISR,从而转去执行中断子程序。

小结:

CPU级的操作都是自动的,不管是中断标志位(IFR),还是中断的使能位(IER)。

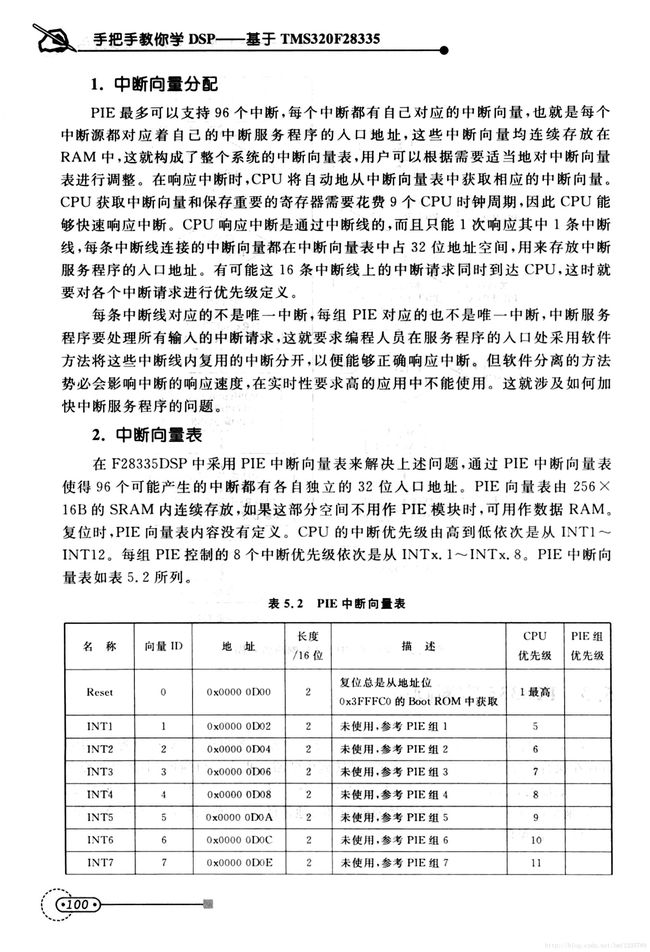

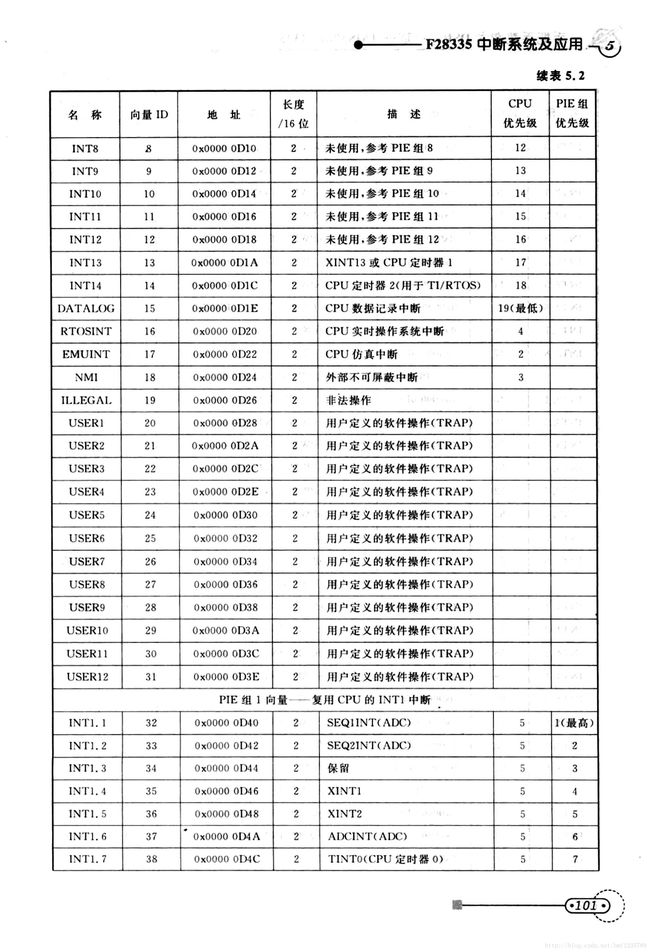

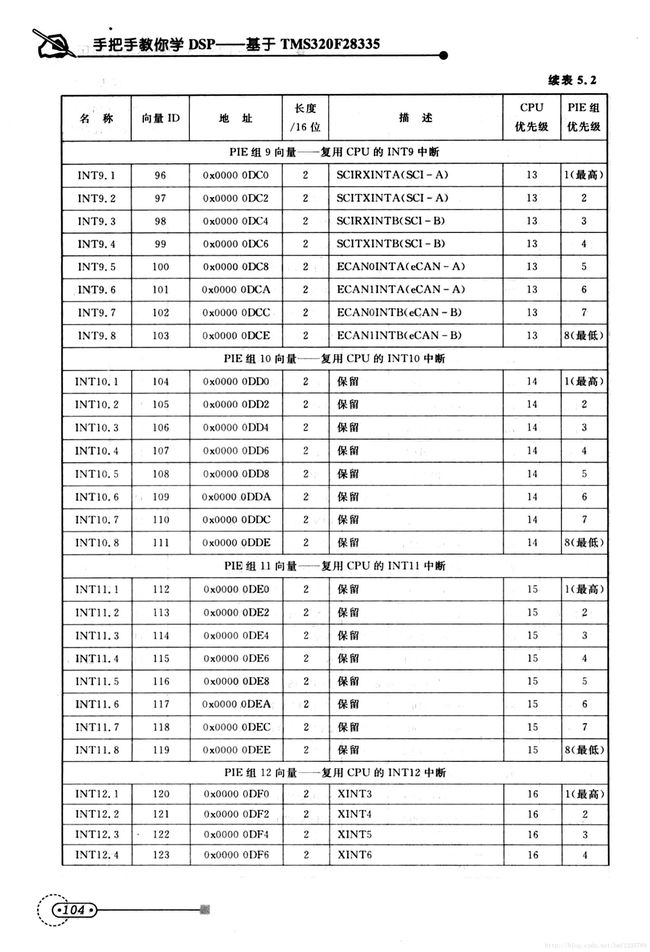

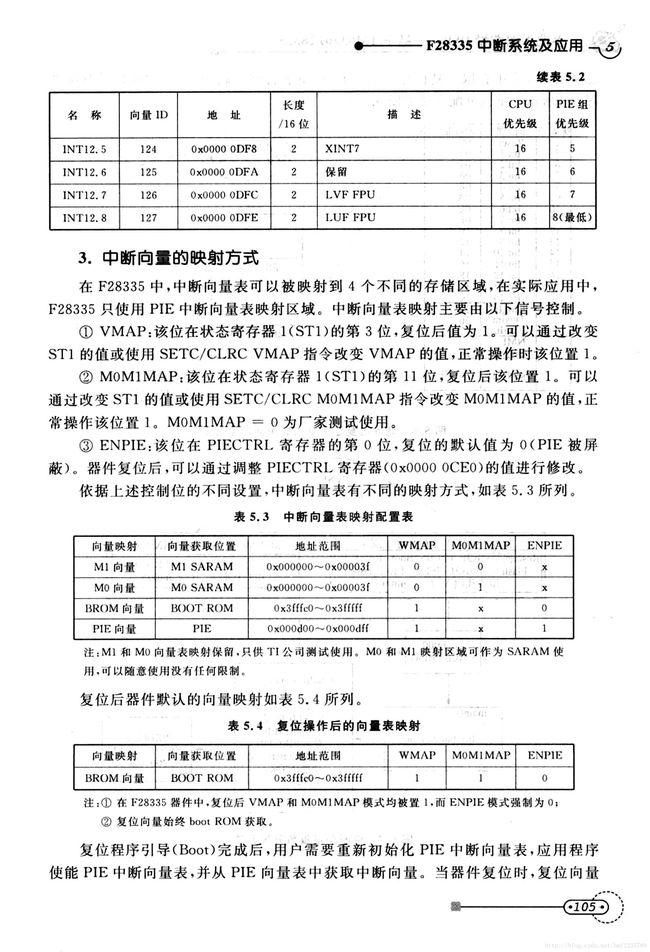

PIE级的中断向量表如下:

根据以上中断系统原理总结出配置中断的步骤为:

1、设置相应GPIO功能,使用模块中断还是外部中断。

2、开启模块系统时钟。

3、初始化模块配置,开启外设使能。(查询法)

4、打开相应PIE中断使能位。

5、使能相应的CPU中断位。

6、将中断函数配置到中断向量表。(中断法)

7、编写中断函数,PIE中断标志位清零。- PIE头文件DSP2833x_PieCtrl.h程序如下:

// TI File $Revision: /main/1 $

// Checkin $Date: August 18, 2006 13:52:24 $

//###########################################################################

//

// FILE: DSP2833x_PieCtrl.h

//

// TITLE: DSP2833x Device PIE 控制寄存器定义.

//

//###########################################################################

// $TI Release: DSP2833x/DSP2823x C/C++ Header Files V1.31 $

// $Release Date: August 4, 2009 $

//###########################################################################

#ifndef DSP2833x_PIE_CTRL_H

#define DSP2833x_PIE_CTRL_H

#ifdef __cplusplus

extern "C" {

#endif

//---------------------------------------------------------------------------

// PIE 控制寄存器定义:

//

// PIECTRL: 控制寄存器位定义:

struct PIECTRL_BITS { // bits 描述

Uint16 ENPIE:1; // 0 PIE向量表使能位

Uint16 PIEVECT:15; // 15:1 PIE中断向量

};

union PIECTRL_REG {

Uint16 all;

struct PIECTRL_BITS bit; //PIECTRL: 控制寄存器

};

// PIEIER: 中断使能寄存器位定义:

struct PIEIER_BITS { // bits 描述

Uint16 INTx1:1; // 0 INTx.1

Uint16 INTx2:1; // 1 INTx.2

Uint16 INTx3:1; // 2 INTx.3

Uint16 INTx4:1; // 3 INTx.4

Uint16 INTx5:1; // 4 INTx.5

Uint16 INTx6:1; // 5 INTx.6

Uint16 INTx7:1; // 6 INTx.7

Uint16 INTx8:1; // 7 INTx.8

Uint16 rsvd:8; // 15:8 保留

};

union PIEIER_REG {

Uint16 all;

struct PIEIER_BITS bit; //PIEIER: 中断使能寄存器

};

// PIEIFR: 中断标志寄存器位定义:

struct PIEIFR_BITS { // bits 描述

Uint16 INTx1:1; // 0 INTx.1

Uint16 INTx2:1; // 1 INTx.2

Uint16 INTx3:1; // 2 INTx.3

Uint16 INTx4:1; // 3 INTx.4

Uint16 INTx5:1; // 4 INTx.5

Uint16 INTx6:1; // 5 INTx.6

Uint16 INTx7:1; // 6 INTx.7

Uint16 INTx8:1; // 7 INTx.8

Uint16 rsvd:8; // 15:8 保留

};

union PIEIFR_REG {

Uint16 all;

struct PIEIFR_BITS bit; //PIEIFR: 中断标志寄存器

};

// PIEACK: 中断应答寄存器位定义:

struct PIEACK_BITS { // bits 描述

Uint16 ACK1:1; // 0 CPU响应PIE中断 1

Uint16 ACK2:1; // 1 CPU响应PIE中断 2

Uint16 ACK3:1; // 2 CPU响应PIE中断 3

Uint16 ACK4:1; // 3 CPU响应PIE中断 4

Uint16 ACK5:1; // 4 CPU响应PIE中断 5

Uint16 ACK6:1; // 5 CPU响应PIE中断 6

Uint16 ACK7:1; // 6 CPU响应PIE中断 7

Uint16 ACK8:1; // 7 CPU响应PIE中断 8

Uint16 ACK9:1; // 8 CPU响应PIE中断 9

Uint16 ACK10:1; // 9 CPU响应PIE中断 10

Uint16 ACK11:1; // 10 CPU响应PIE中断 11

Uint16 ACK12:1; // 11 CPU响应PIE中断 12

Uint16 rsvd:4; // 15:12 保留

};

union PIEACK_REG {

Uint16 all;

struct PIEACK_BITS bit; //PIEACK: 中断应答寄存器

};

//---------------------------------------------------------------------------

// PIE 控制寄存器文件:

//

struct PIE_CTRL_REGS {

union PIECTRL_REG PIECTRL; // PIE 控制寄存器

union PIEACK_REG PIEACK; // PIE 应答寄存器

union PIEIER_REG PIEIER1; // PIE int1 IER 中断使能寄存器

union PIEIFR_REG PIEIFR1; // PIE int1 IFR 中断标志寄存器

union PIEIER_REG PIEIER2; // PIE INT2 IER 中断使能寄存器

union PIEIFR_REG PIEIFR2; // PIE INT2 IFR 中断标志寄存器

union PIEIER_REG PIEIER3; // PIE INT3 IER 中断使能寄存器

union PIEIFR_REG PIEIFR3; // PIE INT3 IFR 中断标志寄存器

union PIEIER_REG PIEIER4; // PIE INT4 IER 中断使能寄存器

union PIEIFR_REG PIEIFR4; // PIE INT4 IFR 中断标志寄存器

union PIEIER_REG PIEIER5; // PIE INT5 IER 中断使能寄存器

union PIEIFR_REG PIEIFR5; // PIE INT5 IFR 中断标志寄存器

union PIEIER_REG PIEIER6; // PIE INT6 IER 中断使能寄存器

union PIEIFR_REG PIEIFR6; // PIE INT6 IFR 中断标志寄存器

union PIEIER_REG PIEIER7; // PIE INT7 IER 中断使能寄存器

union PIEIFR_REG PIEIFR7; // PIE INT7 IFR 中断标志寄存器

union PIEIER_REG PIEIER8; // PIE INT8 IER 中断使能寄存器

union PIEIFR_REG PIEIFR8; // PIE INT8 IFR 中断标志寄存器

union PIEIER_REG PIEIER9; // PIE INT9 IER 中断使能寄存器

union PIEIFR_REG PIEIFR9; // PIE INT9 IFR 中断标志寄存器

union PIEIER_REG PIEIER10; // PIE int10 IER 中断使能寄存器

union PIEIFR_REG PIEIFR10; // PIE int10 IFR 中断标志寄存器

union PIEIER_REG PIEIER11; // PIE int11 IER 中断使能寄存器

union PIEIFR_REG PIEIFR11; // PIE int11 IFR 中断标志寄存器

union PIEIER_REG PIEIER12; // PIE int12 IER 中断使能寄存器

union PIEIFR_REG PIEIFR12; // PIE int12 IFR 中断标志寄存器

};

#define PIEACK_GROUP1 0x0001 //PIE中断应答清零 1

#define PIEACK_GROUP2 0x0002 //PIE中断应答清零 2

#define PIEACK_GROUP3 0x0004 //PIE中断应答清零 3

#define PIEACK_GROUP4 0x0008 //PIE中断应答清零 4

#define PIEACK_GROUP5 0x0010 //PIE中断应答清零 5

#define PIEACK_GROUP6 0x0020 //PIE中断应答清零 6

#define PIEACK_GROUP7 0x0040 //PIE中断应答清零 7

#define PIEACK_GROUP8 0x0080 //PIE中断应答清零 8

#define PIEACK_GROUP9 0x0100 //PIE中断应答清零 9

#define PIEACK_GROUP10 0x0200 //PIE中断应答清零 10

#define PIEACK_GROUP11 0x0400 //PIE中断应答清零 11

#define PIEACK_GROUP12 0x0800 //PIE中断应答清零 12

//---------------------------------------------------------------------------

// PIE 控制寄存器外部引用 & 函数声明:

//

extern volatile struct PIE_CTRL_REGS PieCtrlRegs;

#ifdef __cplusplus

}

#endif /* extern "C" */

#endif // end of DSP2833x_PIE_CTRL_H definition

//===========================================================================

// End of file.

//===========================================================================

- 默认PIE控制文件DSP2833x_PieCtrl.c程序如下:

// TI File $Revision: /main/1 $

// Checkin $Date: August 18, 2006 13:46:35 $

//###########################################################################

//

// FILE: DSP2833x_PieCtrl.c

//

// TITLE: DSP2833x Device PIE 控制寄存器初始化函数.

//

//###########################################################################

// $TI Release: DSP2833x/DSP2823x C/C++ Header Files V1.31 $

// $Release Date: August 4, 2009 $

//###########################################################################

//---------------------------------------------------------------------------

// InitPieCtrl:

//---------------------------------------------------------------------------

// 改函数将PIE控制寄存器初始化到一个已知状态.

//

void InitPieCtrl(void)

{

//初始化PIE

DINT;

// 禁止PIE模块

PieCtrlRegs.PIECTRL.bit.ENPIE = 0;

//PIEIER中断使能寄存器清零

PieCtrlRegs.PIEIER1.all = 0;

PieCtrlRegs.PIEIER2.all = 0;

PieCtrlRegs.PIEIER3.all = 0;

PieCtrlRegs.PIEIER4.all = 0;

PieCtrlRegs.PIEIER5.all = 0;

PieCtrlRegs.PIEIER6.all = 0;

PieCtrlRegs.PIEIER7.all = 0;

PieCtrlRegs.PIEIER8.all = 0;

PieCtrlRegs.PIEIER9.all = 0;

PieCtrlRegs.PIEIER10.all = 0;

PieCtrlRegs.PIEIER11.all = 0;

PieCtrlRegs.PIEIER12.all = 0;

//PIEIFR中断标志寄存器清零

PieCtrlRegs.PIEIFR1.all = 0;

PieCtrlRegs.PIEIFR2.all = 0;

PieCtrlRegs.PIEIFR3.all = 0;

PieCtrlRegs.PIEIFR4.all = 0;

PieCtrlRegs.PIEIFR5.all = 0;

PieCtrlRegs.PIEIFR6.all = 0;

PieCtrlRegs.PIEIFR7.all = 0;

PieCtrlRegs.PIEIFR8.all = 0;

PieCtrlRegs.PIEIFR9.all = 0;

PieCtrlRegs.PIEIFR10.all = 0;

PieCtrlRegs.PIEIFR11.all = 0;

PieCtrlRegs.PIEIFR12.all = 0;

}

//设置PIE控制寄存器

void SetPieCtrl(void)

{

//设置PIE

DINT;

//使能PIE

EnableInterrupts();

//PIEIER中断使能寄存器清零

PieCtrlRegs.PIEIER1.all = (M_INT4 | M_INT7);

//使能XINT1, Timer0中断寄存器

PieCtrlRegs.PIEIER2.all = 0;

PieCtrlRegs.PIEIER3.bit.INTx1 = 1; //使能ePWM1中断寄存器 M_INT1

PieCtrlRegs.PIEIER4.all = 0;

PieCtrlRegs.PIEIER5.all = 0;

PieCtrlRegs.PIEIER6.all = 0;

PieCtrlRegs.PIEIER7.all = 0;

PieCtrlRegs.PIEIER8.all = 0;

PieCtrlRegs.PIEIER9.all = (M_INT1 | M_INT2);

//使能SCIRXINTA, SCITXINTA中断寄存器

PieCtrlRegs.PIEIER10.all = 0;

PieCtrlRegs.PIEIER11.all = 0;

PieCtrlRegs.PIEIER12.all = 0;

//PIEIFR中断标志寄存器清零

PieCtrlRegs.PIEIFR1.all = 0;

PieCtrlRegs.PIEIFR2.all = 0;

PieCtrlRegs.PIEIFR3.all = 0;

PieCtrlRegs.PIEIFR4.all = 0;

PieCtrlRegs.PIEIFR5.all = 0;

PieCtrlRegs.PIEIFR6.all = 0;

PieCtrlRegs.PIEIFR7.all = 0;

PieCtrlRegs.PIEIFR8.all = 0;

PieCtrlRegs.PIEIFR9.all = 0;

PieCtrlRegs.PIEIFR10.all = 0;

PieCtrlRegs.PIEIFR11.all = 0;

PieCtrlRegs.PIEIFR12.all = 0;

}

//使能PIE

void EnableInterrupts()

{

//使能PIE向量表

PieCtrlRegs.PIECTRL.bit.ENPIE = 1;

//中断应答寄存器清零

PieCtrlRegs.PIEACK.all = 0xFFFF;

EINT;

}

//===========================================================================

// End of file.

//===========================================================================

- 默认中断头文件DSP2833x_DefaultIsr.h程序如下:

// TI File $Revision: /main/1 $

// Checkin $Date: August 18, 2006 13:45:37 $

//###########################################################################

//

// FILE: DSP2833x_DefaultIsr.h

//

// TITLE: DSP2833x Devices 默认的中断服务例程定义.

//

//###########################################################################

// $TI Release: DSP2833x/DSP2823x C/C++ Header Files V1.31 $

// $Release Date: August 4, 2009 $

//###########################################################################

#ifndef DSP2833x_DEFAULT_ISR_H

#define DSP2833x_DEFAULT_ISR_H

#ifdef __cplusplus

extern "C" {

#endif

//---------------------------------------------------------------------------

// 默认中断服务程序声明:

//

// 下面的函数原型

// 默认的ISR例程使用默认的中断向量表

// 这个默认的中断向量表在DSP2833x_PieVect.h中

// 文件

//

// 非外部中断:

// Group 0 PIE 中断服务程序:

interrupt void INT13_ISR(void); // XINT13 or CPU-Timer 1

interrupt void INT14_ISR(void); // CPU-Timer2

interrupt void DATALOG_ISR(void); // Datalogging interrupt

interrupt void RTOSINT_ISR(void); // RTOS interrupt

interrupt void EMUINT_ISR(void); // Emulation interrupt

interrupt void NMI_ISR(void); // Non-maskable interrupt

interrupt void ILLEGAL_ISR(void); // Illegal operation TRAP

interrupt void USER1_ISR(void); // User Defined trap 1

interrupt void USER2_ISR(void); // User Defined trap 2

interrupt void USER3_ISR(void); // User Defined trap 3

interrupt void USER4_ISR(void); // User Defined trap 4

interrupt void USER5_ISR(void); // User Defined trap 5

interrupt void USER6_ISR(void); // User Defined trap 6

interrupt void USER7_ISR(void); // User Defined trap 7

interrupt void USER8_ISR(void); // User Defined trap 8

interrupt void USER9_ISR(void); // User Defined trap 9

interrupt void USER10_ISR(void); // User Defined trap 10

interrupt void USER11_ISR(void); // User Defined trap 11

interrupt void USER12_ISR(void); // User Defined trap 12

// Group 1 PIE 中断服务程序:

interrupt void SEQ1INT_ISR(void); // ADC Sequencer 1 ISR

interrupt void SEQ2INT_ISR(void); // ADC Sequencer 2 ISR

interrupt void XINT1_ISR(void); // External interrupt 1

interrupt void XINT2_ISR(void); // External interrupt 2

interrupt void ADCINT_ISR(void); // ADC

interrupt void TINT0_ISR(void); // Timer 0

interrupt void WAKEINT_ISR(void); // WD

// Group 2 PIE 中断服务程序:

interrupt void EPWM1_TZINT_ISR(void); // EPWM-1

interrupt void EPWM2_TZINT_ISR(void); // EPWM-2

interrupt void EPWM3_TZINT_ISR(void); // EPWM-3

interrupt void EPWM4_TZINT_ISR(void); // EPWM-4

interrupt void EPWM5_TZINT_ISR(void); // EPWM-5

interrupt void EPWM6_TZINT_ISR(void); // EPWM-6

// Group 3 PIE 中断服务程序:

interrupt void EPWM1_INT_ISR(void); // EPWM-1

interrupt void EPWM2_INT_ISR(void); // EPWM-2

interrupt void EPWM3_INT_ISR(void); // EPWM-3

interrupt void EPWM4_INT_ISR(void); // EPWM-4

interrupt void EPWM5_INT_ISR(void); // EPWM-5

interrupt void EPWM6_INT_ISR(void); // EPWM-6

// Group 4 PIE 中断服务程序:

interrupt void ECAP1_INT_ISR(void); // ECAP-1

interrupt void ECAP2_INT_ISR(void); // ECAP-2

interrupt void ECAP3_INT_ISR(void); // ECAP-3

interrupt void ECAP4_INT_ISR(void); // ECAP-4

interrupt void ECAP5_INT_ISR(void); // ECAP-5

interrupt void ECAP6_INT_ISR(void); // ECAP-6

// Group 5 PIE 中断服务程序:

interrupt void EQEP1_INT_ISR(void); // EQEP-1

interrupt void EQEP2_INT_ISR(void); // EQEP-2

// Group 6 PIE 中断服务程序:

interrupt void SPIRXINTA_ISR(void); // SPI-A

interrupt void SPITXINTA_ISR(void); // SPI-A

interrupt void MRINTA_ISR(void); // McBSP-A

interrupt void MXINTA_ISR(void); // McBSP-A

interrupt void MRINTB_ISR(void); // McBSP-B

interrupt void MXINTB_ISR(void); // McBSP-B

// Group 7 PIE 中断服务程序:

interrupt void DINTCH1_ISR(void); // DMA-Channel 1

interrupt void DINTCH2_ISR(void); // DMA-Channel 2

interrupt void DINTCH3_ISR(void); // DMA-Channel 3

interrupt void DINTCH4_ISR(void); // DMA-Channel 4

interrupt void DINTCH5_ISR(void); // DMA-Channel 5

interrupt void DINTCH6_ISR(void); // DMA-Channel 6

// Group 8 PIE 中断服务程序:

interrupt void I2CINT1A_ISR(void); // I2C-A

interrupt void I2CINT2A_ISR(void); // I2C-A

interrupt void SCIRXINTC_ISR(void); // SCI-C

interrupt void SCITXINTC_ISR(void); // SCI-C

// Group 9 PIE 中断服务程序:

interrupt void SCIRXINTA_ISR(void); // SCI-A

interrupt void SCITXINTA_ISR(void); // SCI-A

interrupt void SCIRXINTB_ISR(void); // SCI-B

interrupt void SCITXINTB_ISR(void); // SCI-B

interrupt void ECAN0INTA_ISR(void); // eCAN-A

interrupt void ECAN1INTA_ISR(void); // eCAN-A

interrupt void ECAN0INTB_ISR(void); // eCAN-B

interrupt void ECAN1INTB_ISR(void); // eCAN-B

// Group 10 PIE 中断服务程序:

// Group 11 PIE 中断服务程序:

// Group 12 PIE 中断服务程序:

interrupt void XINT3_ISR(void); // External interrupt 3

interrupt void XINT4_ISR(void); // External interrupt 4

interrupt void XINT5_ISR(void); // External interrupt 5

interrupt void XINT6_ISR(void); // External interrupt 6

interrupt void XINT7_ISR(void); // External interrupt 7

interrupt void LVF_ISR(void); // Latched overflow flag

interrupt void LUF_ISR(void); // Latched underflow flag

// 全方位为测试保留位置:

interrupt void PIE_RESERVED(void); // Reserved for test

interrupt void rsvd_ISR(void); // for test

interrupt void INT_NOTUSED_ISR(void); // for unused interrupts

#ifdef __cplusplus

}

#endif /* extern "C" */

#endif // end of DSP2833x_DEFAULT_ISR_H definition

//===========================================================================

// End of file.

//===========================================================================

- 默认中断向量表配置文件DSP2833x_PieVect.c程序如下:

// TI File $Revision: /main/1 $

// Checkin $Date: August 18, 2006 13:46:38 $

//###########################################################################

//

// FILE: DSP2833x_PieVect.c

//

// TITLE: DSP2833x Devices PIE 向量表初始化函数.

//

//###########################################################################

// $TI Release: DSP2833x/DSP2823x C/C++ Header Files V1.31 $

// $Release Date: August 4, 2009 $

//###########################################################################

//定义一个结构体类型PIE_VECT_TABLE的结构体变量PieVectTableInit,并给元素赋初

//值,其元素初值为其对应的默认中断向量服务程序的起始地址(函数名)

//在DSP281x_DefaultIsr.c里面都有定义

#include "DSP2833x_Device.h" // DSP2833x Headerfile Include File

#include "DSP2833x_Examples.h" // DSP2833x Examples Include File

const struct PIE_VECT_TABLE PieVectTableInit = {

PIE_RESERVED, // 0 Reserved space

PIE_RESERVED, // 1 Reserved space

PIE_RESERVED, // 2 Reserved space

PIE_RESERVED, // 3 Reserved space

PIE_RESERVED, // 4 Reserved space

PIE_RESERVED, // 5 Reserved space

PIE_RESERVED, // 6 Reserved space

PIE_RESERVED, // 7 Reserved space

PIE_RESERVED, // 8 Reserved space

PIE_RESERVED, // 9 Reserved space

PIE_RESERVED, // 10 Reserved space

PIE_RESERVED, // 11 Reserved space

PIE_RESERVED, // 12 Reserved space

//非外部中断

INT13_ISR, // XINT13 or CPU-Timer 1

INT14_ISR, // CPU-Timer2

DATALOG_ISR, // Datalogging interrupt

RTOSINT_ISR, // RTOS interrupt

EMUINT_ISR, // Emulation interrupt

NMI_ISR, // Non-maskable interrupt

ILLEGAL_ISR, // Illegal operation TRAP

USER1_ISR, // User Defined trap 1

USER2_ISR, // User Defined trap 2

USER3_ISR, // User Defined trap 3

USER4_ISR, // User Defined trap 4

USER5_ISR, // User Defined trap 5

USER6_ISR, // User Defined trap 6

USER7_ISR, // User Defined trap 7

USER8_ISR, // User Defined trap 8

USER9_ISR, // User Defined trap 9

USER10_ISR, // User Defined trap 10

USER11_ISR, // User Defined trap 11

USER12_ISR, // User Defined trap 12

//第1组向量表

SEQ1INT_ISR, // 1.1 ADC

SEQ2INT_ISR, // 1.2 ADC

rsvd_ISR, // 1.3

XINT1_ISR, // 1.4

XINT2_ISR, // 1.5

ADCINT_ISR, // 1.6 ADC

TINT0_ISR, // 1.7 Timer 0

WAKEINT_ISR, // 1.8 WD, Low Power

//第2组向量表

EPWM1_TZINT_ISR, // 2.1 EPWM-1 Trip Zone

EPWM2_TZINT_ISR, // 2.2 EPWM-2 Trip Zone

EPWM3_TZINT_ISR, // 2.3 EPWM-3 Trip Zone

EPWM4_TZINT_ISR, // 2.4 EPWM-4 Trip Zone

EPWM5_TZINT_ISR, // 2.5 EPWM-5 Trip Zone

EPWM6_TZINT_ISR, // 2.6 EPWM-6 Trip Zone

rsvd_ISR, // 2.7

rsvd_ISR, // 2.8

//第3组向量表

EPWM1_INT_ISR, // 3.1 EPWM-1 Interrupt

EPWM2_INT_ISR, // 3.2 EPWM-2 Interrupt

EPWM3_INT_ISR, // 3.3 EPWM-3 Interrupt

EPWM4_INT_ISR, // 3.4 EPWM-4 Interrupt

EPWM5_INT_ISR, // 3.5 EPWM-5 Interrupt

EPWM6_INT_ISR, // 3.6 EPWM-6 Interrupt

rsvd_ISR, // 3.7

rsvd_ISR, // 3.8

//第4组向量表

ECAP1_INT_ISR, // 4.1 ECAP-1

ECAP2_INT_ISR, // 4.2 ECAP-2

ECAP3_INT_ISR, // 4.3 ECAP-3

ECAP4_INT_ISR, // 4.4 ECAP-4

ECAP5_INT_ISR, // 4.5 ECAP-5

ECAP6_INT_ISR, // 4.6 ECAP-6

rsvd_ISR, // 4.7

rsvd_ISR, // 4.8

//第5组向量表

EQEP1_INT_ISR, // 5.1 EQEP-1

EQEP2_INT_ISR, // 5.2 EQEP-2

rsvd_ISR, // 5.3

rsvd_ISR, // 5.4

rsvd_ISR, // 5.5

rsvd_ISR, // 5.6

rsvd_ISR, // 5.7

rsvd_ISR, // 5.8

//第6组向量表

SPIRXINTA_ISR, // 6.1 SPI-A

SPITXINTA_ISR, // 6.2 SPI-A

MRINTA_ISR, // 6.3 McBSP-A

MXINTA_ISR, // 6.4 McBSP-A

MRINTB_ISR, // 6.5 McBSP-B

MXINTB_ISR, // 6.6 McBSP-B

rsvd_ISR, // 6.7

rsvd_ISR, // 6.8

//第7组向量表

DINTCH1_ISR, // 7.1 DMA channel 1

DINTCH2_ISR, // 7.2 DMA channel 2

DINTCH3_ISR, // 7.3 DMA channel 3

DINTCH4_ISR, // 7.4 DMA channel 4

DINTCH5_ISR, // 7.5 DMA channel 5

DINTCH6_ISR, // 7.6 DMA channel 6

rsvd_ISR, // 7.7

rsvd_ISR, // 7.8

//第8组向量表

I2CINT1A_ISR, // 8.1 I2C

I2CINT2A_ISR, // 8.2 I2C

rsvd_ISR, // 8.3

rsvd_ISR, // 8.4

SCIRXINTC_ISR, // 8.5 SCI-C

SCITXINTC_ISR, // 8.6 SCI-C

rsvd_ISR, // 8.7

rsvd_ISR, // 8.8

//第9组向量表

SCIRXINTA_ISR, // 9.1 SCI-A

SCITXINTA_ISR, // 9.2 SCI-A

SCIRXINTB_ISR, // 9.3 SCI-B

SCITXINTB_ISR, // 9.4 SCI-B

ECAN0INTA_ISR, // 9.5 eCAN-A

ECAN1INTA_ISR, // 9.6 eCAN-A

ECAN0INTB_ISR, // 9.7 eCAN-B

ECAN1INTB_ISR, // 9.8 eCAN-B

//第10组向量表

rsvd_ISR, // 10.1

rsvd_ISR, // 10.2

rsvd_ISR, // 10.3

rsvd_ISR, // 10.4

rsvd_ISR, // 10.5

rsvd_ISR, // 10.6

rsvd_ISR, // 10.7

rsvd_ISR, // 10.8

//第11组向量表

rsvd_ISR, // 11.1

rsvd_ISR, // 11.2

rsvd_ISR, // 11.3

rsvd_ISR, // 11.4

rsvd_ISR, // 11.5

rsvd_ISR, // 11.6

rsvd_ISR, // 11.7

rsvd_ISR, // 11.8

//第12组向量表

XINT3_ISR, // 12.1

XINT4_ISR, // 12.2

XINT5_ISR, // 12.3

XINT6_ISR, // 12.4

XINT7_ISR, // 12.5

rsvd_ISR, // 12.6

LVF_ISR, // 12.7

LUF_ISR, // 12.8

};

//初始化PIE中断向量表

//这个子程序把PIE中断向量表初始化到一个已知状态,这个子程序必须在引导程序后执行

void InitPieVectTable(void)

{

int16 i;

Uint32 *Source = (void *) &PieVectTableInit;

Uint32 *Dest = (void *) &PieVectTable;

//将结构体变量PieVectTableInit的值赋给结构体变量PieVectTable

//注意:两个为同一个结构体类型PIE_VECT_TABLE

EALLOW;

for(i=0; i < 128; i++)

*Dest++ = *Source++; //中断服务程序映射到中断向量表中

EDIS;

//使能PIE中断向量表

PieCtrlRegs.PIECTRL.bit.ENPIE = 1;

}

//===========================================================================

// End of file.

//===========================================================================

- 默认中断配置函数DSP2833x_DefaultIsr.c文件程序如下:

// TI File $Revision: /main/1 $

// Checkin $Date: August 18, 2006 13:46:06 $

//###########################################################################

//

// FILE: DSP2833x_DefaultIsr.c

//

// TITLE: DSP2833x Device 默认中断服务例程.

//

// This file contains shell ISR routines for the 2833x PIE vector table.

// Typically these shell ISR routines can be used to populate the entire PIE

// vector table during device debug. In this manner if an interrupt is taken

// during firmware development, there will always be an ISR to catch it.

//

// As develpment progresses, these ISR rotuines can be eliminated and replaced

// with the user's own ISR routines for each interrupt. Since these shell ISRs

// include infinite loops they will typically not be included as-is in the final

// production firmware.

//

//###########################################################################

// $TI Release: DSP2833x Header Files V1.01 $

// $Release Date: September 26, 2007 $

//###########################################################################

#include "DSP2833x_Device.h" // DSP2833x Headerfile Include File

#include "DSP2833x_Examples.h" // DSP2833x Examples Include File

// Connected to INT13 of CPU (use MINT13 mask):

// Note CPU-Timer1 is reserved for TI use, however XINT13

// ISR can be used by the user.

interrupt void INT13_ISR(void) // INT13 or CPU-Timer1

{

// ISR代码插入这里

// 下两行仅供调试处理器时使用

// 插入ISR代码后删除

asm (" ESTOP0");

for(;;);

}

// Note CPU-Timer2 is reserved for TI use.

interrupt void INT14_ISR(void) // CPU-Timer2

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void DATALOG_ISR(void) // Datalogging interrupt

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void RTOSINT_ISR(void) // RTOS interrupt

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void EMUINT_ISR(void) // Emulation interrupt

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void NMI_ISR(void) // Non-maskable interrupt

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void ILLEGAL_ISR(void) // Illegal operation TRAP

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm(" ESTOP0");

for(;;);

}

interrupt void USER1_ISR(void) // User Defined trap 1

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER2_ISR(void) // User Defined trap 2

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER3_ISR(void) // User Defined trap 3

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER4_ISR(void) // User Defined trap 4

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER5_ISR(void) // User Defined trap 5

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER6_ISR(void) // User Defined trap 6

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER7_ISR(void) // User Defined trap 7

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER8_ISR(void) // User Defined trap 8

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER9_ISR(void) // User Defined trap 9

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER10_ISR(void) // User Defined trap 10

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER11_ISR(void) // User Defined trap 11

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

interrupt void USER12_ISR(void) // User Defined trap 12

{

// Insert ISR Code here

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// -----------------------------------------------------------

// PIE Group 1 - MUXed into CPU INT1

// -----------------------------------------------------------

// INT1.1

interrupt void SEQ1INT_ISR(void) //SEQ1 ADC

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT1.2

interrupt void SEQ2INT_ISR(void) //SEQ2 ADC

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm(" ESTOP0");

for(;;);

}

// INT1.3 - Reserved

// INT1.4

interrupt void XINT1_ISR(void)

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT1.5

interrupt void XINT2_ISR(void)

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT1.6

interrupt void ADCINT_ISR(void) // ADC

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT1.7

interrupt void TINT0_ISR(void) // CPU-Timer 0

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT1.8

interrupt void WAKEINT_ISR(void) // WD, LOW Power

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// -----------------------------------------------------------

// PIE Group 2 - MUXed into CPU INT2

// -----------------------------------------------------------

// INT2.1

interrupt void EPWM1_TZINT_ISR(void) // EPWM-1

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT2.2

interrupt void EPWM2_TZINT_ISR(void) // EPWM-2

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT2.3

interrupt void EPWM3_TZINT_ISR(void) // EPWM-3

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT2.4

interrupt void EPWM4_TZINT_ISR(void) // EPWM-4

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT2.5

interrupt void EPWM5_TZINT_ISR(void) // EPWM-5

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT2.6

interrupt void EPWM6_TZINT_ISR(void) // EPWM-6

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT2.7 - Reserved

// INT2.8 - Reserved

// -----------------------------------------------------------

// PIE Group 3 - MUXed into CPU INT3

// -----------------------------------------------------------

// INT 3.1

interrupt void EPWM1_INT_ISR(void) // EPWM-1

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT3.2

interrupt void EPWM2_INT_ISR(void) // EPWM-2

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT3.3

interrupt void EPWM3_INT_ISR(void) // EPWM-3

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT3.4

interrupt void EPWM4_INT_ISR(void) // EPWM-4

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT3.5

interrupt void EPWM5_INT_ISR(void) // EPWM-5

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT3.6

interrupt void EPWM6_INT_ISR(void) // EPWM-6

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT3.7 - Reserved

// INT3.8 - Reserved

// -----------------------------------------------------------

// PIE Group 4 - MUXed into CPU INT4

// -----------------------------------------------------------

// INT 4.1

interrupt void ECAP1_INT_ISR(void) // ECAP-1

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT4.2

interrupt void ECAP2_INT_ISR(void) // ECAP-2

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT4.3

interrupt void ECAP3_INT_ISR(void) // ECAP-3

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT4.4

interrupt void ECAP4_INT_ISR(void) // ECAP-4

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT4.5

interrupt void ECAP5_INT_ISR(void) // ECAP-5

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT4.6

interrupt void ECAP6_INT_ISR(void) // ECAP-6

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT4.7 - Reserved

// INT4.8 - Reserved

// -----------------------------------------------------------

// PIE Group 5 - MUXed into CPU INT5

// -----------------------------------------------------------

// INT 5.1

interrupt void EQEP1_INT_ISR(void) // EQEP-1

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP5;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT5.2

interrupt void EQEP2_INT_ISR(void) // EQEP-2

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP5;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT5.3 - Reserved

// INT5.4 - Reserved

// INT5.5 - Reserved

// INT5.6 - Reserved

// INT5.7 - Reserved

// INT5.8 - Reserved

// -----------------------------------------------------------

// PIE Group 6 - MUXed into CPU INT6

// -----------------------------------------------------------

// INT6.1

interrupt void SPIRXINTA_ISR(void) // SPI-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP6;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT6.2

interrupt void SPITXINTA_ISR(void) // SPI-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP6;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT6.3

interrupt void MRINTB_ISR(void) // McBSP-B

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP6;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT6.4

interrupt void MXINTB_ISR(void) // McBSP-B

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP6;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT6.5

interrupt void MRINTA_ISR(void) // McBSP-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP6;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT6.6

interrupt void MXINTA_ISR(void) // McBSP-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP6;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT6.7 - Reserved

// INT6.8 - Reserved

// -----------------------------------------------------------

// PIE Group 7 - MUXed into CPU INT7

// -----------------------------------------------------------

// INT7.1

interrupt void DINTCH1_ISR(void) // DMA

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP7;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT7.2

interrupt void DINTCH2_ISR(void) // DMA

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP7;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT7.3

interrupt void DINTCH3_ISR(void) // DMA

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP7;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT7.4

interrupt void DINTCH4_ISR(void) // DMA

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP7;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT7.5

interrupt void DINTCH5_ISR(void) // DMA

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP7;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT7.6

interrupt void DINTCH6_ISR(void) // DMA

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP7;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT7.7 - Reserved

// INT7.8 - Reserved

// -----------------------------------------------------------

// PIE Group 8 - MUXed into CPU INT8

// -----------------------------------------------------------

// INT8.1

interrupt void I2CINT1A_ISR(void) // I2C-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP8;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT8.2

interrupt void I2CINT2A_ISR(void) // I2C-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP8;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT8.3 - Reserved

// INT8.4 - Reserved

// INT8.5

interrupt void SCIRXINTC_ISR(void) // SCI-C

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP8;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT8.6

interrupt void SCITXINTC_ISR(void) // SCI-C

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP8;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT8.7 - Reserved

// INT8.8 - Reserved

// -----------------------------------------------------------

// PIE Group 9 - MUXed into CPU INT9

// -----------------------------------------------------------

// INT9.1

interrupt void SCIRXINTA_ISR(void) // SCI-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT9.2

interrupt void SCITXINTA_ISR(void) // SCI-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT9.3

interrupt void SCIRXINTB_ISR(void) // SCI-B

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT9.4

interrupt void SCITXINTB_ISR(void) // SCI-B

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT9.5

interrupt void ECAN0INTA_ISR(void) // eCAN-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT9.6

interrupt void ECAN1INTA_ISR(void) // eCAN-A

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT9.7

interrupt void ECAN0INTB_ISR(void) // eCAN-B

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT9.8

interrupt void ECAN1INTB_ISR(void) // eCAN-B

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// -----------------------------------------------------------

// PIE Group 10 - MUXed into CPU INT10

// -----------------------------------------------------------

// INT10.1 - Reserved

// INT10.2 - Reserved

// INT10.3 - Reserved

// INT10.4 - Reserved

// INT10.5 - Reserved

// INT10.6 - Reserved

// INT10.7 - Reserved

// INT10.8 - Reserved

// -----------------------------------------------------------

// PIE Group 11 - MUXed into CPU INT11

// -----------------------------------------------------------

// INT11.1 - Reserved

// INT11.2 - Reserved

// INT11.3 - Reserved

// INT11.4 - Reserved

// INT11.5 - Reserved

// INT11.6 - Reserved

// INT11.7 - Reserved

// INT11.8 - Reserved

// -----------------------------------------------------------

// PIE Group 12 - MUXed into CPU INT12

// -----------------------------------------------------------

// INT12.1

interrupt void XINT3_ISR(void) // External Interrupt

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP12;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT12.2

interrupt void XINT4_ISR(void) // External Interrupt

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP12;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT12.3

interrupt void XINT5_ISR(void) // External Interrupt

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP12;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT12.4

interrupt void XINT6_ISR(void) // External Interrupt

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP12;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT12.5

interrupt void XINT7_ISR(void) // External Interrupt

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP12;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT12.6 - Reserved

// INT12.7

interrupt void LVF_ISR(void) // Latched overflow

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP12;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

// INT12.8

interrupt void LUF_ISR(void) // Latched underflow

{

// Insert ISR Code here

// To receive more interrupts from this PIE group, acknowledge this interrupt

// PieCtrlRegs.PIEACK.all = PIEACK_GROUP12;

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

asm (" ESTOP0");

for(;;);

}

//---------------------------------------------------------------------------

// Catch All Default ISRs:

//

interrupt void EMPTY_ISR(void) // Empty ISR - only does a return.

{

}

interrupt void PIE_RESERVED(void) // Reserved space. For test.

{

asm (" ESTOP0");

for(;;);

}

interrupt void rsvd_ISR(void) // For test

{

asm (" ESTOP0");

for(;;);

}

//===========================================================================

// End of file.

//===========================================================================

- 参考资料

《手把手教你学DSP:基于TMS320F28》

《TMS320F28335DSP原理与开发编程》

TMS320F28335中断总结

DSP的外围中断PIE学习

有关DSP281x_defaultIsr文件