ARM7体系结构

ARM7体系结构

之前有提到嵌入式系统的目标就是将计算机芯片化,集成为单片微型计算机,满足对象体系的控制要求。为了实现这一轻便的性能,提供更大的灵活性和更高的智能化,ARM内核采用精简指令集计算机体系结构——RISC,它的逻辑简单,指令集少。

这里有必要说一下RISC结构体系的特征:

- 具有大量的通用寄存器

- 通过装载/保存结构使用独立的load和store指令,完成数据在寄存器和外部存储器之间的传送。其中需要说明的是,处理器只处理寄存器中的数据。这样可以加快访问速度,因为不必每次访问存储器。

ARM体系结构还有如下特征:

- load/store进行批量数据传输,实现最大数据吞吐量。

- 每条数据指令可以同时包含算数逻辑单元ALU的运算和移位处理。地址自动增加,自动减少的寻址方式,优化程序中的循环处理。

- 大多数ARM指令是条件执行的。

RISC的缺点:

功能少

ARM处理器的系列:

M:微控制处理器

成本低,体积小,引脚数目少,Cortex-M3采用纯Thumb2指令执行方式,32位高性能ARM内核能够实现8位和16位处理器级数的代码存储密度,非常适用于几K的存储器MCU市场

R:实时处理器

按照我的理解,应该是因为有很多的中断,实现其实时性

A:应用处理器

性能最好,效能最高

在ARM7系列中,可以使用Embedded ICE JTAG进行在线调试

ARM7TDMI

T: 支持Thumb D: 在线调试 M: 双字相乘 I: 硬件仿真

存储器的字和半字

ARM处理器直接支持8位的字节,16位的半字和32位的字,其中以能被4整除的地址开始连续的4个字节构成一个字,从偶数地址开始连续的2个字节构成一个半字——ARM指令的长度为一个字(四个字节),Thumb指令的长度为一个半字(两个字节)

即ARM为32位的字,Thumb为16位的半字

注意:由于不管是ARM还是Thunb,地址都是偶数,因此bit0位一定是为0,ARM属于字对齐,bit1和bit0都为0,Thumb半字对齐,仅有bit0为0.

三级流水线

流水线的三个阶段分别为:取指,译码,执行

注意:ARM正在执行第一条指令的同时对第二条指令进行译码,并将第三条指令从存储器中取出。只有在取第四条指令时,第一条指令才算正真完成执行。

若将正在执行的指令作为参考点,称为第一条指令,则PC总是指向第三条指令,即:PC总指向正在执行的指令再加2条指令地址

ARM状态时:PC=当前指令位置+8字节

Thumb状态时:PC=当前指令位置+4字节

例如:

0x4000 ADD PC,PC,#4 ;正执行的命令,将PC+4赋给PC(找准PC的值)

0X4004 ... ;被译码的命令

0X4008 ... ;被取指的命令(PC总是指向正执行命令的地址再加2条指令地址,及现在这个地址,0X4008)

0X400C ... ;PC是0x4008,加上4之后为现在这个地址0X400CARM处理器的状态

当前程序状态寄存器CPSR中的控制位T反应处理器正在操作的状态,状态切换时不影响模式和寄存器的内容

ARM:T=0

上电默认状态也是ARM,32位

Thumb:T=1

16位

两者不能混合使用,内核必须切换状态才可以,切换的指令有BX(有条件跳转,检测R0的最低位,为0则为ARM,为1则为Thumb),BXL(无条件跳转)

;从ARM状态切换到Thumb状态

CODE32

LDR R0,=Lable+1 ;R0的bit0=1,BX自动将CPSR中T置1

BX R0 ;切换到Thumb状态,跳转到Lable

CODE16 ;Thumb指令

Lable MOV R1, #12

;从Thumb状态切换到ARM状态

CODE16 ;Thumb指令

LDR R0,=Lable ;R0的bit0为0,BX将CPSR中T置0

BX R0 ;切换到ARM指令

CODE32

Lable MOV R1,#10ARM处理器模式(7种)

用户模式

正常工作状态,不能由此切换到其他状态

系统模式

用户模式和系统模式不能由异常进入,想要进入系统模式,必须修改CPSR才能实现

如下:管理模式切换到系统模式:

MSR CPSR_c,#(NoInt | SYS32Mode)特权模式,与用户模式类似,但可以切换到其他模式,与用户模式共用相同寄存器

未定义模式

中断模式

快速中断模式

管理模式

中止模式

这五种属于异常模式,只有当相应的异常相应时,才能进入。

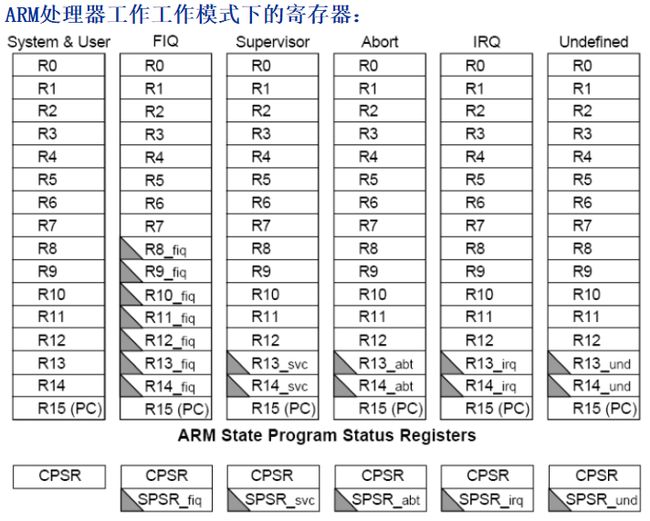

ARM内部寄存器

ARM共有37个寄存器,其中31个32位的都用了,另外有6个32位的仅用了12位。

ARM状态下的寄存器

一般通用

R0~R7

堆栈指针R13(SP)

保护待使用的寄存器里的内容

链接寄存器R14(LR)

保护现场返回地址,子程序的返回地址将自动的存入到R14中,当程序结束后,将R14复制到程序计数器PC中,实现子程序的返回

执行如下任何一条指令都OK

MOV PC,LR

BX LR在子程序入口,使用STMFD指令将R14和其它寄存器的内容保存到堆栈SP中

STMFD SP!,{<registers>,LR}在子程序结束时,使用批量寄存器读取指令LDMFD,将返回地址从堆栈中复制到程序计数器PC中,实现子程序返回

程序计数器R15(PC)

当前程序状态寄存器,P15(PC)总是指向正在取指的指令。若无其他跳转指令,则PC将自动加1个地址,跳转到下一个地址位

(1)读R15

当使用STM或STR指令保存R15时,R15保存的是当前指令地址+偏移量

测试芯片具体存储PC时的偏移量程序:

SUB R1,PC,#4 ;R1存放下面STR指令的地址

STR PC,[R0] ;保存“STR指令地址+偏移量”到R0中

LDR R0,[R0] ;重装

SUB R0,R0,R1 ;计算偏移量=PC-STR地址(2)写R15

由于ARM是字对齐的,因此写的地址必须是有效的正确地址,即是bit0=0,bit1=0,bit[1:0]=0b00

Thumb半字对齐,bit0=0,写入地址时可先与0xFFFF FFFE相与再写入

CPSR和SPSR

用户和系统模式不是异常中断,没有SPSR,其他每种异常都有各自相应的SPSR,它们的作用是异常产生时,保存当前CPSR的值。然后设置CPSR为相应的异常模式。异常中断程序退出返回时,可以通过保存在SPSR中的值来恢复CPSR

除用户模式,其他每种处理器模式都可以通过改写CPSR中的模式位改变

Thumb状态下寄存器

各种模式下实际访问的寄存器

一般通用寄存器

R8~R12thumb状态一般不会用,只有个别指令可以访问,如MOV,ADD,CMP

堆栈指针R13(SP)

Thumb指令集带有传统PUSH和POP指令用于堆栈操作处理。

链接寄存器R14(LR)

跟前面ARM的用法差不多

ARM状态寄存器和Thumb状态寄存器的关系

R0~R7是相同的

Thumb状态CPSR(没有SPSR)和ARM的CPSR一样,Thumb指令集不包含MSR和MRS,要修改CPSR任何标志位必须回到ARM状态,而且当完成复位时,或者进入到异常模式时,会被自动切换到ARM状态

所有异常在ARM状态下执行

当前程序状态寄存器

条件代码标志

N: 负标志,运算结果的第31位,记录标志设置操作结果

Z: 零标志

C: 进位标志

V: 一处标志

控制标志位

I: 中断禁止标志,I=1禁止

F: 快速中断禁止标志,F=1禁止

T: 处理器状态位,T=1,Thumb;T=0,ARM

M0~M4:处理器模式位,特定的几种模式位有定义处理器模式

ARM体系的异常、中断及向量表

~~~~老胡说这里很重要!!!

可是我好困了,这个留着明天再总结好了~