2020年受疫情影响的寒假

2020年春节,相信,很多人会记得,受全国肺炎疫情的影响,上学不能上学,上班不能上班,然而,在家浪了几天后,实属无聊,于是,又拿起了家里的旧电脑,开始更新博客,开始漫长的寒假在家学习之路。

2.8 开始学习的第一天,把要看的资料准备好,感觉自己虽然找到了工作,但是基础还是不怎么扎实,从最基础的东西,一步一步深入学习,加油,武汉!加油,小卢同学!

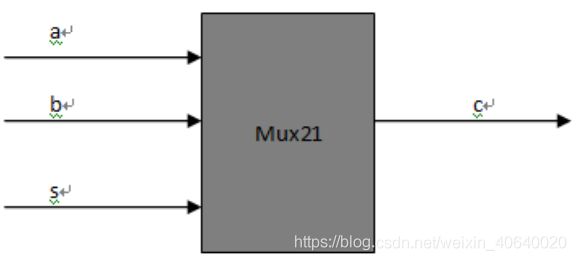

2.9 第一篇 多路选择器

架构图:

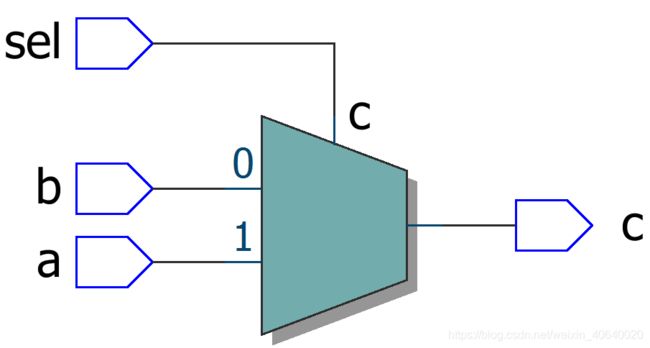

代码1:

module mux21(

input a,

input b,

input sel,

output c

);

assign c = (sel==1)? a:b ;

endmodule代码1综合后的RTL电路为:

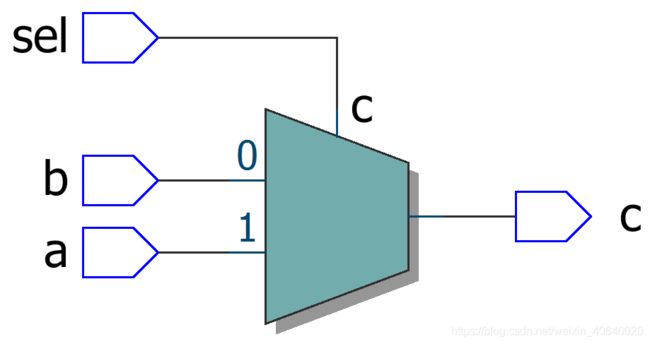

代码2:

module mux21(

input a,

input b,

input sel,

output reg c);

always @(*)

begin

if(sel)

begin

c <= a;

end

else

c <= b;

end

endmodule综合电路

都是组合逻辑电路,综合后的电路一样。

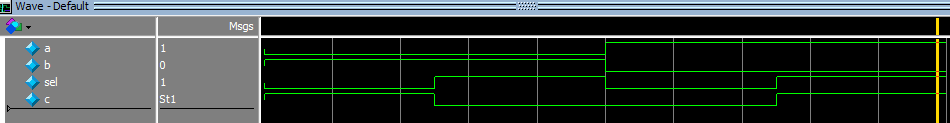

下面进行仿真:

`timescale 1ns/1ps

module mux_21_tb();

reg a;

reg b;

reg sel;

wire c;

initial begin

a = 1'b0;

b = 1'b1;

sel = 1'b0;

# 50

a = 1'b0;

b = 1'b1;

sel = 1'b1;

# 50

a = 1'b1;

b = 1'b0;

sel = 1'b0;

# 50

a = 1'b1;

b = 1'b0;

sel = 1'b1;

# 50

$stop;

end

mux_21 mux_21_dut(

.a(a),

.b(b),

.sel(sel),

.c(c)

);

endmodule功能仿真也叫RTL级仿真

仿真结果:

下面讲讲时序仿真:

时序仿真使用布局布线后器件给出的模块和连线的延时信息, 在

最坏的情况下对电路的行为作出实际地估价。 时序仿真使用的仿真器

和功能仿真使用的仿真器是相同的, 所需的流程和激励也是相同的;

惟一的差别是为时序仿真加载到仿真器的设计包括基于实际布局布

线设计的最坏情况的布局布线延时, 并且在仿真结果波形图中,时序

仿真后的信号加载了时延, 而功能仿真没有。

经过查看波形,发现延时输出,并且还有一个小的毛刺。 时钟端

口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使

系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设

计人员必须要考虑的问题。

毛刺并不是对所有的输入都有危害,例如 D 触发器的 D 输入端,

只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就

不会对系统造成危害,我们可以说 D 触发器的 D 输入端对毛刺不敏感。

根据这个特性,我们应当在系统中尽可能采用同步电路,这是因为同

步电路信号的变化都发生在时钟沿,只要毛刺不出现在时钟的沿口并

且不满足数据的建立和保持时间,就不会对系统造成危害(由于毛刺

很短,多为几纳秒,基本上都不可能满足数据的建立和保持时间)。

其次,要记住,Verilog是硬件描述语言,是对你的硬件电路的描述,在写逻辑之前,要看自己的电路的设计图。

案例二:案件控制小灯led_key

案件三:流水灯led_run

发现,学习真会上头,越学越停不下来,继续!

总结下今晚,三段式状态机:

第一段:第一个always块,描述对应当前状态的状态寄存器,非阻塞赋值:

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

state <= 3'd0;

end

else

state <= n_state;

end第二段:第二个always块,描述下一状态的状态寄存器,阻塞赋值:

always @(*)

begin

//n_state <= 3'd0;

case(state)

3'd0 : begin

if(t1s == 1)

n_state = 3'd1;

else

n_state = 3'd0;

end

3'd1 :begin

if(t1s == 1)

n_state = 3'd2;

else

n_state = 3'd1;

end

3'd2 :begin

if(t1s == 1)

n_state = 3'd3;

else

n_state = 3'd2;

end

3'd3 :begin

if(t1s == 1)

n_state = 3'd4;

else

n_state = 3'd3;

end

3'd4 :begin

if(t1s == 1)

n_state = 3'd1;

else

n_state = 3'd4;

end

default : n_state = 3'd0;

endcase

end

第三段:第三个always块,描述输出

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

led <= 4'b0000;

end

else

begin

case(state)

3'd0 : led <= 4'b0000;

3'd1 : led <= 4'b1110;

3'd2 : led <= 4'b1101;

3'd3 : led <= 4'b1011;

3'd4 : led <= 4'b0111;

default : led <= 4'b0000;

endcase

end

end

endmodule

在 fpga 设计当中, 尽可能的去用时序逻辑输出。