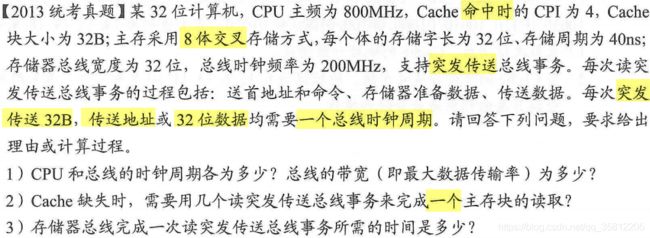

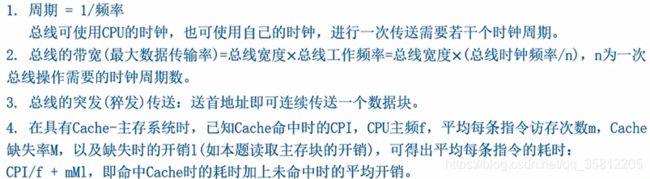

2013年总线+存储器大题

【知识回顾】

第一问:CPU&总线T、总线带宽

T-CPU时钟=1/800M ns=1.25ns;总线时钟周期=1/200M s=5ns

我的弱智答案:总线的带宽=32B/(1/200M) s;

错因: 理解错题意“每次突发传送32B,传送地址或32位数据均需要一个总线时钟周期”不是指突发传送32B用一个总线周期==

正确答案是:总线宽度为32位,总线带宽=4B×200MHz=800MB/s

或4B/5ns=800MB/s(前面算出一个总线时钟周期是5ns,而题目说了“传送32位数据需要一个总线时钟周期”)

这里直接将总线时钟频率当做总线工作频率是因为传32位只需要一个总线时钟周期,若改成“传送32位数据需要n个总线时钟周期”则【总线工作频率=总线时钟频率/n,n为一次总线操作所需要的时钟周期数】

第二问:读块时间

一个突发传送总线事务可传送32B,而一个块为32B,所以Cache(32B)缺失时,需要1个总线事务

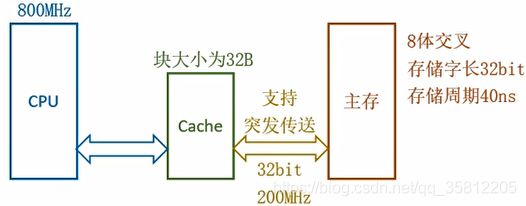

第三问:总线事务用时

【法一】

一次总线事务包括:(1)送首地址&命令(1×T总线时钟);(2)准备data;传送data。

(1)送首地址&命令:命令没有给出具体描述,就默认命令和送首地址并行进行。

(2)存储器准备data:在多体交叉中,每个体40ns可提供32bit数据;每隔40ns/8=5ns启动一个存储体工作,则准备(不是传送~传送是总线的任务)32B的数据耗时40ns+(8-1)×5ns=75ns

(3)总线传送data:存储器准备好data后,耗费一个总线时钟周期传出。

一个32位的data需要一个总线时钟周期(5ns),结合(2)过程,在40ns时存储器准备好第一个数据(总线用5ns把该数据传出),传完后第二个数据又准备好了(准备的时候就往外传了——“流水线”),所以总线又用5ns把该数据传出。。。到最后一个数据准备好后,还需要总线最后一个5ns把该数据传出。

综上,5+75+5=85ns。

【法二】

弱智答案:存储周期为40ns,32位用5ns,所以一次读突发总线事务要5×(32÷4)=40ns。

显然一开始对描述的总线事务没读懂题意==

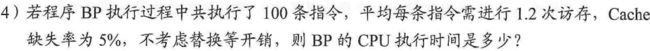

第四问:CPU执行时间

(题目的“不考虑替换等开销”指Cache的替换策略——一般替换算法在OS考察)

【法一】

1)Cache命中时平均每条指令需要4个CPU时钟周期:

4×1.25ns=5ns

2)Cache未命中时,通过读突发传送总线事务读取相应主存块到Cahce(总线事务),CPU再完成该条指令:

1.2×85ns+5ns=107ns(后面的5ns是因为不命中情况也要先访问Cache,从“命中Cache的CPI=4”知4×1.25=5ns)

所以执行时间=100×0.95×5ns+100×0.05×107ns=1010ns

注意:此处是访问Cache和主存同时进行,题目也没给出访存。

【法二】

一条指令执行过程中因Cache缺失而导致的平均额外开销=

平均访存次数×Cache缺失率×一次读突发传送总线事务时间=1.2×5%×85ns=5.1ns

一条指令的平均CPU执行时间=5ns+5.1ns=10.1ns

BP的CPU执行时间=一条指令的平均CPU执行时间×指令条数=10.1ns×100=1010ns

我的弱智答案:平均每条指令1.2次访存,即120次访存,Cache缺失率为5%,Cache命中时的CPI=4,由(2)(3)知Cache缺失时用1×40=40ns完成一个块的读取。 120*5%*85+120*95%*4