Quartus2之引脚锁定和下载到机箱的实例

文章目录

- 一、引脚锁定

- 1.选择机箱

- 2.引脚锁定

- 3.编译

- 二、下载

一、引脚锁定

1.选择机箱

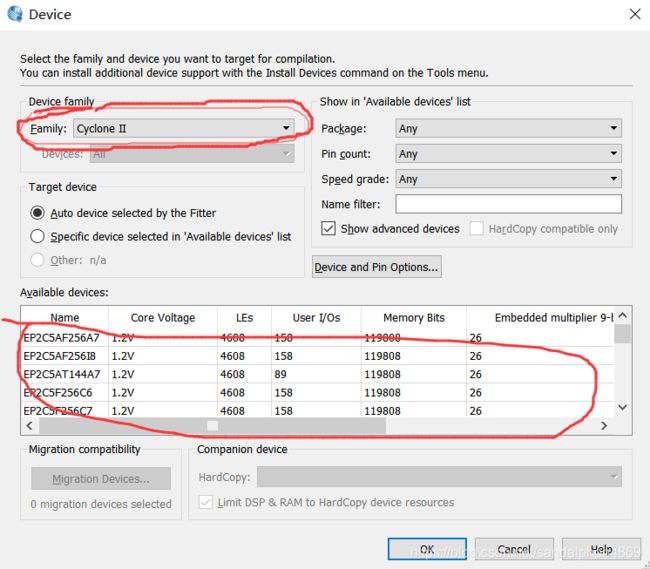

选择菜单 Assignments->Device

选择Device family和选定与实验机箱相同的设备名。

2.引脚锁定

选择菜单 Assignments->pins->Location

根据实验电路结构图 NO.0 和芯片引脚对照表, 查出 a[5…0],clk ,q[7…0] ,在核心芯片 EP3C40Q240C8 上所对应的引脚号,进行引脚锁定,具体如下:

- 输入输出引脚名 | 实验电路图 | 芯片引脚pin|

a[5]-------PIO 13-------51

a[4]-------PIO 12-------50

a[3]-------PIO 11------49

a[2]-------PIO 10------46

a[1]-------PIO 9-------45

a[0]-------PIO 8-------44

clk--------CLOCK0------152

q[7]-------PIO 31-----126

q[6]-------PIO 30-----118

q[5]-------PIO 29-----117

q[4]-------PIO 28-----114

q[3]-------PIO 27-----113

q[2]-------PIO 26-----112

q[1]-------PIO 25-----80

q[0]-------PIO 24-----78

经过以上操作: a[5…0] 锁定 键 2,1

clk 锁定 CLOCK0

q[7…0]锁定 数码管 4, 3

引脚锁定后再次编译

3.编译

二、下载

将电脑与实验箱通过并口连接接好,点快捷键 ,在出现的*.sof 文件上, 选中rogram/configure 点快捷键 。 即可设计下载到 FPGA 中。最后是用实验箱进行硬件测试。