信号完整性测试入门——SECOND

经验法则是一种可以广泛应用于多种情况下的原则和方法。在SI设计中,经验法则用于粗略估计某种参数或指定设计中应该遵循的原则。比如,FR4板材上信号的衰减大约为0.1dB/inch/GHz,这种经验法则可以在设计之前快速粗略地估计信号可能有多大的衰减。

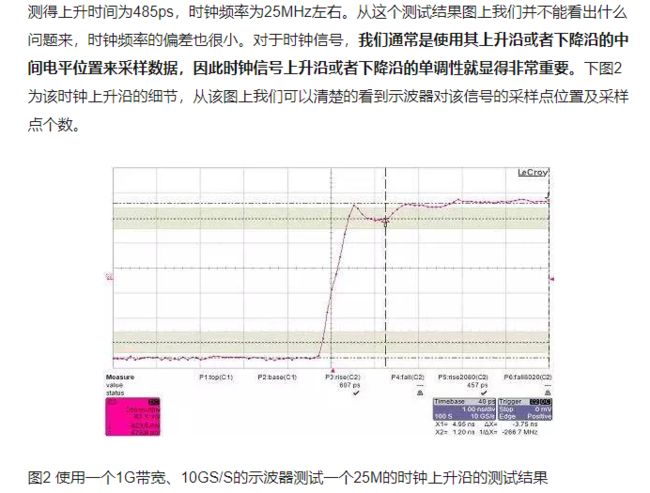

SI设计是个性化的,对于局部总线,关注的仅仅是本身的质量,对反射、串扰、电源滤波等几个方面的设计就能让电路正常工作。在高速同步总线(如DDR)中,只关注反射串扰电源等基本问题还不够,信号波形本身质量好,不能保证电路正常工作,还需要满足时序要求。时钟频率很高时,设计的重点应该落在总线的时序上,改善信号本身质量的目的最终还是为了满足时序要求。在时钟电路中,设计的重点在于保证时钟边沿的单调性、时钟频谱的纯净度、时钟的抖动等性能指标。

时钟边沿单调性:

BW=0.35/RT 其中BW为带宽,RT为上升时间。 以FR4材料为例,每英寸信号延迟为180ps左右