SDRAM驱动需要两个时钟,一个是控制时钟,一个是驱动时钟,这两个时钟有一个相位差,如何产生高精度的时钟是SDRAM能够正常工作的关键,采用FPGA内部动态可重置PLL生成SDRAM所需要的时钟频率。

1.PLL

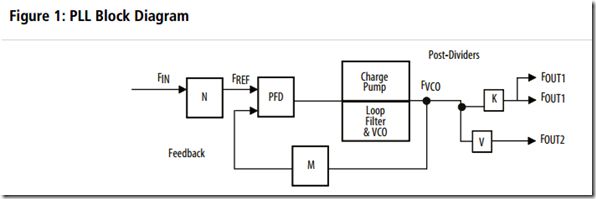

上图是PLL的 官方文档中的内容。PLL主要由前N分频计数器(pre-divider counter),相位频率检测(PFD) ,电荷泵和环路滤波器,VCO(压控振荡器),反馈乘法器计数器(M计数器)和一个后分频计数器。

上图是PLL的 官方文档中的内容。PLL主要由前N分频计数器(pre-divider counter),相位频率检测(PFD) ,电荷泵和环路滤波器,VCO(压控振荡器),反馈乘法器计数器(M计数器)和一个后分频计数器。

PFD检测参考时钟信号(fREF)和补偿时钟信号(feedback)在相位和频率的差,然后控制电荷泵和环路滤波器,并且将相位差转换成一个控制电压信号,进而控制VCO。当PFD产生上升信号,VCO就增加,反之VCO下降。

上图中电荷泵是接收PFD输出的上升信号和下降信号给CP,CP收到上升信号,电流注入LF增大,反之减小。

LF主要是将上升和下降信号转换为电压,作为VCO的偏置电压。LF还消除了CP的干扰,防止电压过冲,最小化减少VCO的抖动。LF电压决定了VCO的操作速度。

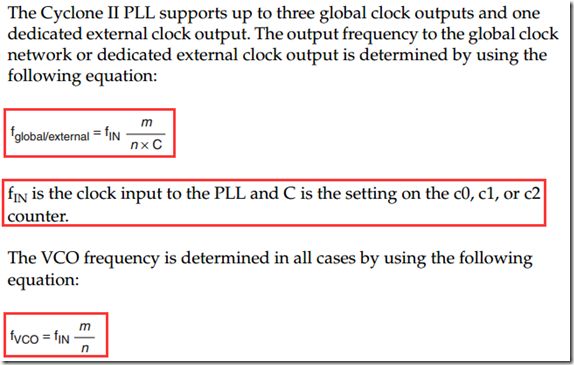

上图是输出频率的计算公式,M和N在quartus II中类似于倍频和分频概念。PLL的精度由M和N的位数决定。

精简结构如下图所示:

2.quartus II 配置PLL操作

在PLL官方手册中可以找到如上图手册,对于其他cyclone XX系列芯片,操作都是类似的。

上图中解释了对于cyclone xx系列最高可以跑到多大时钟频率。

上面公式定义了 fout时钟和VCO时钟,且VCO时钟必须在300~1000Mhz之间。手册有如下解释。

上图是PLL中所需要的信号接口,有些信号可以进行选择性的使用。

inclk为时钟输入引脚,pllena信号在高电平时可以使能和复位PLL。当pllena为低电平时,PLL不工作,高电平PLL开始锁相。

areset引脚要特别注意,此引脚我们经常用,此引脚是高电平复位,低电平时PLL不工作。

3.PLL时钟补偿模式

PLL支持四种补偿模式,正常模式(normal mode),零延时缓冲模式(zero delay buffer mode),非补偿模式(no compensation mode),源同步模式(source synchronous mode)。上述的几种模式都支持倍频和分频,相移以及占空比的可调。

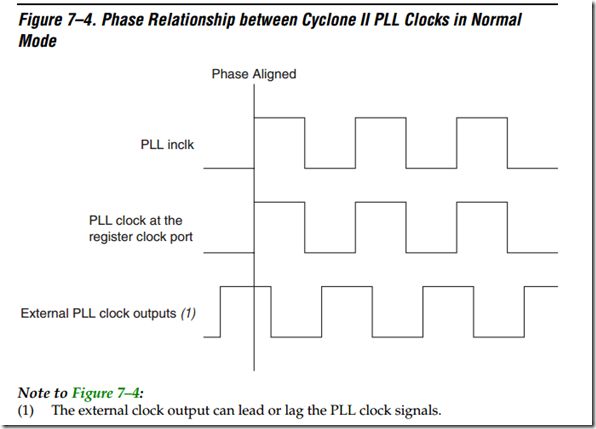

(1)正常模式(normal mode)

在正常模式下,PLL将输入时钟与参考时钟进行锁存对齐,输出时钟或者提前或者延后与PLL的输入时钟。

(2)零延时缓冲模式(zero delay buffer mode)

再此模式下,PLL的输入时钟的相位和PLL的输出时钟相位对齐,但是内部时钟会延时或提前于外部输出时钟。在此模式下,altera推荐输入引脚和输出引脚必须是相同的I/O标准。

再此模式下,PLL的输入时钟的相位和PLL的输出时钟相位对齐,但是内部时钟会延时或提前于外部输出时钟。在此模式下,altera推荐输入引脚和输出引脚必须是相同的I/O标准。

(3)非补偿模式(no compensation mode)

在此模式下,PLL不会对任何的相位进行补偿。输出时钟相位超前或迟滞内部时钟。

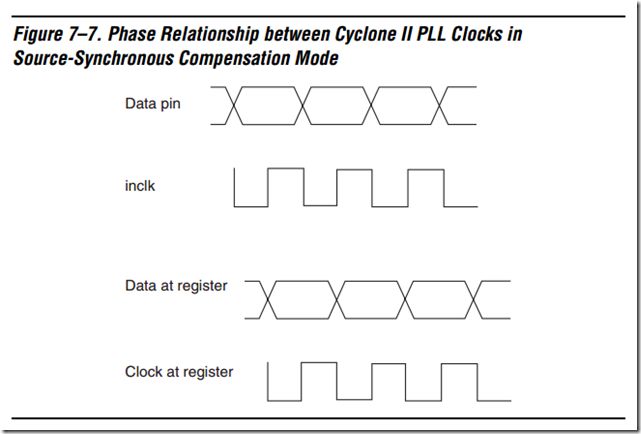

(4)源同步模式(source synchronous mode)

这种情况适用于输入数据和时钟同时到达的情况。

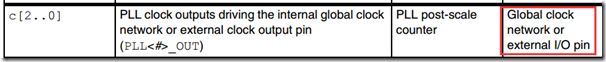

4.多个频率输出情况

上述三个输出时钟都可以驱动全局时钟网络。c2可以驱动一个专用外部I/O引脚(PLL<#>_OUT) 。那么对于多个利用PLL输出的频率,VCO在处理时会倍频。然后在输出时再降频,如从PLL输出需要33MHz和66MHz,那么VCO会被设定到330MHz(这个设定需要在VCO范围内,即300Mhz~1000Mhz)。

上述三个输出时钟都可以驱动全局时钟网络。c2可以驱动一个专用外部I/O引脚(PLL<#>_OUT) 。那么对于多个利用PLL输出的频率,VCO在处理时会倍频。然后在输出时再降频,如从PLL输出需要33MHz和66MHz,那么VCO会被设定到330MHz(这个设定需要在VCO范围内,即300Mhz~1000Mhz)。