原子教你玩STM32_2020.5.9

DMA:动态数据存储,为CPU减负,直接进行数据交换

芯片内部结构

BOOT0 BOOT1

0 X :从片上Flash代码区域启动,执行固件

1 0 :系统存储器BootLoader区域,引导进行串口1下载

1 1 :执行SRAM区域代码

先RST低,DTR高,所以RESET低电平复位,单片机复位

后RST低,DTR低,此时RESET为高复位结束,B0为高,进入ISP

通过CH340G的rst和dtr引脚间接控制单片机的RST和BOOT0引脚,实现的程序一键式下载

手册中有FT标识部分的表示可以容忍5V电压

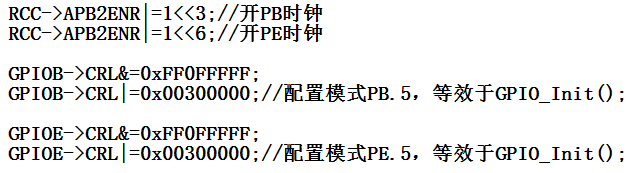

GPIO口的使用:打开相应时钟

配置相应的模式

配置相应的速度

浮空输入模式:自由的输入端,电平传输最终到达相应的

寄存器,读取寄存器值

模拟输入模式:自由输入端,电压被采样到相应的外设部

分,不到达输入寄存器

输出高低电平时,写位设置/清除寄存器---->输出数据寄

存器,控制后续电路的输出电平极性

GPIOx_CRL:端口配置低8位寄存器,每4位控制一个IO

例:PA0-PA7 PA0(3-2:配置输入/输出速度模式)

(1-0:配置输入输出模式细化)

GPIOx_IDR:低16位有效,对应相应IO口的输入电平0/1 在输出模式下也可以读取其上电平,以验证

GPIOx_ODR:低16位有效,对应相应IO口的输出电平0/1

在输入模式下兼有上下拉的选择功能

GPIO_BSRR:端口位设置/清除寄存器

0-15位对应位1,输出高,低无效

16-31位对应位1,输出低,低无效

间接控制ODR寄存器设置IO口

使能IO口时钟 RCC_APB2PeriphColckCmd();

初始化IO口模式,调用GPIO_Init();

操作IO口:GPIO_SetBits(); GPIO_ResetBits();

不同方法操作IO口,最终都是操作相应的底层寄存器ODR/IDR

位带操作:单个IO口的位重新定义为新的地址,可以直接操作地址

如:PAout(1)=1;

位操作:GPIOA->CRL&=0XFFFFFF0F;

GPIOA->CRL|=0XFFFFFF4F; //0101

GPIOA->ODR|=1<<5;

TIMx->SR=(unint16_t)~TIM_FLAG;

Define宏定义:

#define sysclk_freq_72MHz 72000000

前为所定义的宏名,后为常数 表达式 格式串等

ifdef:条件编译

#ifndef

#define

....

#end if

Typedef:类型别名

typedef unsigned char uint8_t;

typedef unsigned int uint32_t;

typedef unsigned short int uint16_t;

STM32,一切底层配置都是配置相关寄存器

sfr P0=0X80;//特殊功能寄存器地址

P0=0X00;//特殊功能寄存器赋值

GPIOA->ODR=0X00000000;

寄存器地址位置映射:

重要的是在顶层中将特定位置的顺序地址

强制类型转换:划分为一个结构体类型,方便查询使用

STM32时钟框图

任何外设使用之前,必须使能相应的时钟

时钟结构体类型定义:与时钟相关寄存器的集合

时钟相关库函数:

STM32的USB slave模式下D+需要接上拉电阻到VCC

USB转串口时只需要D+和D-引脚

Mini和Micro的座子的第4脚ID引脚默认下悬空,正常工作