单片机的IO,推挽输出、高阻状态

单片机的IO,推挽输出、高阻状态

集电极开路,Open Collector 简称 OC 门

上图所示,集电极开路由两个NPN型三极管组成。Q1 的集电极作为 output pin,因此称为集电极开路。

a. 输入低电平“0”,Q2截止,VCC 无法通过电阻接地,Q1 导通,output 输出“0”。

b. 输入高电平“1”,Q2 导通,VCC 通过电阻接地,Q1 截止,但是 output 无法输出高电平“1”。

如果要想输出高电平可以在输出端加上上拉电阻。因此集电极开路输出可以用做电平转换,通过上拉电阻

上拉至不同的电压,来实现不同的电平转换。

用做驱动器。由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。OC门使用

上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片

的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

这种三极管是电流控制型元器件,注意关键词电流控制。意思就是说,只要基极B有输入(或输出)电流就可以对这个晶体管进行控制了。

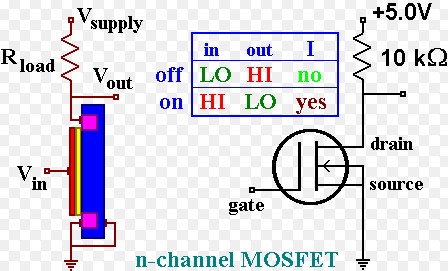

漏极开路,Open Drain 简称 OD 门

上图所示,漏极开路由一个N-MOSFET组成,MOS 的漏极作为 output pin,因此称为漏极开路。

典型的用法是在漏极外部的电路添加上拉电阻到电源如图所示。完整的开漏电路应由开漏器件和开漏上拉电阻组成。

这里的上拉电阻R的阻值决定了逻辑电平转换的上升/下降沿的速度。阻值越大,速度越低,功耗越小。

因此在选择上拉电阻时要兼顾功耗和速度。标准的开漏脚一般只有输出的能力。

场效应管是电压控制型元器件,只要对栅极施加电压,DS就会导通。

结型场效应管有一个特性就是它的输入阻抗非常大,这意味着:没有电流从控制电路流出,也没有电流进入控制电路。没有电流流入或流出,就不会烧坏控制电路。而双极型晶体管不同,是电流控制性元器件,如果使用开集电路,可能会烧坏控制电路。这大概就是我们总是听到开漏电路而很少听到开集电路的原因吧?因为开集电路被淘汰了。

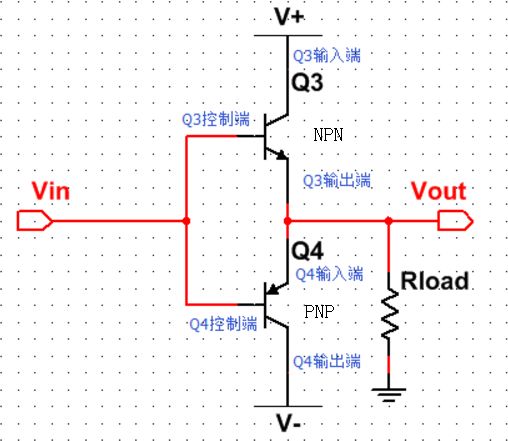

推挽输出,Push-Pull

当Vin电压为V+时,上面的N型三极管控制端有电流输入,Q3导通,于是电流从上往下通过,提供电流给负载。

经过上面的N型三极管提供电流给负载(Rload),这就叫「推」。

当Vin电压为V-时,低于Q4的导通电压,下面的三极管有电流流出,Q4导通,有点流从上往下流过。

经过下面的P型三极管提供电流给负载(Rload),这就叫「挽」,也称为拉。

以上,这就是推挽(push-pull)电路。

推挽输出不仅可以采用三极管,也可以使用MOSFET(场效应管),如下图。

单片机IO口

一对管子组成的推挽结构,从电路上来讲可以通过调配管子的参数轻松实现输出大电流,提高带载能力。

两个管子根据通断状态不同有4种组合。上下管都导通相当于把电源和GND短路了,这种情况是不允许出现的。

从数字逻辑的角度上来讲,上管开-下管关相当于IO口与Vcc直接相连,IO口输出高电平“1”。上管关-下管开时

IO口与GND直接相连,IO口输出低电平“0”。这种结构下如果没有外接上拉电阻,输出“0”的状态就是俗称

的“开漏”(Open-Drain:漏极开路)状态。有的资料上也把这种状态称为“低阻态”,因为IO引脚是通过一个

管子接地的,并不是直接使用导线连接,而一般的MOS在导通状态也会有mΩ级别的导通电阻。

分析到这里就很明白了,“低阻态”是IO口相对于GND而言的,那“高阻态”也是相对于GND而言的啦。怎么把

GND和IO口隔离起来达到类似开路的状态?把下管置于截止状态就可以了。这时候推挽的一对管子都是截止状态,

忽略读取逻辑的话IO口引脚相当于与MCU内部电路开路。考虑到实际电路的MOS截止时并不是完美的开路,有少许

的漏电流,所以称为“高阻态”。

不是所有的单片机都支持三态输出。三态输出一般由寄存器控制,需进行配置。

高阻态既然无确定电平,怎么能做输出呢?把一个端口置为高阻态,相当于该端口从电路中断开(仅对输出来说),

比如在一个通信线上挂了几个端口,将一个端口置为高阻态,就意味着该端口不会影响到该通信线的电平变化,

但还是可以读取端口的电平。一般高阻态都是作为模拟量输入的,因为高阻态不会影响到输入的电平,可以

准确的读取模拟量。