【PYNQ-Z1学习笔记】NO.1 纯PL端开发示例

最近搞来一块PYNQ-Z1,不要问我为什么没搞Z2,因为花的不是俺的钱,俺不好意思提要求了。蛤蛤~

我发现PYNQ给的官方文档都是直接刷系统写python的,我们新时代求知若渴好青年怎么能直接就这样开始了呢!必然要先试一试它的其他模式~正好我也没玩过ZYNQ系列,试一试纯PL开发,SDK,标准ZYNQ开发流程,最后再搞一搞PYNQ的开发。(其实因为我买的SD卡还没到)

PYNQ-Z1

PYNQ-Z1开发板是全球第一块Python on FPGA开发板。其所支持的 PYNQ 项目,是一个新的开源框架,使嵌入式编程人员能够在无需设计可编程逻辑电路的情况下即可充分发挥 Xilinx Zynq All Programmable SoC(APSoC)的功能。与常规方式不同的是,通过 PYNQ,用户可以使用 Python 进行 APSoC 编程,并且代码可直接在 PYNQ-Z1 上进行开发和测试。通过 PYNQ,可编程逻辑电路将作为硬件库导入并通过其 API 进行编程,其方式与导入和编程软件库基本相同。

技术文档:http://www.digilent.com.cn/community/411.html

简单来说就是一块芯片上既有PS又有PL这就是ZYNQ,可是这对小朋友的要求有点高,我们万物皆python吧!何不用python来开发硬件呢,这就诞生了PYNQ。

纯PL开发的准备

首先上图,粉红色的板子好似美娇娘2333

要把它当个FPGA用的话,我们用JTAG作为烧录方式。首先把左上角的跳线帽选到“JTAG”,左下角控制电源的跳线帽选到“USB”,如上图所示。这块板子的JTAG和UART就是一个,就左边那个micro-USB接口。

至于我们用到的软件,X家的VIVADO想必是老朋友了,不多说。完成之后就可以开干了。

用PLL产生不同时钟间歇点亮4个LED

代码很简单,也没什么意思,仅供娱乐之用。

首先创建一个VIVADO工程,就跟以前用FPGA一毛一样,然后选zynq XC7Z020这个芯片,一路next就OK了。

1.使用Xilinx的PLL IP核

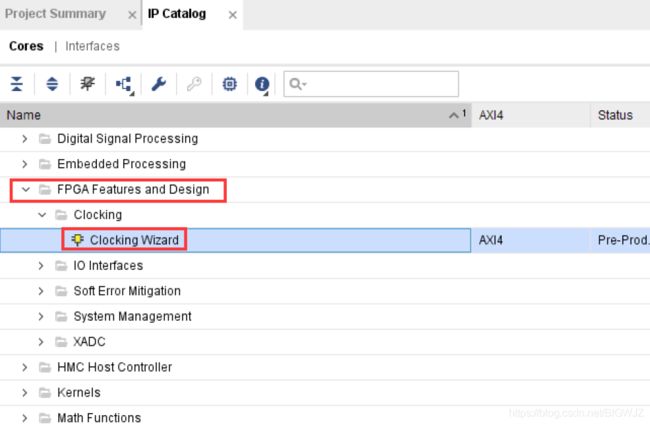

进入工程界面,首先我们搞个PLL,点击IP Catalog

选择Clocking Wizard

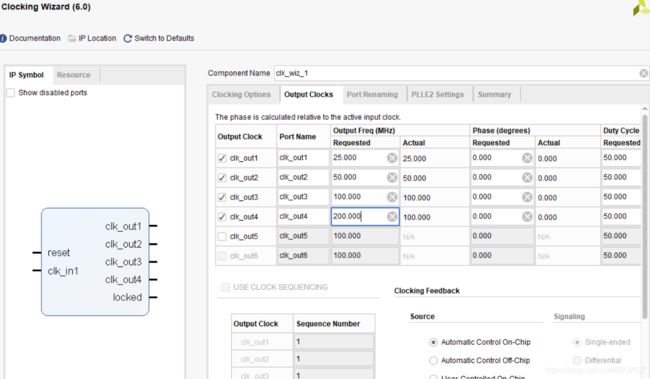

做四个输出 25,50,100,200MHz

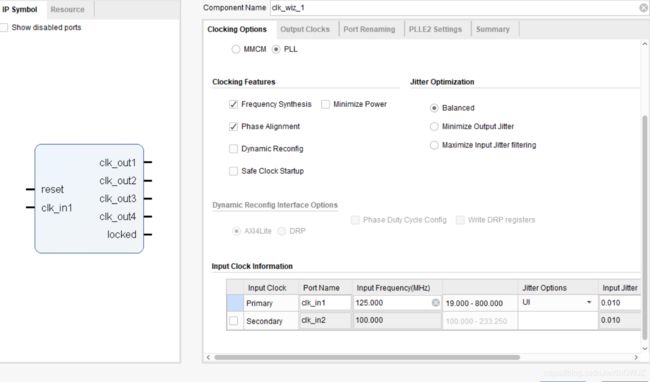

PYNQ-Z1的PL端板载晶振125MHz,这玩意我在网上找了半天,结果发现digilent网上给了约束文件,就在上面那个网址里面。我们给他设置成PLL,时钟输入125。

一路OK+next,完毕over

2. 写设计文件

我想让四个LED以不同频率闪烁,写两个小小verilog,如下:

module pll_test(

input sys_clk,

input bt0,

output led0,led1,led2,led3

);

wire locked;

wire rst_n;

reg[31:0] timer_cnt;

wire clk_1,clk_2,clk_3,clk_4;

assign rst_n=~bt0;

clk_wiz_0 clk

(

// Clock out ports

.clk_out1(clk_1), //OUT 200MHz

.clk_out2(clk_2), //OUT 100MHz

.clk_out3(clk_3), //OUT 50MHz

.clk_out4(clk_4), //OUT 25MHz

// Status and control signals

.reset(bt0),

.locked(locked),

// Clock in ports

.clk_in1(sys_clk)

);

led l0 (clk_1,rst_n,led0);

led l1 (clk_2,rst_n,led1);

led l3 (clk_3,rst_n,led2);

led l4 (clk_4,rst_n,led3);

endmodule

module led(

input clk,

input rst_n,

output reg led

);

reg [31:0] timer_cnt;

always@(posedge clk or negedge rst_n)

begin

if (!rst_n)

begin

led <= 0 ;

timer_cnt <= 32'd0 ;

end

else if(timer_cnt >= 32'd49_999_999)

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

endmodule

3.写约束文件

拒绝GUI,我们要学会直接写约束文件!(复制官网上的文件再改改)

新建一个约束文件。

set_property -dict { PACKAGE_PIN H16 IOSTANDARD LVCMOS33 } [get_ports { sys_clk }]; #IO_L13P_T2_MRCC_35 Sch=sysclk

create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports { sys_clk }];

set_property -dict { PACKAGE_PIN D19 IOSTANDARD LVCMOS33 } [get_ports { bt0 }]; #IO_L4P_T0_35 Sch=btn[0]

set_property -dict { PACKAGE_PIN R14 IOSTANDARD LVCMOS33 } [get_ports { led0 }]; #IO_L6N_T0_VREF_34 Sch=led[0]

set_property -dict { PACKAGE_PIN P14 IOSTANDARD LVCMOS33 } [get_ports { led1 }]; #IO_L6P_T0_34 Sch=led[1]

set_property -dict { PACKAGE_PIN N16 IOSTANDARD LVCMOS33 } [get_ports { led2 }]; #IO_L21N_T3_DQS_AD14N_35 Sch=led[2]

set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports { led3 }]; #IO_L23P_T3_35 Sch=led[3]

不会有人对着原理图找引脚,一个一个的在VIVADO里面填吧,不会吧不会吧?不会有人不知道digilent上有XDC文件吧,不会吧不会吧?

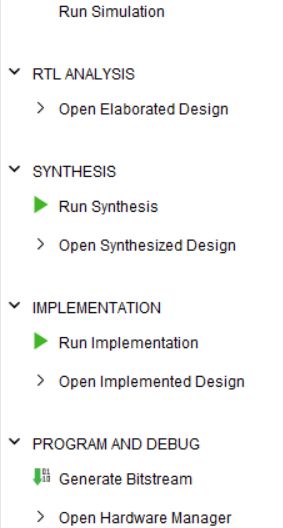

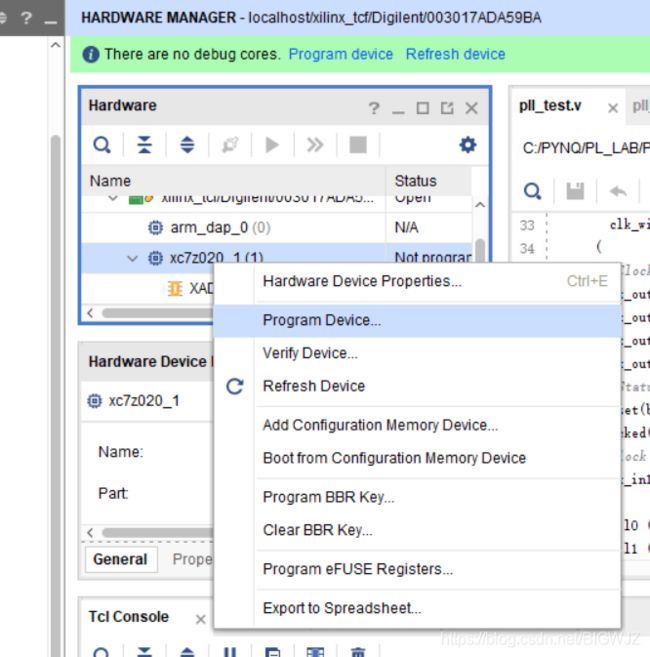

4.综合,生成bit,烧录

这没啥好说的,按照上面一个一个来呗,最后连上JTAG直接把bit文件烧进去。

康康最后结果吧~

额,上传视频好麻烦,放两张照片吧…

总结

这是篇没啥营养的笔记,FPGA大家都会用,我写的也不详细。PYNQ-Z1当成FPGA用就和其他没啥区别,其他FPGA上的也可以放到这上面来做一下好玩的,毕竟他有HDMI输入输出。总之就这样了,之后再尝试尝试SDK和Linux。

走过路过点个赞QAQ~