FPGA与PCB协同设计 -- IO Designer使用方法(3)

设计流程二:

Xpedition Designer设计原理图 + IO Designer Optimizer优化布局布线

步骤1: 用Xpedition Designer设计原理图

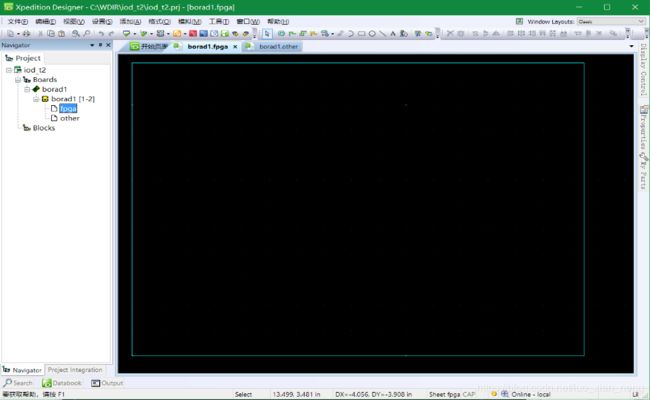

other页,放其他元件;fpga页为空, 准备放FPGA的元器件,如下图

步骤2:建立FPGA的临时元器件(存放到临时元件库中)

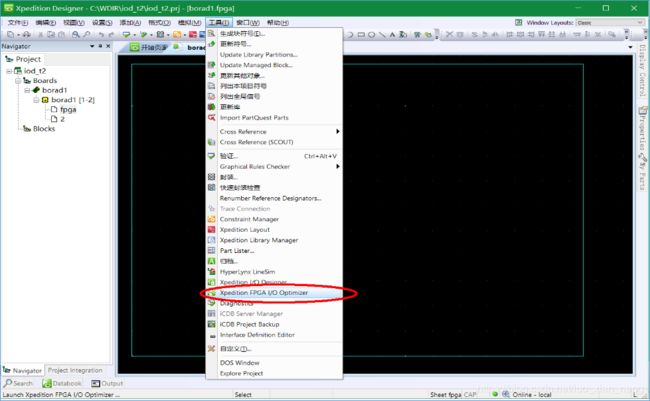

菜单选择“工具”--》 “Xpedition FPGA I/O Optimizer” 启动IO Designer

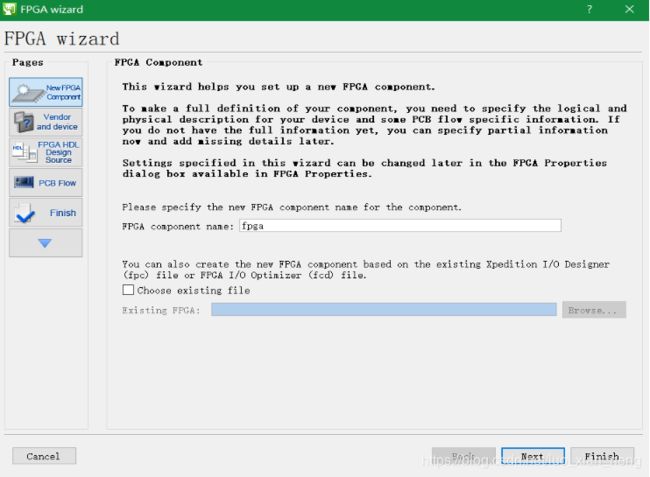

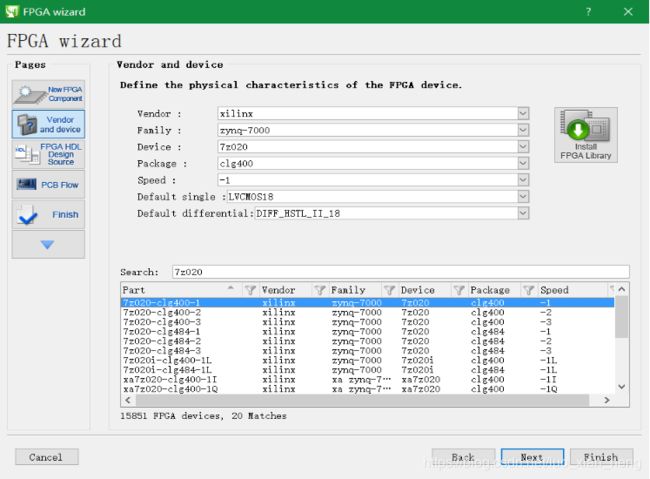

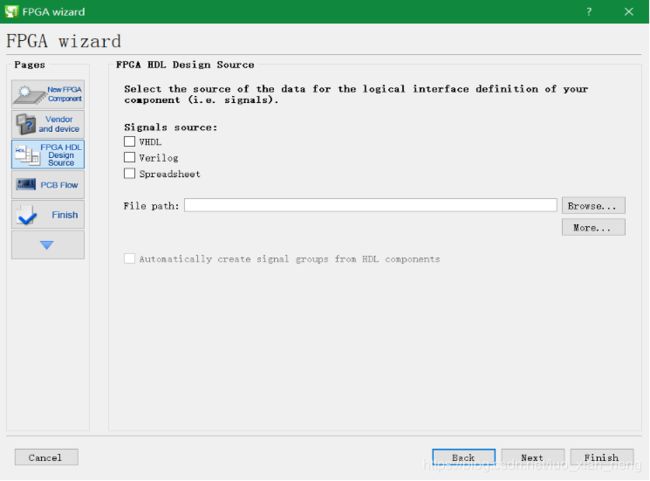

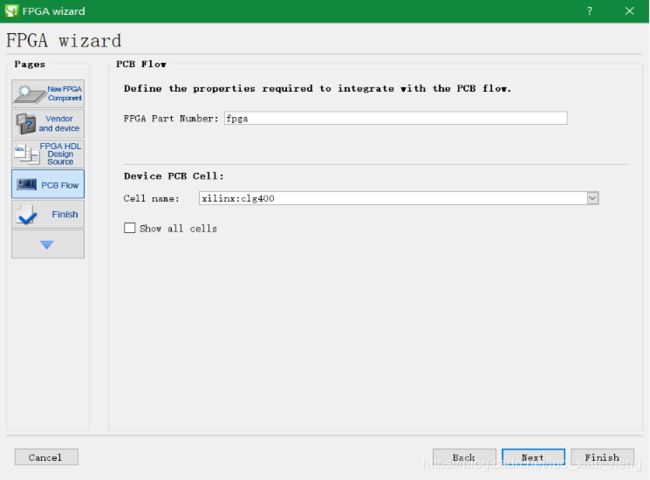

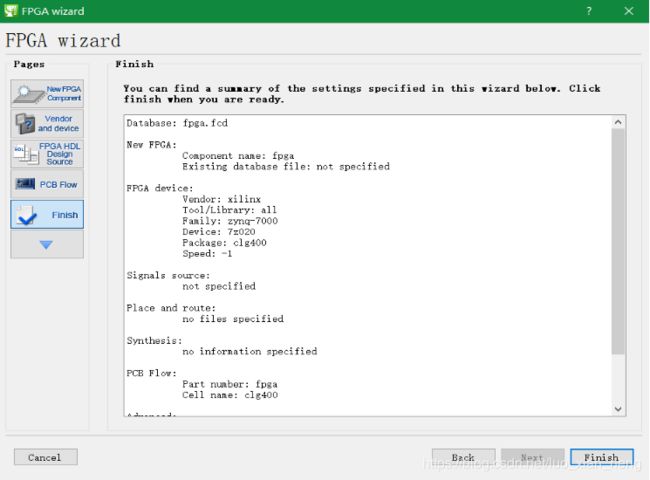

建立FPGA元器件

完成后,显示fpga元件

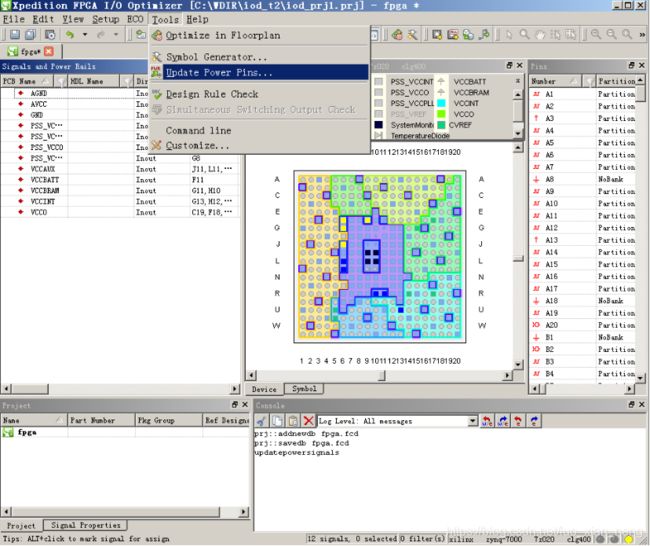

步骤3:分配管脚信号

菜单选择“tools” --> “Update Power pins”给电源管脚自动分配信号

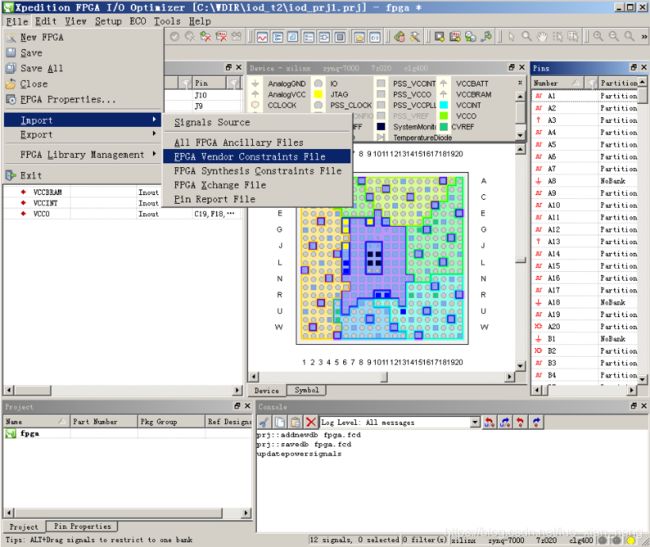

输入Vivado约束文件(或其他数据交换文件)

输入vivado的管脚约束文件,导入信号、管脚配置等信息。

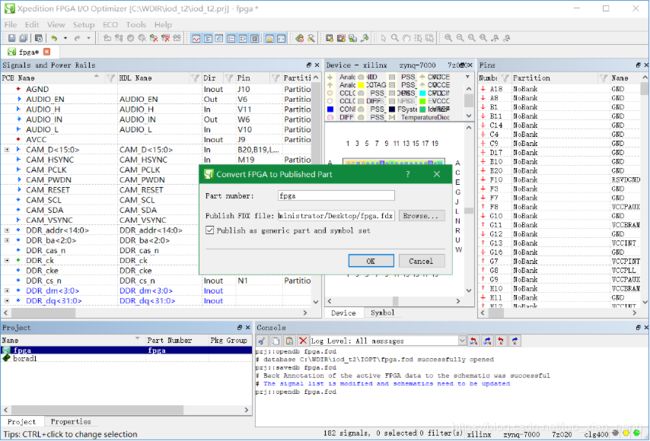

导入vivado信息后,如下图。

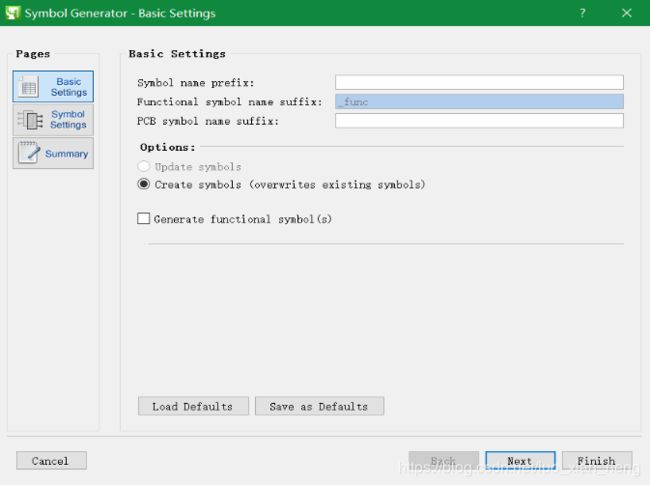

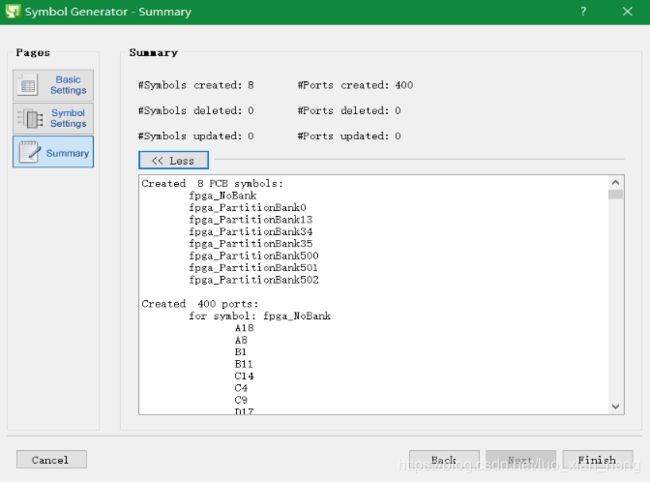

步骤4:生成原理图symbols

步骤5: 将生成的fpga元器件输出到Xpedition Designer原理图

回到Xpedition Designer原理图工具中,将FPGA元器件导入到本地元件库(临时元件库)

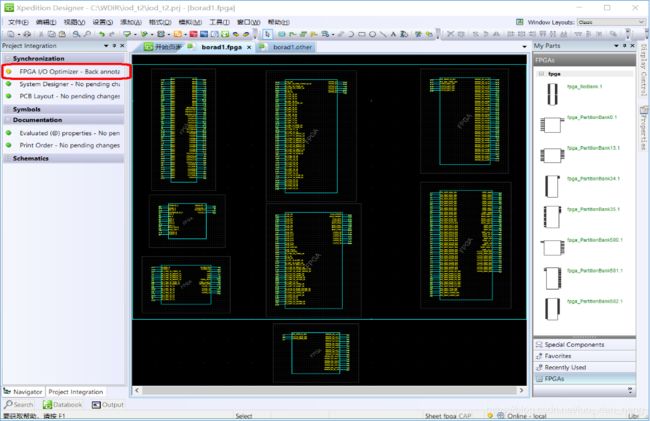

①鼠标点击右下角同步图标,调出“project integration”页面; ②点击“FPGA I/O Optimizer - back annotate”导入fpga器件

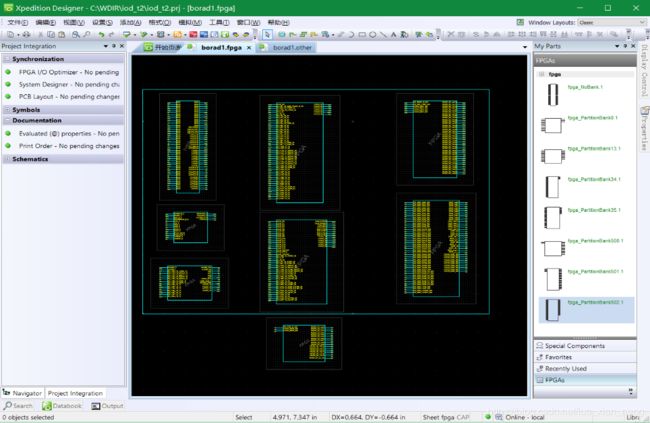

fpga元器件导入到本地临时库中,则“我的元件”中显示对应的symbol,如下图

生成的fpga元件存放在工程目录下的临时库ProjLibs中(如下图),PartsLibs目录存放临时fpga元器件,SymbolLibs目录存放临时fpga的原理图symbol

步骤6:用临时库中的fpga元件sybol设计电路,如下图

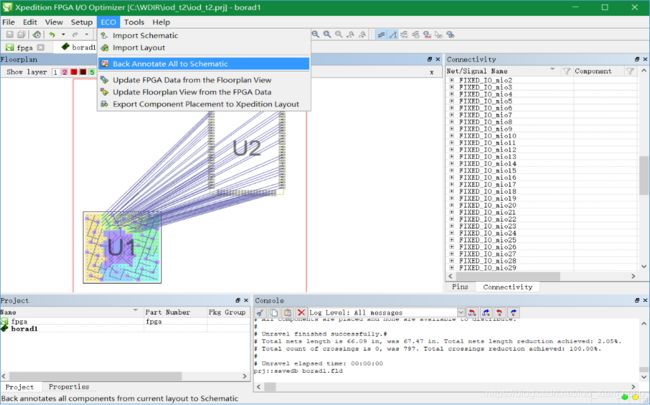

将fpga信号回注到原理图,菜单选择“ECO” --> "Back Annotate all to schematic", 如下图;

Designer中点击同步图标 “FPGA I/O Optimizer - back annotate ...” 回注

回注后的结果如下,引脚生成了网络连线

局部放大图:

点击工具栏“封装”按钮,封装当前设计,为fpga器件分配标号

步骤7:规划布局、布线,优化走线。

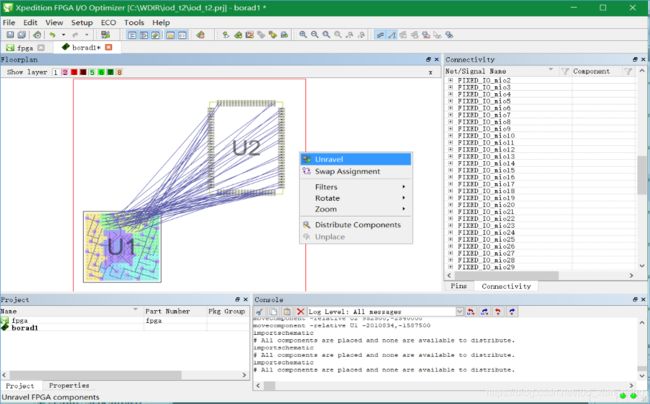

点击“tools” --> “Optimizer in Floorplan”建立布局

移动元器件进行布局规划后,右键鼠标选择“Unravel”进行布线优化

优化后的管脚连线

优化后的管脚连线回注到原理图

进入Designer,点击“FPGA I/O Optimizer - back annotate ...” 回注原理图

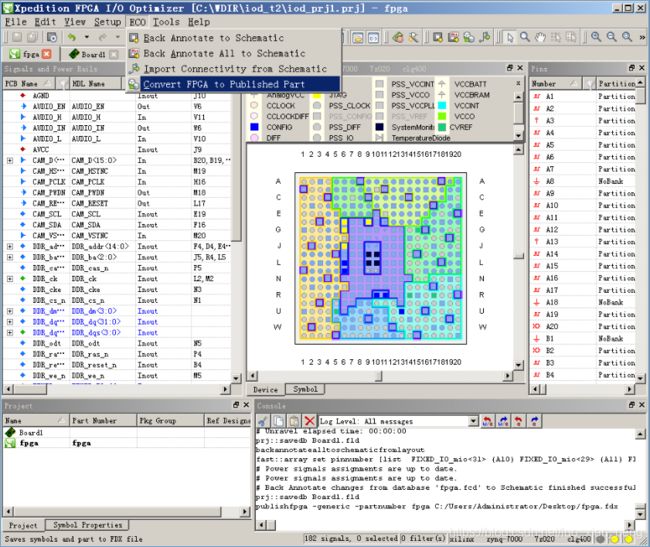

步骤8:优化全部完成后,将临时库中的fpga元件发布到中心库,用于后端PCB设计。

菜单选择“ECO” --> “Convert FPGA to published part”, 输出发布文件.

步骤9:将fpga发布文件导入到中心库

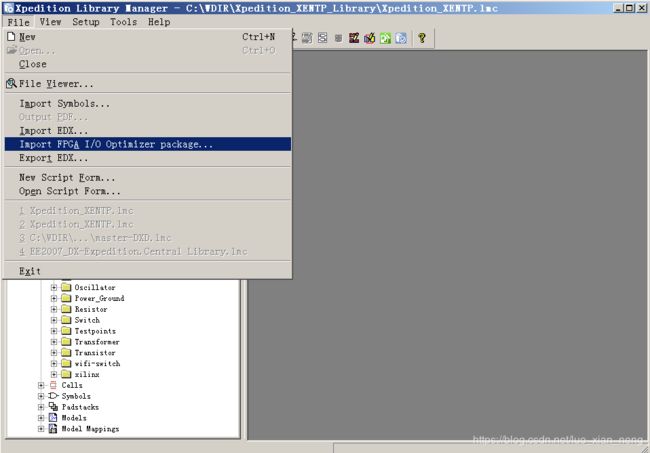

打开Liberary Manager中心库管理工具, 导入发布的fpga元器件(如下图)

选择导入symbols分区、part分区

步骤10:用中心库中fpga元器件设计PCB Layout

(省略)