HDLbits答案更新系列21(4 Verification: Reading Simulation 4.1 Finding bugs in code)

目录

前言

4 Verification: Reading Simulation

4.1 Finding bugs in code

4.1.1 Mux(Bugs mux2)

4.1.2 NAND(Bugs nand3)

4.1.3 Mux(Bugs mux4)

4.1.4 Add/sub(Bugs addsubz)

4.1.5 Case statement(Bugs case)

结语

HDLbits网站链接

前言

今天进入到了第四部分,这部分第一小节的内容比较简单,直接更新吧。

4 Verification: Reading Simulation

4.1 Finding bugs in code

4.1.1 Mux(Bugs mux2)

module top_module (

input sel,

input [7:0] a,

input [7:0] b,

output[7:0] out );

assign out = sel ? a : b;

endmodule这道题目的错误在于a和b都是多比特的数据,而sel信号是单比特的。如果a、b也是单比特,那么可以用修改前的方式。

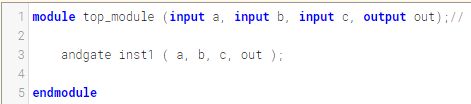

4.1.2 NAND(Bugs nand3)

module top_module (input a, input b, input c, output out);

wire out_1;

andgate inst1 (out_1, a, b, c, 1'b1,1'b1);

assign out = ~out_1;

endmodule这道题第一处错误是端口映射没有将out写在第一位,第二处错误是题目要求完成与非门,作者给出的可引用的module是与门。

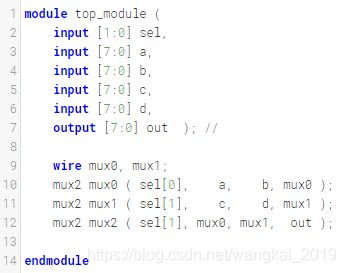

4.1.3 Mux(Bugs mux4)

module top_module (

input [1:0] sel,

input [7:0] a,

input [7:0] b,

input [7:0] c,

input [7:0] d,

output [7:0] out );

wire[7:0] mux0;

wire[7:0] mux1;

mux2 u1_mux2 ( sel[0], a, b, mux0 );

mux2 u2_mux2 ( sel[0], c, d, mux1 );

mux2 u3_mux2 ( sel[1], mux0, mux1, out );

endmodule这道题目中首先mux0和mux1应该定义为8bit,然后实例化的前两个mux应该是sel[0]。

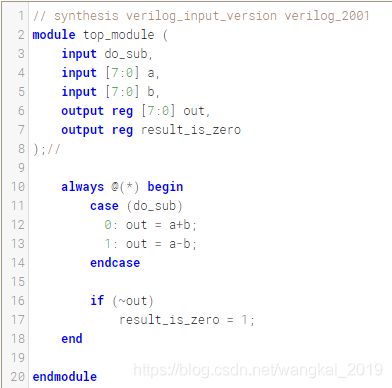

4.1.4 Add/sub(Bugs addsubz)

// synthesis verilog_input_version verilog_2001

module top_module (

input do_sub,

input [7:0] a,

input [7:0] b,

output reg [7:0] out,

output reg result_is_zero

);//

always @(*) begin

case (do_sub)

0: out = a+b;

1: out = a-b;

endcase

if (out == 8'd0)

result_is_zero = 1;

else

result_is_zero = 0;

end

endmodule这道题目要将result_is_zero补充完整。

4.1.5 Case statement(Bugs case)

module top_module (

input [7:0] code,

output reg [3:0] out,

output reg valid

);

always @(*)begin

case (code)

8'h45: out = 0;

8'h16: out = 1;

8'h1e: out = 2;

8'h26: out = 3;

8'h25: out = 4;

8'h2e: out = 5;

8'h36: out = 6;

8'h3d: out = 7;

8'h3e: out = 8;

8'h46: out = 9;

default: out = 0;

endcase

if(out == 4'd0 && code != 8'h45)begin

valid = 1'b0;

end

else begin

valid = 1'b1;

end

end

/*

//second way

always @(*) begin

out = 0;

valid = 1;

case (code)

8'h45: out = 0;

8'h16: out = 1;

8'h1e: out = 2;

8'h26: out = 3;

8'h25: out = 4;

8'h2e: out = 5;

8'h36: out = 6;

8'h3d: out = 7;

8'h3e: out = 8;

8'h46: out = 9;

default: valid = 0;

endcase

end

*/

endmodule这道题给出两种方法,大家看一下就可以了。第一种方法我将valid和out全部写在一个always中,这是不好的,建议大家分开写。

结语

今天更新这个小节吧,应该没有特别难的题目,如果我有代码错误的地方欢迎留言指出哦。

HDLbits网站链接

https://hdlbits.01xz.net/wiki/Main_Page