HDLbits答案更新系列22(4.2 Build a circuit from a simulation waveform)

目录

前言

4.2 Build a circuit from a simulation waveform

4.2.1 Combinational circuit 1(Sim/circuit1)

4.2.2 Combinational circuit 2(Sim/circuit2)

4.2.3 Combinational circuit 3(Sim/circuit3)

4.2.4 Combinational circuit 4(Sim/circuit4)

4.2.5 Combinational circuit 5(Sim/circuit5)

4.2.6 Combinational circuit 6(Sim/circuit6)

4.2.7 Sequential circuit 7(Sim/circuit7)

4.2.8 Sequential circuit 8(Sim/circuit8)

4.2.9 Sequential circuit 9(Sim/circuit9)

结语

HDLbits网站链接

前言

今天这个小节内容算是数字IC工程师的看家本领了,看波形写代码,无论在笔试还是项目中,这都是基本功中的基本功,下面我们就开始吧。

4.2 Build a circuit from a simulation waveform

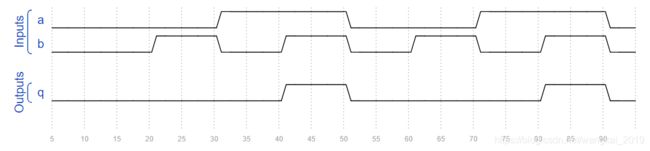

4.2.1 Combinational circuit 1(Sim/circuit1)

module top_module (

input a,

input b,

output q );//

assign q = a & b; // Fix me

endmodule4.2.2 Combinational circuit 2(Sim/circuit2)

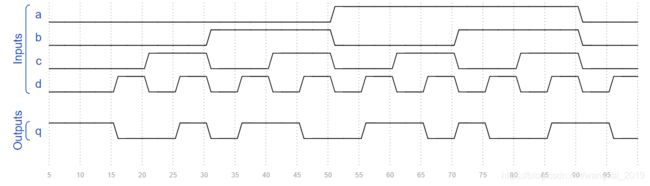

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = ~a & ~b & ~c & ~d | ~a & ~b & c & d | ~a & b & ~c & d | ~a & b & c & ~d |

a & b & ~c & ~d | a & b & c & d | a & ~b & ~c & d | a & ~b & c & ~d;

endmodule画一个卡诺图,答案立马出来。

4.2.3 Combinational circuit 3(Sim/circuit3)

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b & d | b & c | a & d | a & c;

endmodule和上一道题目做法相同,画卡诺图就好。

4.2.4 Combinational circuit 4(Sim/circuit4)

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b | c;

endmodule同理。

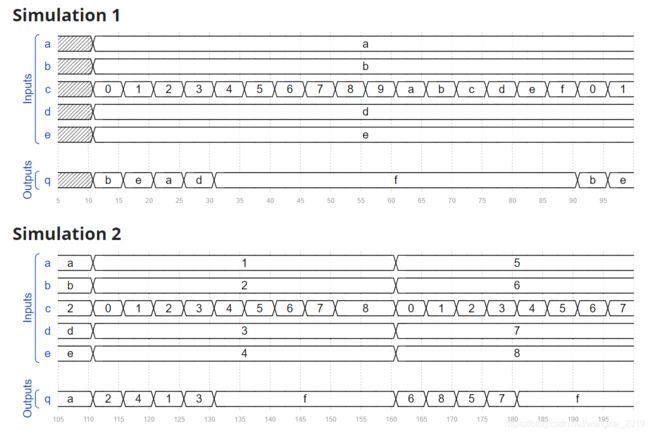

4.2.5 Combinational circuit 5(Sim/circuit5)

module top_module (

input [3:0] a,

input [3:0] b,

input [3:0] c,

input [3:0] d,

input [3:0] e,

output reg [3:0] q );

always@(*)begin

case(c)

0:begin

q = b;

end

1:begin

q = e;

end

2:begin

q = a;

end

3:begin

q = d;

end

default:begin

q = 4'hf;

end

endcase

end

endmodule大家只要将C的值作为判定条件,这道题就容易多了。

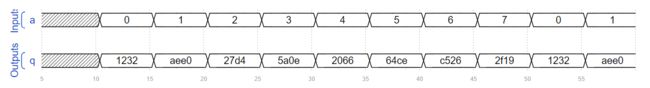

4.2.6 Combinational circuit 6(Sim/circuit6)

module top_module (

input [2:0] a,

output reg [15:0] q );

always@(*)begin

case(a)

0:begin

q = 16'h1232;

end

1:begin

q = 16'haee0;

end

2:begin

q = 16'h27d4;

end

3:begin

q = 16'h5a0e;

end

4:begin

q = 16'h2066;

end

5:begin

q = 16'h64ce;

end

6:begin

q = 16'hc526;

end

7:begin

q = 16'h2f19;

end

endcase

end

endmodule每个a值对应一个q值,这里由于case的所有情况都被囊获进去了,所以我没有写default,还是建议大家补充完整。

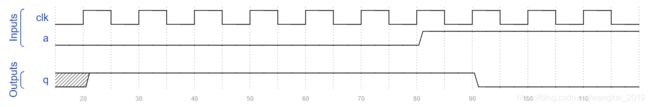

4.2.7 Sequential circuit 7(Sim/circuit7)

module top_module (

input clk,

input a,

output q );

always@(posedge clk)begin

q <= ~a;

end

endmodule4.2.8 Sequential circuit 8(Sim/circuit8)

module top_module (

input clock,

input a,

output p,

output q );

always@(*)begin

if(clock)begin

p = a;

end

end

always@(negedge clock)begin

q <= p;

end

endmodule这道题可能解法不唯一,欢迎大家展示出自己的解法。

4.2.9 Sequential circuit 9(Sim/circuit9)

module top_module (

input clk,

input a,

output [3:0] q );

always@(posedge clk)begin

if(a)begin

q <= 4'd4;

end

else if(q == 4'd6)begin

q <= 4'd0;

end

else begin

q <= q + 1'b1;

end

end

endmodule这道题目是一个计数器,只不过“复位信号”a为1时q为4。

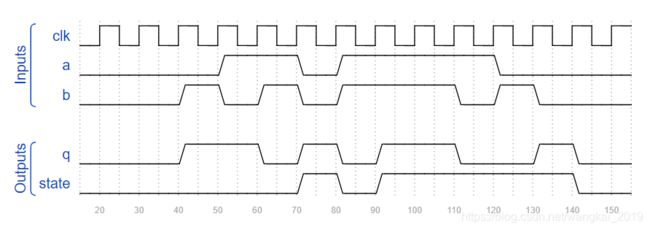

module top_module (

input clk,

input a,

input b,

output q,

output state );

always@(posedge clk)begin

if(a == b)begin

state <= a;

end

end

always@(*)begin

q = a & ~b & ~state | ~a & ~b & state | a & b & state | ~a & b & ~state;

end

//q second way and third way

//assign q = (a == b) ? state : ~state;

//assign q = (a ^~ b) ? state : ~state;

endmodule这道题可能方法不唯一,我想到的是这种方法,大家自己试试吧。

结语

今天更新的这个小节很重要,这是基本功,我也需要继续在这个方面下功夫。希望能和大家一起努力,共同进步~

HDLbits网站链接

https://hdlbits.01xz.net/wiki/Main_Page