#总线#408真题大题系列

【知识回顾】

(1)首先看之前的总结https://blog.csdn.net/qq_35812205/article/details/105588044

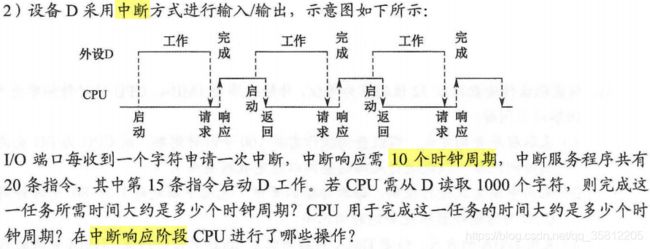

(2)看懂中断图:0.5ms为准备data——10时钟周期CPU相应——20周期CPU执行中断服务程序。

20条指令的中断服务程序中的最后5条开始就是【启动下一次操作】(CPU和外设并行,和传送基本无关)

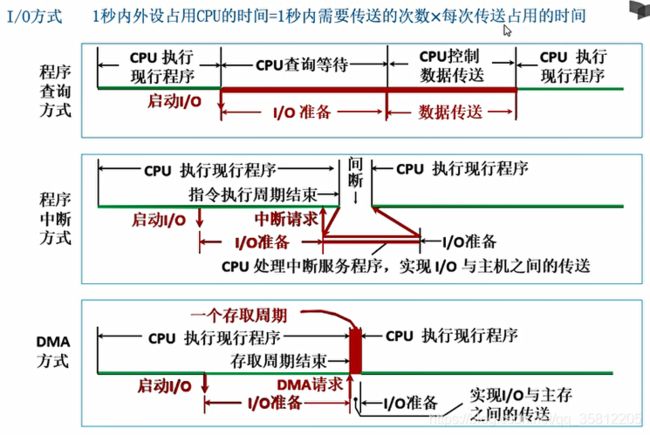

要区分【传送数据的时间】和【占用CPU的时间】(第三题)。

(3)中断响应阶段即隐指令——CPU操作:(1)关中断(2)保护断点(3)引出中断服务程序。

【真题】

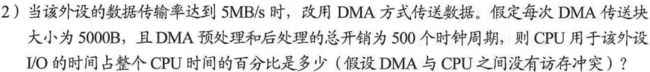

第一题(2009常规题):

第一问:中断

由数据传输率和传输单位为32位=4B知每秒传送0.5MB/4B=125K次(即每秒中断次数)。

所以百分比R1=125K×(2+18)×5 / 500M=2.5%

第二问:DMA

和(1)同理每秒DMA次数为5MB / 5000B=1000次(即每秒DMA次数)。

所以百分比R2=1000×500 / 500M=0.1%

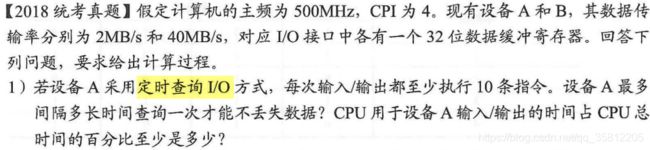

第二题(2018三种I/O方式):

第一问:定时查询

【程序定时查询】CPU向缓存端口查询数据,由于缓存端口大小有限,必须在传输完端口大小的数据时访问端口,以防部分数据未被及时读取而丢失。

设备A准备32位数据所用的时间为4B / 2MB/s=2μs,所以最多每隔2μs必须查询一次,每秒的查询次数至少是1s/2μs=5×10^5 次,

每秒CPU用于设备A输入/输出的时间至少为5×10^7 /500M=4%。

【注意】主频:机器内部主时钟的频率,时钟周期的倒数。

第二问:中断

【解析】如果按照常规计算会发现CPU时间占比“大于”1(不可能)。

若正常进行,每秒中断次数为2MB/4B *400个时钟周期,而CPU每秒只有500M个(小于前者)时钟周期,即准备数据的时间小于中断响应和中断处理的时间,数据会被刷新,造成丢失,因此B不适合用中断I/O方式。

第三问:DMA(送分题)

【解析】每秒的DMA次数最多为40MB/1000B=40000次,

CPU用于B输入/输出的时间最多为40000×500=2×10^7个时钟周期,

所以占比=2×10^7 / 500M=4%.

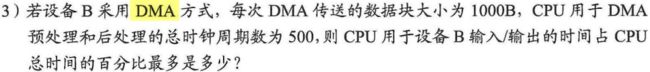

第三题(2016程序中断):

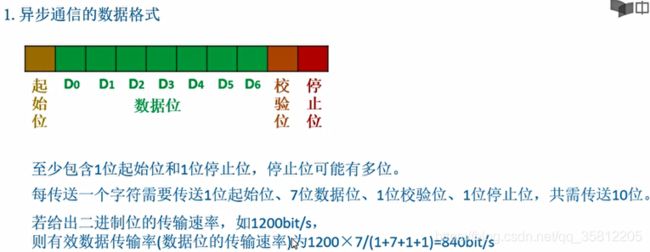

第一问:异步串行

【解析】传送一个ASCII码字符需要(1个起始位+7个数据位+1个奇校验位+1个停止位)=10位。

每0.5ms送入1个字符,所以每秒送入1s/0.5ms=2000个字符。

【注意】异步串行通信至少包含1位起始位和1位停止位(停止位可能有多位,奇校验位可选,本题是有的)。

第二问:中断细节过程

【解析】首先注意审题【求的时间单位是“时钟周期数”(分别换成时钟周期数再相加)】。

(1)一个字符传送时间=T设备D将字符送I/O端口+T中断响应+T中断服务程序前15条指令。

时钟周期=1/50MHz=20ns,

设备D将字符送I/O端口的时间为0.5ms/20ns=2.5×10^4个时钟周期;

一个字符的传送时间=2.5×10^4+10+15×4=25070个时钟周期。

完成1000个字符传送用时=1000×25070=25070000个时钟周期。

(2)CPU用于该任务的时间(上图绿色部分)约为1000×(10+20×4)=9×10^4 个时钟周期。

【注意】20条指令的中断服务程序中的最后5条开始就是【启动下一次操作】(CPU和外设并行,和传送基本无关),

要区分【传送数据的时间】和【占用CPU的时间】。

(3)中断响应阶段——CPU操作:(1)关中断(2)保护断点(3)引出中断服务程序。

2016总结

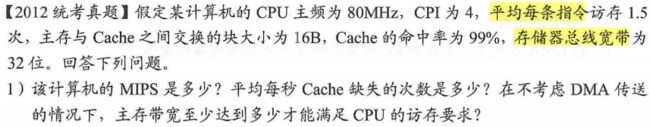

第四题(2012总线+访存)

PS:注意下面题目第二行的“存储器总线带宽”要改为“存储器总线宽度”(指存储器每次并行传输的位数是32位)。

第一题(MIPS、Cache缺失次数、主存带宽):

首先明确题目的【访存】指“访问Cache-主存体系”;MIPS:每秒可执行多少百万条指令。

平均每秒CPU执行的指令数=80M/4=20M,即MIPS=20.

因为平均每条指令访存1.5次,因此共访存20M×1.5次,

因为Cache的命中率为99%,因此平均每秒Cache缺失20M×1.5×(1-99%)=300K次。

每次Cache缺失都要调入整个主存块(16B),所以主存带宽至少为300K×16B=4.8MB/s

【注意】题目问的“至少”(因为实际中可能CPU访存时缺失时,需要主存同时调块给主存和Cache;而且如果考虑DMA,DMA也需要访存,使得主存带宽会更大)。

另外:和https://blog.csdn.net/qq_35812205/article/details/107843966第三问不太一样。

**********做题要感受出每小问之间的联系**********

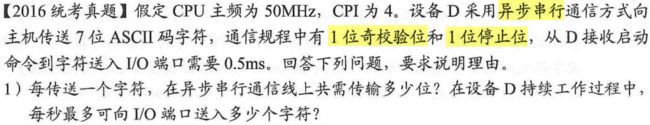

第二题(缺页异常、周期挪用):

【审题】“磁盘I/O接口的数据缓冲寄存器为32位”指【外设没准备好 或 接收完数据缓冲寄存器中的32位数据时,由I/O接口发出DMA请求】。

【解析】因为平均每秒Cache缺失次数(即访问内存/页次数)为300K次,所以300K×0.0005%=1.5次缺页/s

外设没准备好或接收完数据缓冲寄存器的32位=4B数据时,由I/O接口发出DMA请求,所以请求次数为1.5×4KB/4B=1.5K=1.5×1024=1536次。

【注意】

(1)访问Cache缺失后访问主存如果又缺失(缺页),此时要访问磁盘调块(一般常规题只指访问TLB缺失后访问页表后【页面缺失】后要从【磁盘】调页面)。

(2)【周期挪用】DMA每准备好一个数据,就向CPU发出DMA请求(让CPU让存储器的总线让出),DMA传送完数据后再交还总线给CPU。

第三问(DMA优先级):

(3)CPU和DMA控制器同时要求使用存储器总线时,哪个优先级更高?why

【解析】CPU和DMA控制器同时要求使用存储器总线时,DMA请求的优先级更高。

因为DMA请求若不能及时地得到相应,I/O传输数据可能会丢失。

【注意】使用DMA传输方式的一般都是高速设备,如果不及时的相应使数据被刷新。

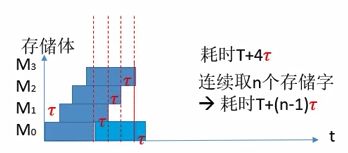

第四问(四体低位交叉):

(4)为了提高性能,主存采用4体低位交叉存储模式,工作时每1/4个存储周期启动一个体,若每个体的存储周期为50ns,则该主存能提供的最大带宽为多少?

【解析】最大带宽为4×4B/5ns=320MB/s。

【注意】题目问的是“最大带宽”(即值流水线充分流动起来的情况即【每隔1/4个存储周期就能存储一个字】,而不是考虑一开始情况),一个字一般取为存储器总线宽度/数据线根数(本题为32位);或者认为四个存储体并行地工作。

总结

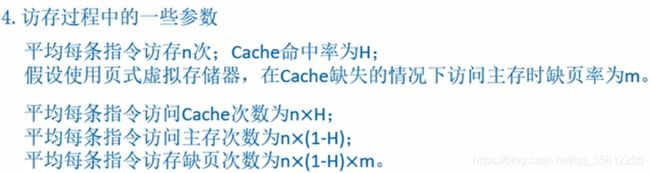

【注意】下图中如果不是“在Cache缺失的情况下访问主存时缺页率为m”,而是直接给出“访问主存时缺页率为m”,则要要计算【平均每条指令访存缺页次数】=n×m。