ICC图文流程——(五)布线Route

ICC绕线阶段

主要任务:完成标准单元的信号线的连接,布线工具会自动进行布线拥塞消除、优化时序、减小耦合效应、消除窜扰、降低功耗、保证信号完整性等问题。

首先先介绍一下基于格点的布线理论

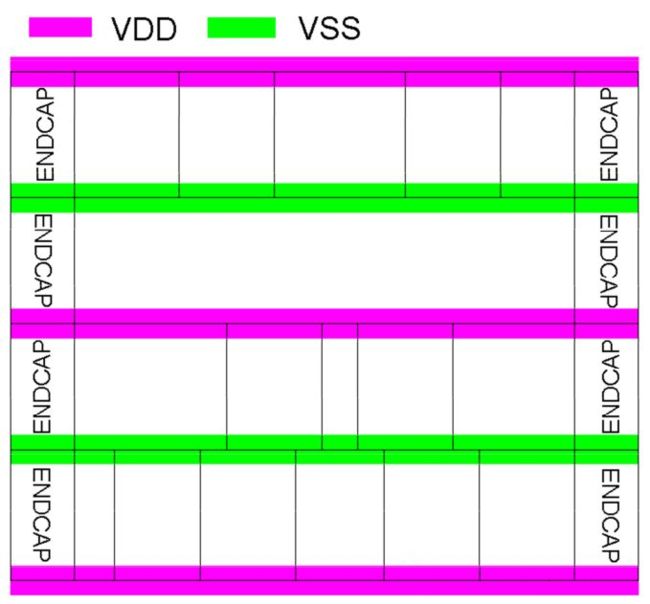

标准单元的高宽都被设计为为pitch的整数倍,因此其pin都可以放置在Grid Point上,为布线作准备。并且他们的高度都被设计成相同高度,这样可以整齐地放在rail上,这在placement阶段已经介绍过。

绕线阶段的命令为route_opt,该命令包含了布线阶段的三个部分:

·Global routing(全局布线)

·Track assignment (布线通道分配)

·Detail routing (详细布线)

其中Detail routing 又分为Detail routing 和Search and Repair (布线修补)

接下来一一介绍

·Global routing (全局布线)

全局布线Global routing,简称GR。它对整块芯片的走线做布局规划,并没有进行任何实际的走线(not lay down any metal traces)

GR会为指定的金属层和Gcells分配线路。

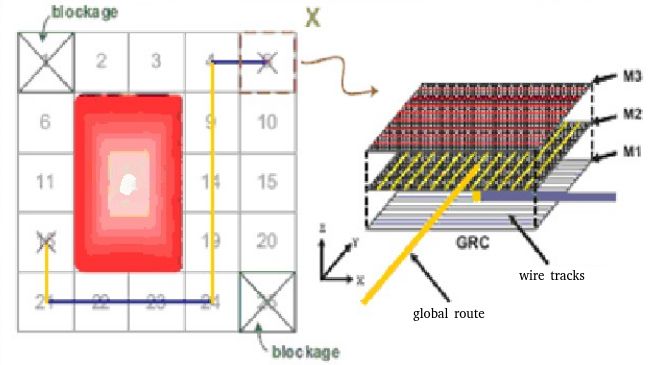

Gcell:全称global routing cells,也叫GRC,同样的它也是我们定义的一种grid, G cell grid对routing过程中起着相当重要的作用。

在floorplan阶段时,关于congestion(拥塞)的解释时已经提及GRC。

它定义在Lef或者floorplan文件(.def)中,当然初始时工具会根据设计和tech lef中情况自动生成.如下图所示,左侧为lef文件中关于GRC定义的解释,右侧为lef文件中GRC的定义格式举例。

产生的GRC grid如下所示

右图为一个GRC中的示例图,如图所示,一个GRC中包含了15条tracks(通常一个gcell中会占有10几个track,根据design的不同有所变化),其中由于wires或OBS(route blockage)等被占用9条而其余6条属于可使用。global routing的目标是使得每个gcell的容量占有率在85%左右。

global route以gcell cell作为绕线参考网格,工具在绕线时会试图寻找gcell中的最短path。在global route时,软件只知道起点和终点,可以简单理解为两个具有连接关系的pin。但是不知道如何从起点走到终点。

但是GR会避开拥塞高以及blockages和P/G(rings/straps/rails)等区域,这样就能大概的设计出一个走线的大致路径。

但是GR只是进行了设计而并没有将线之间进行首尾连接,。如图为进行了GR,图中这些线代表了工具确定的大体位置及走向,但没有实际具有宽度的连线,不同的颜色代表了不同线层,并且给出孔的位置。

GUI>Route>Global Route

·Track Assignment(布线通道分配)

GR是基于gcell的分析,主要是分配绕线资源,根据global routing结果可以看看congestion情况,就是总体看绕线资源是否足够,是否合理,它并没有将绕线分配到具体的track上。

而布线通道分配将GR设计的每一连线分配到一定的track上,并且对连线进行实际布线,这个阶段不做DRC检查。

如上图所示,左图是GR形成的net,并没有首尾连线,而经过经过track assignment后,形成右图完整的net。并且,在track assignment阶段,布线尽可能走长直的金属连线,但同时会减少孔的个数。为了减少孔的个数,会形成jog(小范围地改变布线方向,如下图所示)。

TA阶段不做DRC的检查,即走线会产生许多DRC:Wire spacing;Wire width;Via rules(size;density;stackable etc..)

由Detail Route修复

·Detail Route(详细布线)

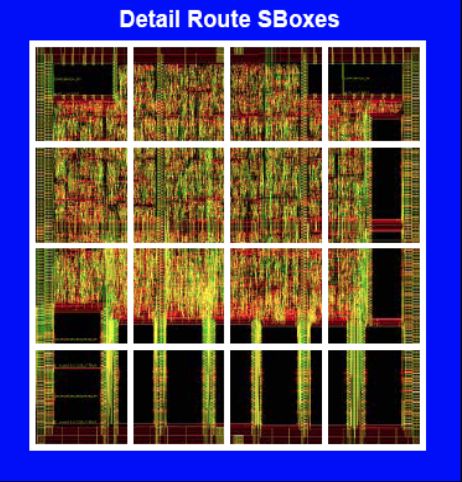

Detail route的工作主要将TA产生的DRC violation移除。方法:使用固定尺寸的switch box(sbox)来修复违规。

Sbox是整个版图平均划分的小格子,工具对每一个小格子内部的DRC进行修复,但是边界上的DRC修复不了。

Sbox由GRC构成,每个Sbox边缘会重叠一个GRC宽度(Sbox由GRC组成,两个sbox交叠的宽度为一个GRC的宽度)。

·Search and repair(布线修补)

通过逐渐增大Sbox的尺寸寻找和消除Detail routing中没有完全消除的DRC违规。

然后介绍一下布线的流程

·布线前检查

·检查设计中的违规,主要检查经过CTS的设计还是否存在setup hold违例等

icc_shell>report_constraint -all

·检查设计是否存在理想网络和高扇出,若存在,在route之前将他们修复

icc_shell>all_ideal_nets

all_high_fanout -nets -threshold 501 (扇出大于501pf就列出)

·确认布线方向

icc_shell>report_preferred_routing_direction

一般来说,奇数层横向走线,偶数层纵向走线。

·确认TLUPlus文件已经加载

icc_shell>report_tlu_plus_files

·检测当前设计合理性,该命令用与检测当前设计的placement是否合理,输出违规报告

icc_shell>check_legality

检测:

1. 标准单元是否在row上

2. 标准单元是否相互重叠

3. 标准单元是否与blockages交叉

4. 标准单元所摆放的row上存在不允许的方向的标准单元

5. Cells with a core site type not equal to that of the row on which cells are placed

(根据我的理解是边缘处结构和中间结构不一致,将使得芯片边缘处标准单元的时序和中间标准单元不一致。这涉及到floorplan阶段添加的EndCAP cell,在28 nm以及更小尺寸的工艺中才需要添加。

为了保证栅以及氧化层的一致性,需要在标准单元Row两端放置EndCAP,用来保证两边的标准单元左右环境的一致性。避免在光刻时,由于最两端标准单元左右环境的不一致导致其性能有所差异。

库中定义的时序的值一般都是常规情况下(也就是芯片中间)的标准单元的时序。因而,如果不加Endcap的话,那么边缘处的标准单元的时序便和库中定义的值有一定的出入,而工具是无法考虑该现象的。因此PR工具或者STA工具分析的结果便于流片后测试的结果有出入。严重的话可能会导致芯片Fail掉。)

6. 标准单元是否和电源线重叠

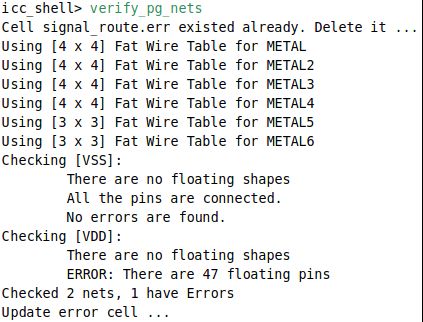

·检查所有电源和接地引脚是否物理连接到P/G网络(查看是否有悬空)

icc_shell>verify_pg_nets

查看设计中是否存在floating pin,特别是MTCMOS是否存在floating的global vdd。对于结果报告,需要我们能够分辨出哪些是真错,哪些是假错(或者说不用关心的错误),比如floating shape的错误就可以完全不用管

结果显示有floating pins没有连接到VDD上

通过GUI>Verification>Error Browser 选择Rail(该问题为P/G problem),右边![]() 按钮选择当前design

按钮选择当前design

通过Error Browser,我们可以在设计的layout window上定位我们出现的error

通过view setting分析,被highlight标注的标准单元引脚缺少了VDD rail,导致VDD连接断开,使得它们成为floating pins

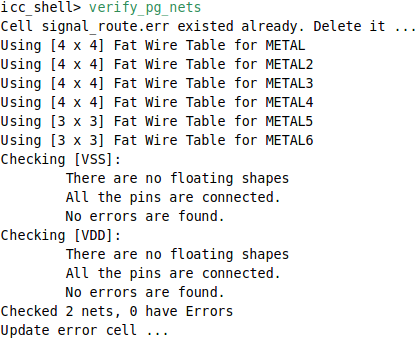

icc_shell>preroute_standard_cells -remove_floating_pieces

生成VDD rail,移除悬空,重新检查电源地的连接

重新检查 error已经被修复

布线前检查完成,进行布线和优化

·实施布线

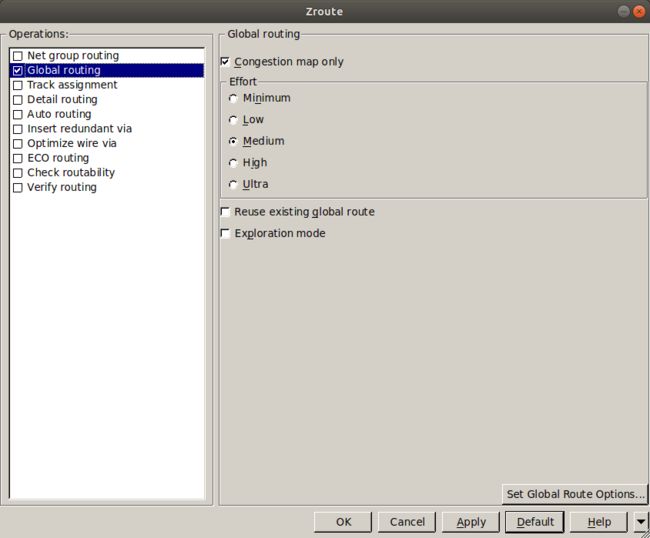

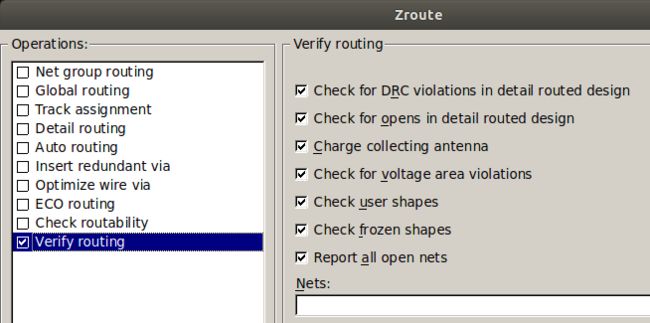

ICC布线分为两种布线模式,传统route方法和Z route模式。

Z route是对传统基于格点的布线模式的延伸,线可以不用非得沿着格点进行布线,能有效解决DRC的违反。现在基本上都使用Z route模式。

icc_shell>get_route_mode_options -zroute 返回为true

若返回为false

icc_shell>set_route_mode_options -zroute true 或者GUI>Route>Zroute Mode

·加载天线效应文件

icc_shell>source xxx_antenna.tcl (Astro使用.clf ICC使用.tcl)

左图所示为.clf文件内容,右图为.tcl文件格式,可根据语法自行编写

设置布线过程中考虑天线效应 icc_shell>set_route_zrt_detail_options -antenna true

关于天线效应的内容放在下一章chip-finishing内具体介绍,一般流程会将其放在最后的DFM中进行DRC修复,但是在布线前考虑天线效应文件有助于设计的进行

·允许插入冗余通孔;使设计中的冗余通孔随布线更改保持最新

Icc_shell>set_route_zrt_common_options -post_detail_route_redundant_via_insertion medium

set_route_zrt_detail_options -optimize_wire_via_effort_level medium

·对布线进行设置

使用set_route_zrt_*_options可以对布线进行设置 (*=common;global;track;detail)

设置完毕后进行确认检查非默认布线规则、布线设置

Icc_shell>report_routing_rules;

report_route_opt_strategy;

report_route_zrt_common_options;

report_route_zrt_global_options;

report_route_zrt_track_options;

report_route_zrt_detail_options;

·进行初始布线

icc_shell>route_opt -initial_route_only

该命令包括了全局布线、路线分配和详细布线。若设计规模很大,可分布执行,通过

GUI>Route>Global Route/Track Assignment/Detail Route分步执行

report_clock_tree -summary;report_clock_timing -type skew;report_qor

report_constraint -all

有max_transition的violation 继续进行优化布线,解决违规

icc_shell>route_opt -skip_initial_route -power 同时进行功耗的优化

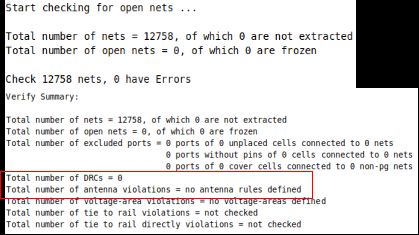

·布线后检测

icc_shell>verify_zrt_route 检查DRC错误

能够判断设计DRC是否被修复 是否具有天线效应

GUI>Verify Route

若存在违反,输入命令

icc_shell>route_zrt_detail -incremental true -initial_drc_from_input true 进行修复

·检查LVS(Layout Versus Schematics)是否通过 (在calibre验证LVS前,应ICC能先通过LVS)主要检查design中的short和open。

icc_shell>verify_lvs

icc_shell>report_design_physical -route报告完整route物理设计

保存设计save_mw_cel -as route_opt_final