sja1000 CAN控制器波特率计算方法详解

这段时间调试公司处理器can总线,实现最基本的对发实验,can控制器是sja1000,起初因为是对发实验,同样2块开发板,同样内核配置相同,因此时钟以及波特率肯定一样,也没有仔细研究can的时钟以及波特率,今天有客户问can控制器的时钟以及波特率,下午仔细看了一下sja1000手册,并且写了一个由波特率和时钟来计算分频值的小程序,这里总结一下。

sja1000 can工作频率和波特率之间分频值寄存器是6号和7号寄存器 ,datasheet上对这2个寄存器说明如下

6.5 Common registers

6.5.1

BUS TIMING REGISTER 0 (BTR0)

The contents of the bus timing register 0 defines the values of the Baud Rate Prescaler (BRP) and the Synchronization

Jump Width (SJW). This register can be accessed (read/write) if the reset mode is active.

In operating mode this register is read only, if the PeliCAN mode is selected. In BasicCAN mode a ‘FFH’ is reflected.

Table 44 Bit interpretation of bus timing register 0 (BTR0); CAN address 6

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

SJW.1 SJW.0 BRP.5 BRP.4 BRP.3 BRP.2 BRP.1 BRP.0

6.5.1.1

Baud Rate Prescaler (BRP)

The period of the CAN system clock tscl is programmable and determines the individual bit timing. The CAN system clock

is calculated using the following equation:

tscl = 2 × tCLK × (32 × BRP.5 + 16 × BRP.4 + 8 × BRP.3 + 4 × BRP.2 + 2 × BRP.1 + BRP.0 + 1)

where tCLK = time period of the XTAL frequency = 1/ f XTAL

6.5.1.2

Synchronization Jump Width (SJW)

To compensate for phase shifts between clock oscillators of different bus controllers, any bus controller must

re-synchronize on any relevant signal edge of the current transmission. The synchronization jump width defines the

maximum number of clock cycles a bit period may be shortened or lengthened by one re-synchronization:

tSJW = tscl × (2 × SJW.1 + SJW.0 + 1)

6.5.2

BUS TIMING REGISTER 1 (BTR1)

The contents of bus timing register 1 defines the length of the bit period, the location of the sample point and the number

of samples to be taken at each sample point. This register can be accessed (read/write) if the reset mode is active.

In operating mode, this register is read only, if the PeliCAN mode is selected. In BasicCAN mode a ‘FFH’ is reflected.

Table 45 Bit interpretation of bus timing register 1 (BTR1); CAN address 7

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

SAM TSEG2.2 TSEG2.1 TSEG2.0 TSEG1.3 TSEG1.2 TSEG1.1 TSEG1.0

首先看寄存器6BTR0

datasheet说明BTR0决定了BRP和SJW,复位模式下可读可写,对于BRP其中给出了关键的计算公式

tscl = 2 × tCLK × (32 × BRP.5 + 16 × BRP.4 + 8 × BRP.3 + 4 × BRP.2 + 2 × BRP.1 + BRP.0 + 1)

tscl代表的是can控制器系统时钟的一个周期长度,tCLK是外部所供时钟周期,

32 × BRP.5 + 16 × BRP.4 + 8 × BRP.3 + 4 × BRP.2 + 2 × BRP.1 + BRP.0是不关心SJW2位的BTR0寄存器的值,只不过是把二进制做了十进制转换而已。

说明一点,can控制器将外部时钟做如上运算出的系统时钟是can控制器的采样时钟,can内部必须要工作在一个远高于波特率的采样时钟下,这样对传送进来的每位数据才能进行多次采样确定数据的高低。这里的tscl就是can控制器内部的采样时钟。

Synchronization Jump Width是同步跳转宽度。同步跳转宽度定义了一个位周期可以被一次重新同步缩短或延长的时间份额Tq(见下面对BPR5-BPR0的说明)的最大数目,以便在数据发送时与总线同步。SWJ1、SWJ0决定同步跳转宽度。从给出的公式看出同步跳转宽度是tscl的BTR0高2位+1倍。

再来看BTR1寄存器

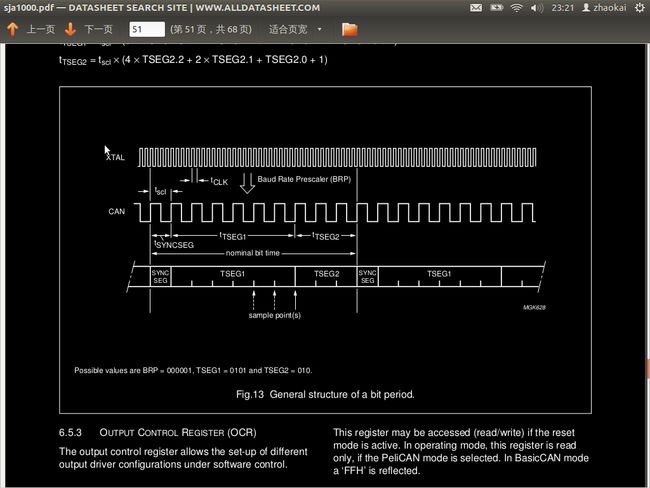

BTR1定义了数据位宽度以及采样点,对于BTR1各位和数据位宽度的关系需要看datasheet给出的General structure of a bit period图。如下:

有图可以看出外部时钟XTAL 内部采样时钟FSCL 波特率之间的关系。外部时钟和内部采样时钟的计算公式前面已经说明了,从图中可以看到

一个normal bit time是SYNCSEG + TSEG1 + TSEG2,而datasheet上也给出了这几个值的计算公式如下:

tSYNCSEG = 1 × tscl

tTSEG1 = tscl × (8 × TSEG1.3 + 4 × TSEG1.2 + 2 × TSEG1.1 + TSEG1.0 + 1)

tTSEG2 = tscl × (4 × TSEG2.2 + 2 × TSEG2.1 + TSEG2.0 + 1)

a normal bit time代表了一个数据位的时间宽度,设波特率为baud,这个时间宽度就是1/baud。

所以 1/baud = (3 + TSEG1 + TSEG2)x tscl

TSEG1代表是BTR1寄存器的低4位,TSEG2是BTR1寄存器的4,5位二进制数的值

BTR1最高位代表了每次抽样的抽样点数,计算波特率我们先不关心。

这样结合前面BTR0寄存器计算公式说明我们就可以得出外部时钟和波特率之间的关系公式,这前后其实就是通过tscl内部采样时钟来连接起来的 如下:

1/baud = (3 + TSEG1 + TSEG2)x 2 x(1/fxtal)x(BTR0 + 1)

====》

baud = FXTAL / ( 2 x (BTR0 + 1)x (TSEG1 + TESG2 + 3))

说明:BTR0代表BTR0寄存器低6位的值,TSEG1代表BTR1寄存器低4位的值,TSEG2代表BTR1寄存器中4 5位二进制数的值