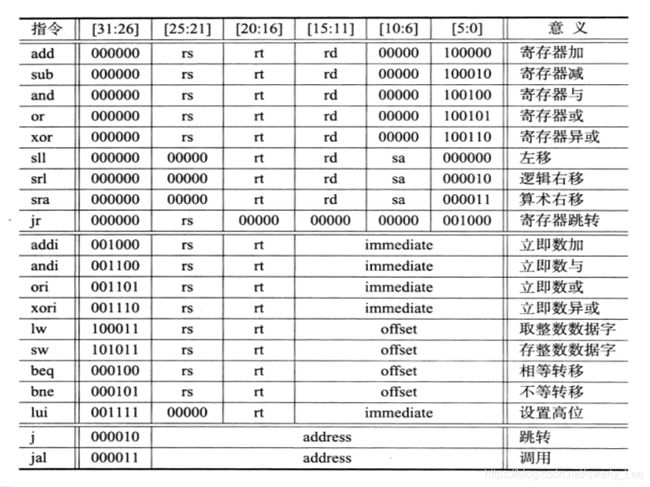

暑期实训CPU设计(三)

今天先详细的描述一下MIPS的20条指令,各控制信号,验证自己做的数据通路图

1.取值功能的数据通路

首先PC寄存器输出的32位地址码,要作为指令存储器的地址码输入,如果考虑PC+4,还需要从PC的输出端连接到加法器的输入端,另一端是常数4,加法器的运算结果是PC+4,PC+4会更新PC,所以它会和PC输入端连接。

2.R型运算指令 (5条 add sub and or xor )

操作码op全为0,需要靠功能说明字段func确定操作类型

例如:add rd,rs,rt #R[rd]->R[rs]+R[rt]

操作码和功能说明字段输入到控制单元,控制单元产生控制信号,在读取寄存器堆的时候需要有两个寄存器的编号rs rt,rs rt分别连接到寄存器堆的两个地址输入端口,根据两个地址就可以读出两个数据,这两个数据要送到ALU做加法运算,ALU运算得到一个结果,运算的结果要写回寄存器堆,目标地址来源于rd,rd连接到寄存器堆的地址写入端口,要写入的话还需要控制单元产生一个高电位的写使能信号,然后在时钟信号的驱动下,数据才能真正写入寄存器堆。ALU的输出端连接到寄存器堆的数据输入端WD。Alu做运算还需要控制单元产生一个控制信号aluc连接到ALU的控制端口。

3.R型移位指令(3条 左移,逻辑右移,算数右移)

例如:rd <- rt << sa

操作码和功能说明字段输入到控制单元,控制单元产生控制信号,说明是逻辑右移还是算数右移,sa,rt这两个数据要送到ALU做移位运算,后面结果写入寄存器堆同上(下划线)。

4.I型运算指令(4条 addi andi ori xori )

例如:addi rt,rs,imm #R[rt]<-R[rs]+E(imm)

I型运算指令涉及到把16位立即数扩展为32位的操作,需要扩展器(只有addi是符号扩展,其他是零扩展,加的话涉及溢出所以符号扩展,其他则不会溢出。符号扩展负数高16位全部为1,正数全部为0,)。指令当中的立即数经过扩展输入到ALU的B端口,rs输入到寄存器堆的地址输入端口,读出数据后,连接到ALU的A端口,两者做运算,后面结果写入寄存器堆同上(下划线)。注意,数据在写入到寄存器堆的时候,目标地址是rt。

5.I型访存指令(2条)

lw rt,imm(rs) #R[rt]<-Mem[R[rs]+E(imm)] 访问:从数据存储器中读数据

需要增加一个数据存储器,存储器需要读模式和写模式的控制信号。指令当中的立即数经过扩展输入到ALU的B端口,rs输入到寄存器堆的地址输入端口,读出数据后,连接到ALU的A端口,两者做加法运算,得到一个目标地址,需要根据目标地址访问数据存储器,所以Alu的输出要和数据存储器的地址输入端口连接。数据存储器RD端口输出一个数据,写回Rt寄存器。数据要写回寄存器堆,目标地址来源于rt,rt连接到寄存器堆的地址写入端口,要写入的话还需要控制单元产生一个高电位的写使能信号,然后在时钟信号的驱动下,数据才能真正写入寄存器堆。

sw rt,imm(rs) #Mem[R[rs]+E(imm)]->R[rt] 存储:把数据写入数据存储器中

指令当中的立即数经过扩展输入到ALU的B端口,rs输入到寄存器堆的地址输入端口,读出数据后,连接到ALU的A端口,两者做加法运算,得到一个目标地址。rt连接到寄存器堆的地址输入端口,读出数据,这个数据需要写入到数据存储器,所以B端口应连接数据存储器的数据输入端口WD。这样根据上面得到的目的地址,把数据写入数据存储器。

6.I型分支指令(2条)

例如:beq rs,rt,offset #if R[rs]==R[rt]

#then PC<-PC+4+E(offset)<<2

#else PC<-PC+4

bne不等时转移

需要增加一个左移两位器和一个加法器。首先根据rs rt读取两个操作数,这两个操作数在ALU中做减法运算,产生一个0标志位,o标志位作为控制单元的输入信号,如果0标志位为1则表示两个操作数是相等的,PCsource=01,就要进行分支,通过PC相对寻址的方式产生分支地址。offset立即数扩展,左移两位后连接到加法器的A端口,PC+4连接B端口,两者相加得到分支的目标地址,这个目标地址要去更新PC寄存器,所以加法器的结果要和PC寄存器的输入端连接。操作数不相等,PCsource=00,直接用PC+4更新PC寄存器。

7.J型指令(3条)

j跳转指令:j,address #PC<-(PC+4)[31:28] U (address<<2)

# goto address

需要增加一个左移两位器和拼接器。把指令中的26位地址码,输入到左移两位器,26位变28位,和PC+4的高四位拼接。拼接的结果就是转移指令的目标地址,PCsource=11,然后这个目标地址去更新PC寄存器。

jal调用指令:j,address #PC<-(PC+4)[31:28] U (address<<2)

# $31<-PC+4;

# goto address

跳转到某个地址后,同时把返回调用点的地址保存在r31寄存器中

jr指令

jr rs #PC <- rs

# goto rs

跳转到某寄存器。根据RS读出数据,这个数据作为跳转的目标地址,PCsource=10,然后这个目标地址去更新PC寄存器。

8.最后一条I型指令lui

lui rs,0

imm16位扩展至32位,送入alu,alu取高16位,低位填零补全32位,将结果回填Rs寄存器

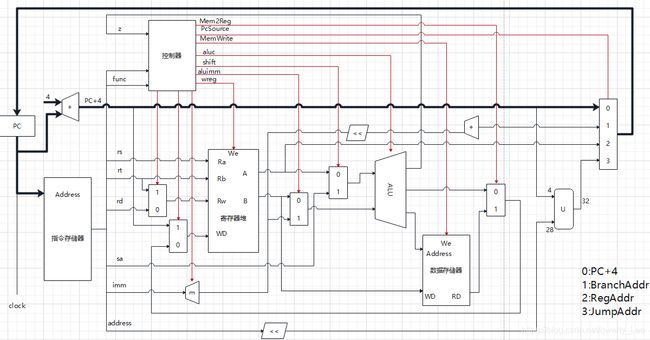

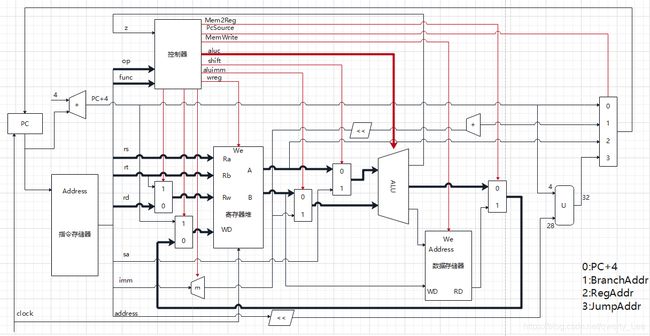

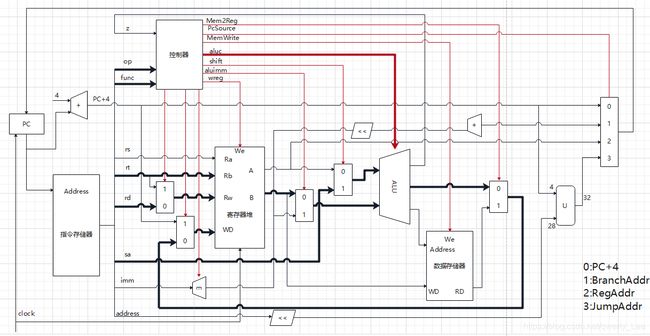

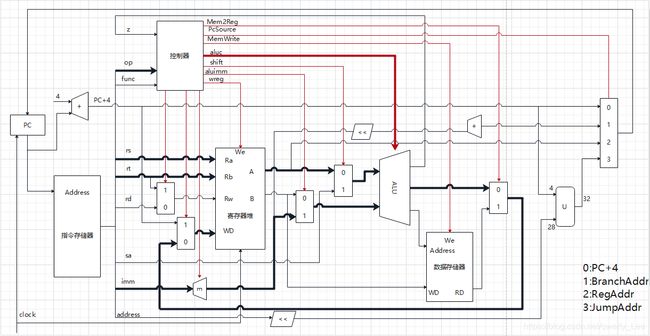

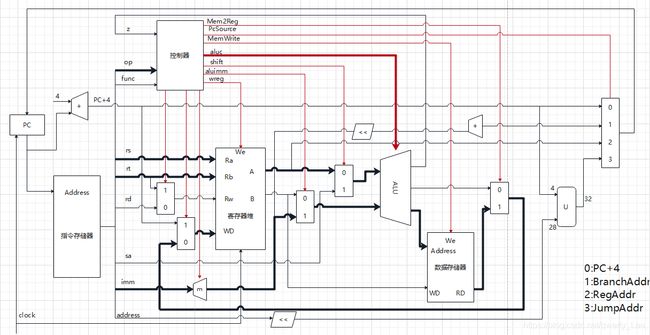

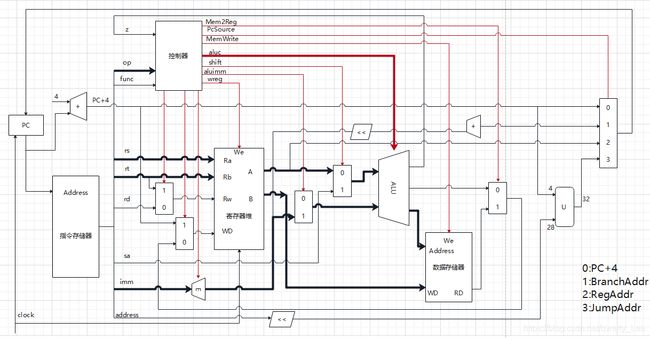

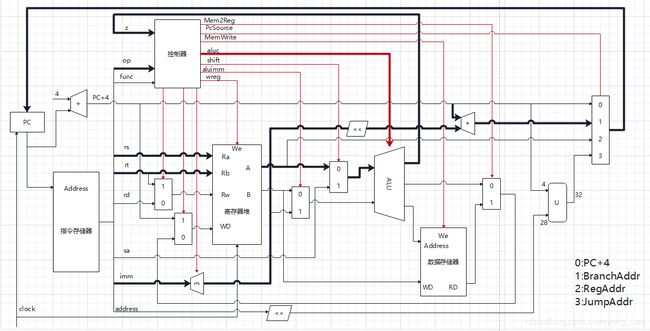

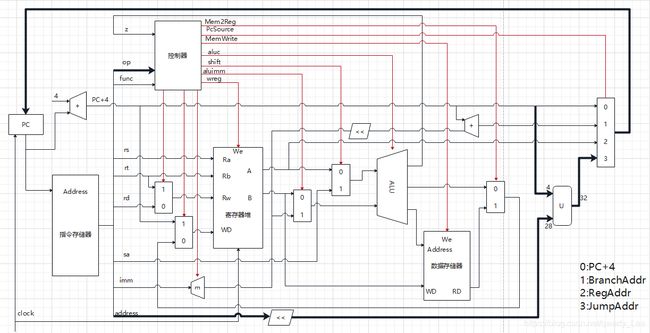

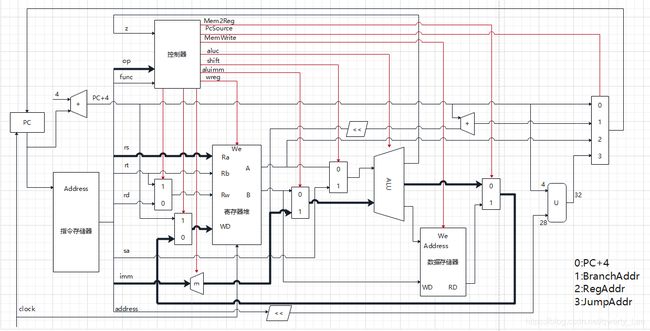

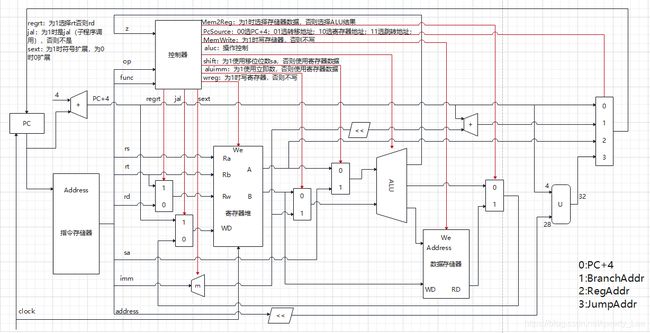

CPU数据通路图

这个数据通路图可能与上边的数据通路图有一些出入,以此为准,有错误欢迎指正。

寄存器堆:

Ra:地址输入端口

Rb:地址输入端口

Rd:地址写入端口

WD:数据输入端口,数据写入寄存器

数据存储器:

Address:地址输入端口

RD:数据输出端口

WD:数据输入端口,数据写入存储器

下一步设计ALU