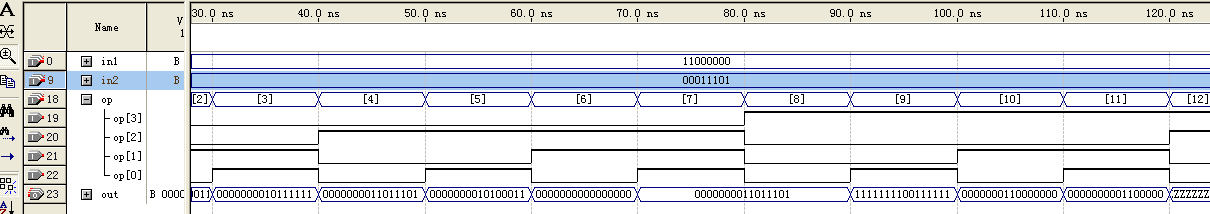

简单运算逻辑单元ALU,实现传递,自加1,自减1,相加,相减,与,或,异或,非,左移一位,右移一位.

Verilog代码:

module ALU(in1,in2,op,out);

input[7:0] in1,in2;

input[3:0] op;

output[15:0] out;

wire[7:0] in1,in2;

wire[3:0] op;

reg[15:0] out;

parameter transfer = 4'b0001,

increase = 4'b0010,

decrease = 4'b0011,

addtion = 4'b0100,

subtraction = 4'b0101,

AND = 4'b0110,

OR = 4'b0111,

XOR = 4'b1000,

NOT = 4'b1001,

shift_left = 4'b1010,

shift_right = 4'b1011;

always@(in1 or in2 or op)

begin

case(op)

transfer : out=in1;

increase : out=in1+1'b1;

decrease : out=in1-1'b1;

addtion : out=in1+in2;

subtraction : out=in1-in2;

AND : out=in1&in2;

OR : out=in1|in2;

XOR : out=in1^in2;

NOT : out=~in1;

shift_left : out=in1<<1;

shift_right : out=in1>>1;

default : out=16'bz;

endcase

end

endmodule

功能仿真结果: