McBsp接口使用和概念

McBsp很有用链接:http://wenku.baidu.com/link?url=aHBZP4Vy5rQPwYheFt-Zr3zXlX34HNn9zPwRElz-c55Nxj0-NhoOFbvu9IW8GK0XNaiVZAbEOXJ4VGhFc7pVtZwkzTVYlyHEkiLekGNGGHS

McBSP初始化以及和EDMA的结合使用(C64X DSP)

(1)时钟、帧以及相关寄存器设定

http://blog.csdn.net/aesthete/archive/2006/07/06/885425.aspx

2)McBSP初始化

McBSP可以通过两种方式进行数据传输:

EDMA方式:McBSP发送事件通知EDMA通道进行传输,有接收事件REVT和输出事件XEVT,它们都与固定EDMA通道进行了绑定;

CPU方式:McBSP通过中断方式通知CPU进行数据的传输,有接收中断RINT和输出中断XINT,中断的设定由SPCR.RINTM和SPCR.XINTM控制,如果要使用中断方式,应该设为00b;CPU也可以通过轮询方式(Polled)来控制数据的传输,主要是通过查询SPCR.RRDY和SPCR.XRDY来实现;

McBSP串口复位,两种方式:

①设备复位:REST引脚置为低电平,所有的串口部件都复位,相应的寄存器也处于复位状态;

②寄存器方式复位:跟设备复位不同,寄存器方式复位可以独立复位各部件,如单独对接收部件复位等;寄存器复位是通过设置SPCR.XRST...等完成的;

MsBSP的EDMA传输方式初始化步骤:

SPRC.GRST(XRST, RRST, FRST)设定为0,如果刚刚进行了设备复位,则无需再去设定;

设置SRGR、SPCR、PCR、RCR寄存器,注意不要设置上述的几个复位字段;

设置SPRC.GRST为1使GRS启动,此时GRS选定的时钟源就可以驱动CLKG开始工作;(如果接收部件和输出部件的帧同步和时钟都由外部源驱动的话,则这一步可以省略,因为无需Sampel Rate Generator支持工作);

等待两个位时钟(CLKR、CLKX):

N = ((1+CLKGDV) * 2 * CLKSM) + ((1+CLKGDV) * 2 * (Ps /P) * (!CLKSM));

启用中断

需要设定DSP的控制寄存器CSR.GIE位和IER.NMIE;

对于EDMA,启动CPU中断INT8,启用EDMA中断EDMA_INT,并且选定合适的EDMA通道(12~15通道,17和18通道);

EDMA初始化:

对EDMA通道进行编程设定,如:

设定源地址Source Address为DRR用于读,或者为内存位置用于写;

设定目的地址Destination Address为DXR用于写,或者为内存位置用于读;

CNT设置为要传输元素和帧个数;

接收同步事件R/WSYNC为McBSP的REVT用于读;

输出同步事件R/WSYNC为McBSP的XEVT用于写;

设置EDMA通道传输完成中断位TCINT为1,启用Transfer Complete中断;

PRI推荐为1;

准备EDMA的启动:设置EDMA事件启用寄存器EER的对应于某(些)通道的位,启用某(些)通道的事件触发;

如果McBSP接收部件以及输出部件在帧传输过程中是作为从设备(Slave,即帧同步信号是从外部获取的)的,则需要设置SPCR.XRST或SPCR.RRST为1,表示准备接收帧同步信号并且开始数据传输;还有一种进行同步的方法是使用帧同步中断来唤醒接收/输出部件,但是需要设定SPCR.(R/X)INTM为10b;

准备接收或者输出帧主设备(Master,即同步信号从内部获取)运行,需要设定SPCR.RRST或者SPCR.XRST为1;

如果FSGM=1,表示帧同步信号由SRG的FSG驱动,则需要设置FRST为1来启动FSG;如果FSGM=0,表示每次DXR复制到XSR都会产生一帧,因此FRST无意义;

MsBSP的CPU中断传输方式初始化步骤:

设置SPCR.XINTM或者SPCR.RINTM为00b,表示允许McBSP在DXR或者DRR中的数据准备好时给CPU发送中断;除了上述步骤的EDMA相关部分,其余都相同,EDMA部分替换为如下步骤:

①通过中断选择器MUXL/H把XINT(0/1/2)和/或者RINT(0/1/2)中断映射到CPU;

2. ②启用映射的中断。一旦McBSP初始化完成,传输每一个元素(写入DXR或者从DRR中读取)都会引起一次ISR的执行;

MsBSP的CPU轮询传输方式初始化步骤:

去除EDMA方式中的EDMA相关和中断相关,最后一步之后编写一个轮询循环检查SPCR.RRDY或者SPCR.XRDY以便确定McBSP是否准备好了接收或者输出。

(3)CSL在McBSP和EDMA中的应用

以DM642为例,要使用CSL API和C语言进行编程,需要在CCS集成开发环境的Project->Build Option中作一些设定,如link csldm642.lib以及link rts6400.lib,也需要预定义DSP芯片类型,如CHIP_DM642。当然,也可以在cmd文件中使用-l 选项加载csldm642.lib和rts6400.lib,在源文件或者头文件中#define CHIP_DM642。

在编程过程中,常用的CSL API如下:

声明CSL对象:

MCBSP_Handle hMcbsp

EMDA_Handle hEdma

EDMA_Handle hEdma_NULL

设置中断向量表:

IRQ_setVecs(vectors)

初始化CSL库:

CSL_init()

配置McBSP:

MCBSP_Config mcbspCfg

MCBSP_config(hMcbsp, &mcbspCfg)

打开McBSP通道:

hMcbsp = MCBSP_open(MCBSP_DEV0, MCBSP_OPEN_RESET);

启用sample rate generator:

MCBSP_enableSrgr(hMcbsp)

复位EDMA通道:

DMA_reset(INV)

EDMA_clearPram(0x00000000)

启用中断:

IRQ_nmiEnable()

IRQ_globalEnable()

IRQ_disable(IRQ_EVT_DMAINT0)

IRQ_clear(IRQ_EVT_DMAINT0)

IRQ_enable(IRQ_EVT_DMAINT0)

打开EDMA通道:

hEdma = EDMA_open(EDMA_CHA_REVT0, EDMA_OPEN_RESET);

配置EDMA通道:

EDMA_Config config;

EDMA_config(&config);

EDMA_configArgs()

配置空的EDMA参数集,需要结束时link到此参数集:

hEdma_NULL = EDMA_allocTable(−1);

EDMA_reset(hEdma_NULL);

EDMA_link(hEdma, hEdma_NULL); /* Link to terminating event */

启用EDMA:

EDMA_enableChannel(hEdma)

启用McBSP接收和传输部件

MCBSP_enableRcv(hMcbsp)

MCBSP_enableXmt(hMcbsp)

启用帧同步:

MCBSP_enableFsync(hMcbsp)

处理EDMA中断:

EDMA_intTest()

EDMA_intClear()

关闭McBSP 和 EDMA 通道:

MCBSP_close(hMcbsp)

DMA_close(hDma)

EDMA_close(hEdma)-----------------------------------------------------------------------------

本文大部分内容摘自

赵洪亮《TMS320C55X DSP应用系统设计(第2版)》

TI 《TMS320VC5501/5502/5509/5510 DSP Multichannel Buffered Serial Port (McBSP) Reference Guide》

------------------------------------------------------------------------------------------

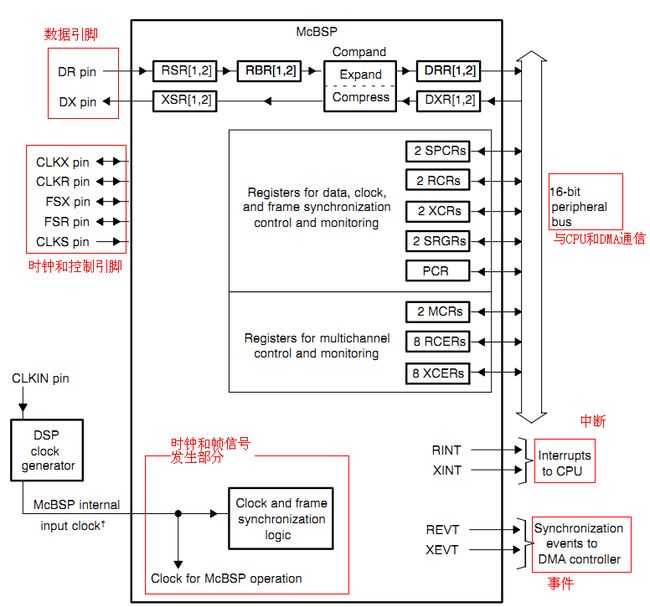

McBSP包括一个数据通道和一个控制通道,通过7个引脚与外部设备连接。

功能框图如下:

注意:

1、对于5502,MCBSP接收到的DSP的内部时钟是来自DSP的slow peripherals clock group,即是从divider2 (D2)分频器产生的时钟信号(SYSCLK2)。

2、在C55X系列中,不是每一款DSP都支持CLKS信号。对于不支持CLKS信号的芯片,是无法使用CLKS的相关功能的。

其中,7个引脚分别为

DX负责数据的发送;

DR负责数据的接收;

CLKX是发送时钟引脚;

CLKR是接收时钟引脚;

FSX是发送帧同步引脚;

FSR是接收帧同步引脚。

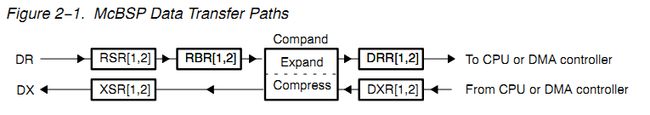

CPU和DMA控制器通过外设总线与MCBSP进行通信。当发送数据时,CPU和DMA将数据写入数据发送寄存器(DXR1,DXR2),接着复制到发送移位寄存器(XSR1,XSR2),通过发送移位寄存器输出至DX引脚。同样,当接收数据时,DR引脚上接收到的数据先移位到接收移位寄存器(RSR1,RSR2),接着复制到接收缓冲寄存器(RBR1,RBR2)中,RBR再将数据复制到数据接收寄存器(DRR1,DRR2)中,由CPU或DMA读取数据。这样就可以同时进行内部和外部的数据采集。

一、MCBSB的数据传输过程

MCBSP的接收操作是三缓冲(triple buffered)的,而发送操作是双缓冲(double buffered)的。寄存器值的使用取决于串行字长是否符合16bits。

如果字长为16bits或小于16bits(8bits、12bits),则只须使用一套寄存器(RSR1,RBR1,DRR1,DXR1,XSR1)。

如果字长大于16bits,则需要使用两套寄存器(RSR1/2,RBR1/2,DRR1/2,DXR1/2,XSR1/2)。

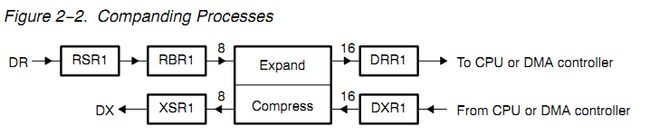

二、数据的压缩和扩展

1、MCBSP的压缩和扩展硬件可以将数据按照μ-律和A-律格式进行压缩和扩展。其示意图如下:

对于使用μ-律压缩和扩展的数据,要保证其在DXR1中进行14位左对齐,如下图:

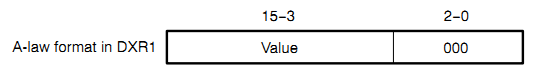

对于使用A-律压缩和扩展的数据,要保证其在DXR1中进行13位左对齐,如下图:

2、翻转数据位的顺序

MCBSP默认为最高位先发送,但是对于一些固定的8bits传输协议,需要先进发送最低位的数据。MCBSP可以通过设置XCR2的XCOMPAND 为01,则8bits的数据在通过串行口发送前将会被翻转,这样发送数据时就变成低位优先发送。

三、时钟和帧信号

1、时钟

数据从DR管脚到RSR寄存器及从XSR寄存器到DX管脚是一位一位传送的。每传输一位的时间是由时钟信号的上升沿或下降沿来决定的。

接收时钟信号(CLKR)控制着DR管脚到RSR寄存器的每一个bit的传输;发送时钟信号(CLKX)控制着XSR寄存器到DX管脚的每一个bit的传输。CLKR和CLKX信号可以来自MCBSP的外部时钟引脚,也可以来自MCBSP内部。另外,CLKR和CLKX信号的极性(正或负?)是可编程控制的。

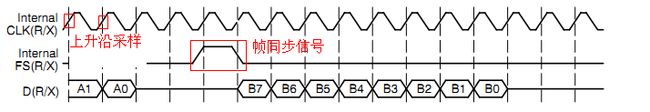

下如示意了时钟信号如何控制每一bit传输的时间:

注:5502的MCBSP的最高频率是DSP的slow peripherals clock的1/2。如果使用DSP的管脚来输入CLKX和CLKR信号,则注意选择合适的输入时钟频率。如果使用内部生成的采样频率,则注意选择适合的输入时钟频率和设置相应的分频数(CLKGDV)。

2、串行字

bits在移位寄存器(RSR或XSR)和数据管脚间传输时,是按组转移的,一组称为一个串行字(serial word)。一个串行字的bit数是可以由用户来定义的。

从DR管脚进来的数据会先存放在RSR寄存器,直到RSR寄存器存满了一个串行字,然后,这个串行字才会被发往RBR(最后道达DRR)。DX管脚同理。

3、帧和帧同步

把一个或多个串行字当成一个组来进行传输,称为帧。你可以定义一个帧里包含多少个串行字。

一个帧里的字会被连续传输,帧与帧之间则会有停顿。MCBSP使用帧同步信号来确定每一个帧的发送/接收。当帧同步信号产生一个脉冲,则MCBSP开始接收/发送一个帧数据,当下一个帧同步脉冲产生时,就发送下一帧,依此类推。

FSR信号用了开始DR管脚的数据传输,FSX用来开始DX管脚的数据传输。FSR和FSX信号可以来自MCBSP的边界管脚或来自MCBSP内部。

4、检测帧同步信号,即使在reset状态中

MCBSP可以发送传输/接收中断至CPU,用了通知CPU 自己发生了某些特定事件。为了帮助甄别帧同步信号,一些中断可以被发送用来作为帧同步脉冲的响应。将相应的中断模式位设置为10(对于接收,RINTM=10;对于发送,XINTM=10)。

不同于其他的串口中断模式,MCBSP的中断模式在串口的相关部分处于reset状态时仍然在运行。

5、忽略不希望遇到的帧同步脉冲

MCBSP可以配置,用以忽略发送或接收帧同步脉冲。

如果想识别帧同步信号,则对于接收端,设置RFIG=0;对于接收端XFIG=0。

如果想忽略帧同步信号,则对于接收端,设置RFIG=1;对于接收端XFIG=1。

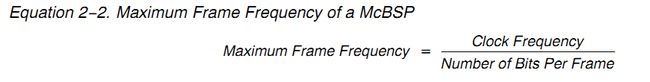

6、帧频率

振频率等于时钟频率除以一个帧持续的时钟周期数,如下图所示:

最大振频率为时钟频率除以一个帧所包含的bit数,如下图:

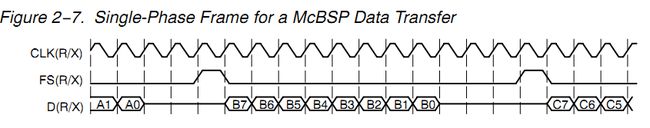

当帧频率为最大值时,其脉冲与数据波形的关系如下:

示意图中使用的是1-bit的数据延时(1-bit data delay)。

注:对于5502芯片,如果使用0bit延时的帧同步并且使用的是外部时钟,则需要一个多余的帧周期,因而最高帧频率将达不到上述的速度;如果是1-bit或2-bits延时或使用内部时钟,则不需要多余的帧周期,因而可以达到上述的帧频率。

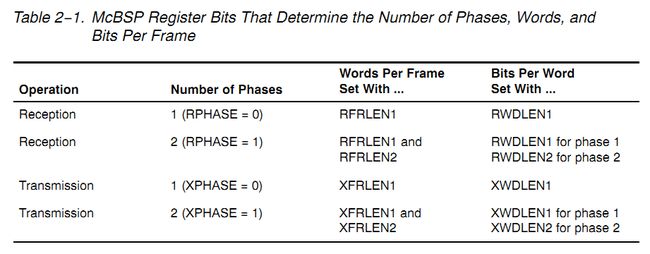

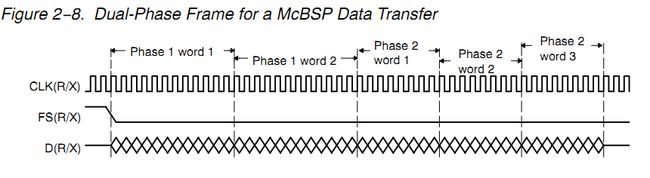

四、帧阶段(Frame Phases)

MCBSP可以通过配置,让一个帧拥有不同的阶段。

一个帧的不同阶段可以拥有不同的字的数量,每个字的bits个数也可以不同。得益于这样的时间,MCBSP的帧可以灵活的传输各种结构的数据。

1、一帧中的阶段数、字数和bits数

一帧中的阶段数、字数和bits数的如何有寄存器决定:

只有一个phase的帧的传输:

有两个phases的帧的传输

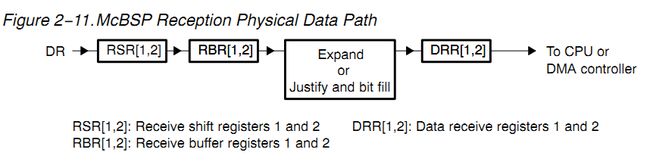

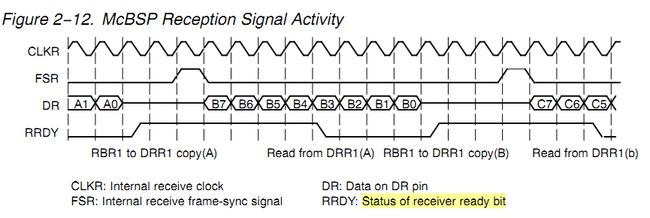

五、MCBSP接收

物理数据通路:

接收数据时序图:

下面将描述数据由DR管脚到CPU或DMA的过程:

(1)MCBSP用FSR管脚等待帧同步信号的到来

(2)当帧同步脉冲到来后,MCBSP插入相应的数据延迟。数据延迟的数量在RCR2寄存器的RDATDLY位中设定。

(3)MCBSP从DR管脚接收数据,并移位至接收移位寄存器(RSR1/21)中。(如果字长小于或等于16bit,则只使用RSR1寄存器,如果大于16bits则除了RSR1外还要使用RSR2寄存器,数据的高位存在RSR2寄存器中)

(4)当一个完整的字被完全送达后,MCBSP将RSR寄存器中的值拷贝到接收缓冲寄存器(RBR),规定RBR1不被之前的数据占满。(如果字长小于或等于16bit,则只使用RBR1寄存器,如果大于16bits则除了RBR1外还要使用RSR2寄存器,数据的高位存在RBR2寄存器中)

(5)MCBSP将RBR中的数据拷贝到数据接收寄存器(DRR)中,规定DRR1不被之前的数据占满。当DRR1接收到新数据时,SPCR1寄存器的receiver ready bit(RRDY)将置1。这暗示着接收的数据已经准备妥当,可以被CPU或DMA控制器读取。(如果字长小于或等于16bit,则只使用DRR1寄存器,如果大于16bits则除了DRR1外还要使用DRR2寄存器,数据的高位存在DRR2寄存器中)。如果在由RBR拷贝到DRR的过程中使用了数据扩展或压缩(companding),则RBR1中的8-bit数据将扩展为DRR中左对齐的16-bit数据。如果在拷贝过程中没有使用数据扩展或压缩,则从RBR[1,2]拷贝到DRR[1,2]的数据将进行调整并按照RJUST位进行bit填充。

(6)CPU或DMA控制器从数据接收寄存器中读取数据。当DRR1的内容被读取后,RRDY将被置0,然后下一个RBR至DRR的拷贝将开始。

注:如果DRR1和DRR2都被使用了(即字长大于16-bit),那么CPU或DMA控制器必须先读DRR2的数据然后再读DRR1的数据。当DRR1的数据被读取后,下一个RBR至DRR的拷贝周期马上开始。如果先读DRR1的话,则DRR2中的数据将丢失。

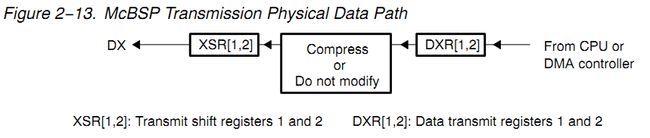

六、MCBSP发送

MCBSP发送物理通路示意图:

MCBSP发送时序图:

MCBSP发送数据的过程如下:

(1)CPU或DMA控制器将数据写入数据发送寄存器(DXR)中。当DXR1中载入数据时,SPCR2寄存器中的transmitter ready bit(XRDY)位被清零,用以表示发送器还未准备好新数据。如果字长超过16-bit,则除了DXR1寄存器外,还需要使用DXR2寄存器;否则,只要使用DXR1寄存器即可。

注:如果DXR1和DXR2寄存器都被使用了,则CPU或DMA控制器在向DXR寄存器中载入数据时,需要先载入DXR2的数据,然后载入DXR1的数据。当DXR1中被载入数据时,DXR寄存器中的数据会立刻被拷贝入发送移位寄存器(XSR)中。如果DXR2没有被先载入,则先前的DXR2中的数据将被移位至XSR2中,而导致数据错误。

(2)当新数据到达DXR1后,MCBSP将会将数据发送寄存器(DXR)中的内容拷贝入发送移位寄存器(XSR)中。另外,transmit ready bit将会被置1。由此表示接收器已经准备好从CPU和DMA控制器中接收数据。如果字长超过16-bit,则除了XSR1寄存器外,还需要使用XSR2寄存器;否则,只要使用XSR1寄存器即可。

如果数据压缩和扩展(companding)被启用,则MCBSP将DXR1中的16-bit数据压缩为XSR1中的8位数据;如果没有被启用,则MCBSP直接将DXR中的数据传输到XSR而不做任何调整和改动。

(3)MCBSP在FSX管脚上等待传输帧同步信号。

(4)当帧同步脉冲到达时,MCBSP按照XCR2寄存器中的XDATDLY位所设定的数据延迟来插入数据延迟。

(5)MCBSP将发送移位寄存器(TXR)中的数据位移位至DX管脚。

八、MCBSP产生的中断和DMA事件

MCBSP通过下述内部信号来通知CPU和DMA控制器: