谈及此部分,多多少少有一定的难度,笔者写下这篇文章,差不多是在学习FPGA一年之后的成果,尽管当时也是看过类似的文章,但是都没有引起笔者注意,笔者现在再对此知识进行梳理,也发现了有很多不少的收获。笔者根据网上现有的资源,作进一步的总结,希望能够有所帮助。

一个不错的网站,类似于一个手册,随时可以去查询如何去定义各个时序约束指令怎么用。http://quartushelp.altera.com/current/mergedProjects/tafs/tafs/tcl_pkg_sdc_ver_1.5.htm

静态时序分析(STA,static timing analysis),对于STA的理解,可以想象在FPGA的内部好比一块PCB,FPGA的逻辑阵列好比PCB板上的一些分立元器件,PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通,PCB上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过内部逻辑门传输也有一定的延时,PCB信号走线也有延时,FPGA信号走线也有延时,这就带来了一系列的问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理之后从FPGA的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输延时的不一致,不仅会影响FPGA本身会给FPGA之外的电路或者系统带来诸多的问题。

所以针对上面的一系列问题,设计者需要提出一些特定的时序要求,针对现有的电路给出时序约束,

分析时序,本质上是节点对节点之间的时序分析,如果没有节点,时序也就无从谈起。在FPGA中,我们可以把节点当作是寄存器与寄存器之间的时序分析,寄存器与寄存器之间可能还有一些组合逻辑充斥着。所以时序路径通常有四大类:

(1)寄存器到寄存器类型,即reg2reg;

(2)输入引脚到寄存器类型,即pin2reg;

(3)寄存器到输出引脚类型,即reg2pin;

(4)输入引脚到输出引脚类型,即pin2pin;

针对上述四种基本时序路径,最关心的就是数据信号和时钟锁存沿之间的建立时间和保持时间的关系。

对于四种延时路径可以用图1所示,对于signal in,是外部IC到FPGA的输入信号引脚,一般情况下芯片手册都会给出各引脚关于时序方面的说明,如Tco、TSU、Th、等信息,这个是在分析时序时会用到。Reg1到reg2之间的时序路径是相当于在FPGA内部的寄存器到寄存器之间的延时路径,signal out是相当于FPGA的输出信号到外部IC之间的引脚信息。

图1 时序路径分析

这里只分析FPGA内部的时序路径,外部IC的时序路径需要结合具体的IC数据手册,然后结合FPGA输入引脚部分的大概延时进行推测一个值,之后具体再分析。

所以从寄存器1到寄存器2之间的延迟时间的分析。

图16.2 寄存器到寄存器延时

上图是考虑各种延迟之后的从输入数据到输出数据的时间延迟。

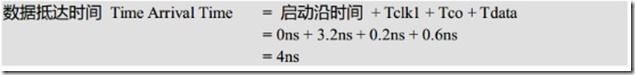

所以我们引入第一个概念:数据抵达时间(官方视频上面的概念),也就是实际到达时间,

引入第二个概念:数据要求时间

图16.3 数据要求时间分析

由于有寄存器建立时间的参与,所以会使得数据锁存时间由下面的公式决定,但是在应用时Tsu按照负值代入公式,这样计算的才正确,可能是官方的bug,所以按照负值计算即可。

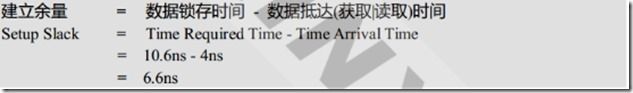

建立余量

为了说明怎么计算得到建立余量,特举例如下所示。

对于公式上面的锁存沿时间,其实就是启动沿和锁存沿之间的差值,也就是建立时间关系,建立时间关系是理想状态下,启动沿与锁存沿之间的距离,如下图2所示,这个建立时间关系 = 时钟周期,所以在计算的时候,可以先计算出建立时间关系值,然后也就确定了锁存沿时间。

图2 建立时间和时钟周期的关系

保持余量

还是用我们的经典的图来说明保持余量,那么数据从寄存器1到寄存器2要经过的时间为

![]()

![]()

其中数据周期时间,是以时钟周期为计算值。

根据上图,用一些数字来计算,如下图

由此得到了保持余量值。

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================