时序收敛-基本方法论

本部分内容参考ug612 《Timing Closure User Guide 》,主要是对第二章内容的整理和翻译。

在一个有效的设计中,生成工具必须要了解每一条路径上的时序约束。时序需求可以被分为几个大类,最通用的类型包括:

•Input paths

• Register-to-register paths

• Output paths

• Path specific exceptions

指定约束应该从全局约束开始,然后添加局部路径的例外。也就是说,全局的约束优先级是最低的。

1.输入时序约束

The input timing constraints cover the data path from the external pin or pad of the package of the FPGA device to the internal synchronous element or register that captures that data.

输入时序约束控制外部引脚到内部模块的路径。采用OFFSET IN来指出input timing constraints。(The OFFSET IN constraint defines the relationship between the data and the clock edge used to capture that data at the pin or pads of the FPGA device.)也就是说OFFSET IN定义了时钟沿河被采集数据的关系(相位)。输入模式分为两类,分别如下。

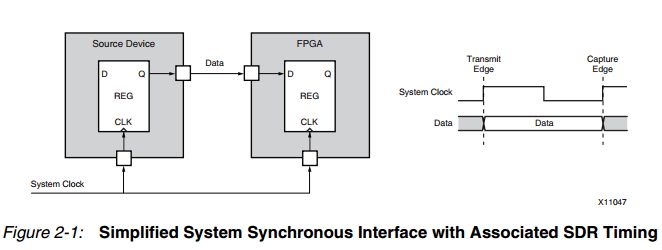

System Synchronous inputs

系统同步输入,指由同一时钟传输和捕获数据,如下图所示

1.时钟上升沿传输

2.下一个上升沿捕获

那么global constraint 是OFFSET = IN value VALID value BEFORE clock;

例子:(理想情况)

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk";

Source synchronous inputs

In a source synchronous input interface, a clock is regenerated and transmitted along with the data from the source device along similar board traces. This clock captures the data in the FPGA device.

The board trace delays and board skew no longer limit the operating frequency of the interface. The higher frequency also results in the source synchronous input interface typically being a dual data rate (DDR) application.

即一个时钟周期传两组数据,上升沿和下降沿均采集数据,在传输数据的同时传输时钟,利用重新生成的时钟捕获数据(DDR取代SDR)

在这种情况下约束如下

OFFSET = IN valueVALID valueBEFORE clockRISING;

OFFSET = IN valueVALID valueBEFORE clockFALLING;

例子: (理想情况)

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" RISING;

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" FALLING;

在实际情况下,不可能像上面的例子那样理想,IN后面跟的是INPUT的开始时间(相对clock的提前量),VALID是数据的有效时间。

2.寄存器-寄存器的时序约束

寄存器-寄存器的约束,在同步时序电路中,就是周期的约束,具体分为以下几类

自动相关同步时钟域

手动相关同步时钟域

异步时钟域

自动相关同步时钟域(DLL,DCM,PLL,MMCM)

因为它是自动的,所以基本不用管,当时我们要写输入到DCM的信号的时序约束。例如

NET “ClkIn” TNM_NET = “ClkIn”;

TIMESPEC “TS_ClkIn” = PERIOD “ClkIn” 5 ns HIGH 50%;

手动相关同步时钟域

如果说,输入的同步时钟是从不同的引脚引入的,那么DCM就用不了了,我们需要手动的定义一个主时钟,并以之为参考,定义相对的约束。语法如下:

NET “PrimaryClock” TNM_NET = “TNM_Primary”;

NET “RelatedClock” TNM_NET = “TNM_Related”;

TIMESPEC “TS_primary” = PERIOD “TNM_Primary” PeriodValue HIGH

HighValue%;

TIMESPEC TS_related” = PERIOD “TNM_Related” TS_Primary_relation PHASE

value;

异步时钟域

xilinx无法分析,也可以用,具体参考ug612。

3.输出时序约束

输出就是输入的逆

SDR

例子:NET "ClkIn" TNM_NET = "ClkIn";

OFFSET = OUT 5 ns AFTER "ClkIn";

DDR(一般来说不给约束就可以)

例子:NET “ClkIn” TNM_NET = “ClkIn”;

OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” RISING;

OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” FALLING;

以下两个部分没有看明白为何放在output timing constraints中

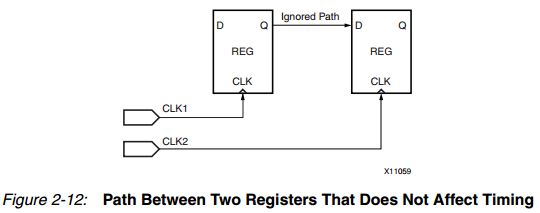

False Paths 移除不需要(不对)的约束

采用FROM TO约束可以移除(忽略)指定路径上的约束,即如下图所示情况

To specify the Timing Ignore constraint for this method, define:

• A set of registers for the source time group.

• A set of registers for the destination time group.

• A From-To constraint with a Timing Ignore keyword to remove the paths between the groups.

在指定FROM—TO约束路径之前,我们需要指定源寄存器和目标寄存器,语法如下

NET "CLK1" TNM_NET = FFS "GRP_1";

NET "CLK2" TNM_NET = FFS "GRP_2";

TIMESPEC TS_Example = FROM "GRP_1" TO "GRP_2" TIG;

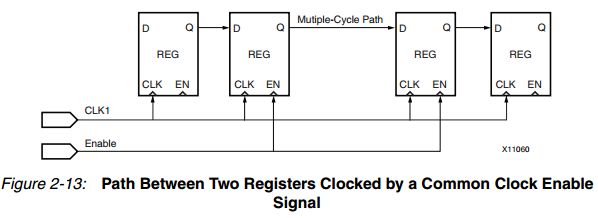

Multi-cycle Paths (多周期路径)

这个和前面的实际上是一样的,不够这两个寄存器是一个时钟信号和使能信号驱动的。

Syntax Example

NET "CLK1" TNM_NET = "CLK1";

TIMESPEC "TS_CLK1" = PERIOD "CLK1" 5 ns HIGH 50%;

NET "Enable" TNM_NET = FFS "MC_GRP";

TIMESPEC TS_Example = FROM "MC_GRP" TO "MC_GRP" TS_CLK1*2;

关于这两部分,可以参考博客特定约束From to。

![clipboard[1] clipboard[1]](http://img.e-com-net.com/image/product/1136a5d9d05c4e4bbc9fd7685f3b62dd.jpg)

![clipboard[6] clipboard[6]](http://img.e-com-net.com/image/product/656c01295802421a8475104e99785f3a.jpg)

![clipboard[7] clipboard[7]](http://img.e-com-net.com/image/product/58df766041844deb9e4424619a1ec0fa.jpg)