信号完整性与电源完整性分析_信号完整性与电源完整性分析(下)

在信号完整性中,重点是确保传输的1在接收器中看起来就像 1(对0同样如此)。

在电源完整性中,重点是确保为驱动器和接收器提供足够的电流以发送和接收1和0。

电容退耦的两种解释

采用电容退耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。

储能的角度

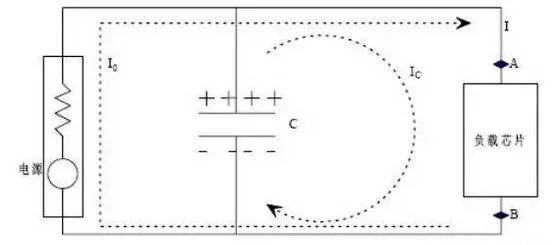

在制作电路板时, 通常会在负载芯片周围放置很多电容, 这些电容就起到电源退耦作用。其原理如下图:

图1当负载电流不变时,其电流由稳压电源部分提供,即图中的Io,方向如图所示。此时电容两端电压与负载两端电压一致,电流Ic为0,电容两端存储相当数量的电荷,其电荷数量和电容量有关。

当负载瞬态电流发生变化时,由于负载芯片内部晶体管电平转换速度极快,必须在极短的时间内为负载芯片提供足够的电流。但是稳压电源无法很快响应负载电流的变化,因此,电流Io不会马上满足负载瞬态电流要求,从而负载芯片电压降低。

但是由于电容电压与负载电压相同,所以电容两端存在电压变化。对于电容来说电压变化必然产生电流,此时电容对负载放电,电流Ic不再为0,为负载芯片提供电流。

只要电容量C足够大,只需很小的电压变化,电容就可以提供足够大的电流,满足负载态电流的要求。相当于电容预先存储了一部分电能,在负载需要的时候释放出来,即电容是储能元件。

储能电容的存在使负载消耗的能量得到快速补充,因此保证了负载两端电压不至于有太大变化,此时电容担负的是局部电源的角色。

从储能的角度来理解电源退耦,非常直观易懂,但是对电路设计帮助不大。

从阻抗的角度理解电容退耦,能让我们设计电路时有章可循。事实上,在决定电源分配系统的去耦电容的时候,用的就是阻抗的概念。

阻抗的角度

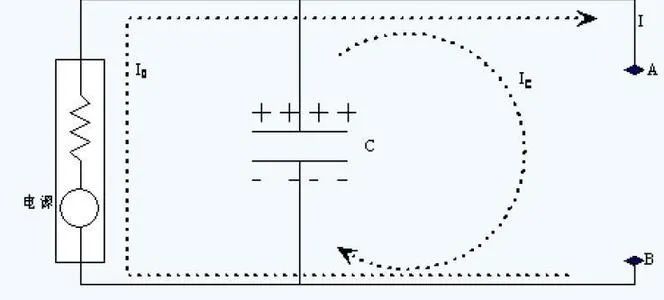

将图 1 中的负载芯片拿掉,如图 2 所示。从 AB 两点向左看过去,稳压电源以及电容退耦系统一起,可以看成一个复合的电源系统。

这个电源系统的特点是:不论 AB 两点间 负载瞬态电流如何变化,都能保证 AB 两点间的电压保持基本稳定,即 AB 两点间电压变化很小。

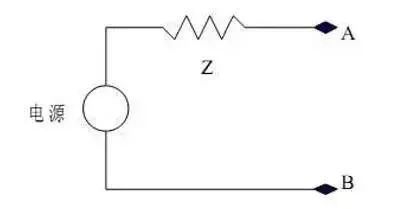

我们可以用一个等效电源模型表示上面这个复合的电源系统,如图3.

图3

对于这个电路可写出如下等式:

最终设计目标是,不论 AB 两点间负载瞬态电流如何变化,都要保持 AB 两点间电压变化范围很小。

根据上面公式,这个要求等效于电源系统的阻抗Z要足够低。在图2中,我们是通过去耦电容来达到这一要求的。从等效的角度出发,去耦电容降低了电源系统的阻抗。

另一方面,从电路原理的角度来说,可得到同样结论。电容对于交流信号呈现低阻抗特性。加入电容,实际上也降低了电源系统的交流阻抗(1/jwc)。

从阻抗的角度理解电容退耦,会给我们设计电源分配系统带来极大的方便。

电源分配系统设计的最根本的原则就是使阻抗最小。最有效的设计方法就是在这个原则指导下产生的。

实际电容的特性

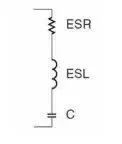

正确使用电容进行电源退耦,必须了解实际电容的频率特性。理想电容器在实际中是不存在的,这就是为什么常听到“电容不仅仅是电容”的原因。

实际的电容器总会存在一些寄生参数,这些寄生参数在低频时表现不明显,但是高频情况下,其重要性可能会超过容值本身。

图4是实际电容器的SPICE模型,图中,ESR代表等效串联电阻,ESL代表等效串联电感或寄生电感,C为理想电容。

图4

等效串联电感(寄生电感)无法消除,只要存在引线,就会有寄生电感。

这从磁场能量变化的角度可以很容易理解,电流发生变化时,磁场能量发生变化,但是不可能发生能量跃变,表现出电感特性。

寄生电感会延缓电容电流的变化,电感越大,电容充放电阻抗就越大,反应时间就越长。

自谐振频率点是区分电容是容性还是感性的分界点,高于谐振频率时,“电容不再是电容”,因此退耦作用将下降。

电容的等效串联电感和生产工艺和封装尺寸有关,通常小封装的电容等效串联电感更低,宽体封装的电容比窄体封装的电容有更低的等效串联电感。

在电路板上会放置一些大的电容,通常是坦电容或电解电容。这类电容有很低的ESL,但是ESR很高,因此Q值很低,具有很宽的有效频率范围,非常适合板级电源滤波。

电路的品质因数越高,电感或电容上的电压比外加电压越高。Q值越高在一定的频偏下电流下降得越快,其谐振曲线越尖锐。也就是说电路的选择性是由电路的品质因素Q所决定的,Q值越高选择性越好。

局部去耦设计方法

为保证逻辑电路能正常工作,表征电路逻辑状态的电平值必须落在一定范围内。比如对于3.3V逻辑,高电平大于2V为逻辑1,低电平小于0.8V为逻辑0。

把电容紧邻器件放置,跨接在电源引脚和地引脚之间。正常时,电容充电,存储一部分电荷。这样电路转换所需的瞬态电流不必再由VCC提供,电容相当于局部小电源。

因此电源端和地端的寄生电感被旁路掉了,寄生电感在这一瞬间没有电流流过,因而也不存在感应电压。通常是两个或多个电容并联放置,减小电容本身的串联电感,进而减小电容充放电回路的阻抗。