STM32MP157系列教程连载-硬件设计篇2:STM32MP1微处理器之电源篇

STM32MP157系列教程连载-硬件设计篇2:STM32MP1微处理器之电源篇

一、官网资料下载

官网是获取设计资料与技术支持的最好途径。ST官网为用户提供了STM32MP1系列处理器的详细设计资料(数据手册、参考手册、设计参考文档)与参考电路板(DK板与EV板),用于产品设计参考:

官网首页

进入官方后,选择产品->微控制器->STM32 Arm Cortex MPUs(点击) 进入STM32MP1系列处理器界面,并点击产品选择器一栏。

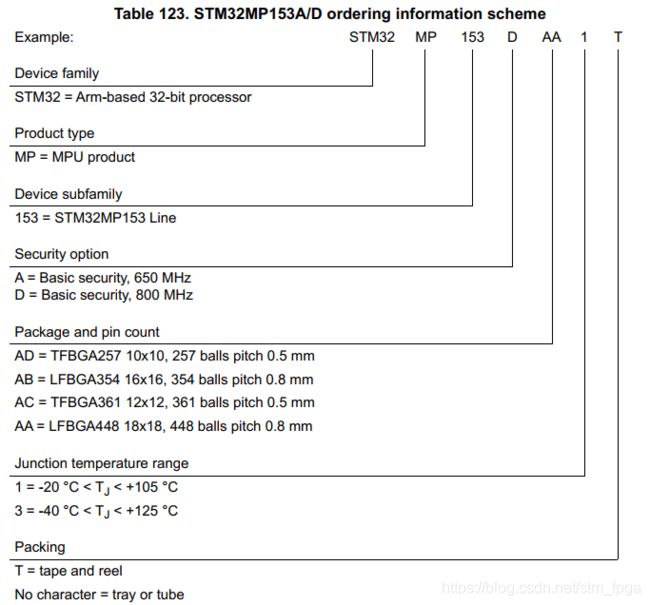

在筛选器的封装一栏选择LFBGA448。大约做一下说明,STM32MP1现在包含3条产品线,4种不同封装,并支持可选的安全性能(安全启动与硬件加密)。总结下来STM32MP157系列的资源最多,支持4种不同封装,双核Cortex-A7+单核Cortex-M4架构,支持3D GPU、MIPI-DSI与升级版的CAN总线,同时也意味着芯片成本更高(有失有得)。STM32MP153系列支持4种不同封装,双核Cortex-A7+单核Cortex-M4架构,不支持3D GPU与MIPI-DSI,支持升级版的CAN总线。STM32MP151系列支持4种不同封装,单核Cortex-A7+单核Cortex-M4架构,成本最低。在其它方面,均支持SDRAM、Timers、SPI、I2C、USART/UART、SAI、USB、SDMMC、FMC、HDMI-CEC、QuadSPI、Gigabit Ethernet、 10/100M Ethernet、24bit Parallel interface、14 bit Camera interface、DFSDM、16 bit synchronized ADC、12 bit DAC外设资源。3条产品线,4种不同封装以及丰富的外设,使用户能够在性能与成本之间找到平衡点,以应对当前复杂的需求以面向不同应用场景。

下拉产品条目,选择STM32MP157A(FS-MP1A开发板搭载的型号),点击左侧箭头展开,点击打开产品页面按钮。

在跳转后的页面点击资源一栏,用户可以根据实际需求下载STM32MP157A/D的资料,资料如下所示:

以上文件根据实际设计需求进行下载,需要注意的是设计人员需要不定时更新一下勘误手册或其它重要设计文档,作为一款新推出的处理器,随着使用者的增多,官方会逐渐的更新一些芯片BUG,并给出了应对方式,需要我们在设计、调试与使用中避开BUG。

之后进行DK与EV参考板相关设计资料下载,回到当前页面的顶部,点击工具与软件栏,下拉页面找到评估工具。

官方给出的评估板主要分为DK板与EV板,DK板采用的处理为STM32MP157A/C系列,封装TFBGA361,配备1颗512MB(25616)的DDR3L,无eMMC存储,采用集成电源管理芯片(STPMIC1),板载WiFi/BLE模块,接口包含HDMI、千兆以太网、音频、USB、MIPI-DSI、SD存储卡等;EV板采用的处理器为STM32MP157A/C系列,封装LFBGA448,配备2颗512MB(25616)的DDR3L,拓扑结构采用fly-by,配备eMMC以及NAND存储,采用集成电源管理芯片(STPMIC1),包含SD存储卡、USB、串口、音频、千兆以太网、摄像头、MIPI-DSI、RGB LCD等接口。

点击相应的产品型号后,页面跳转后,进入资源下载栏即可下载相应板子资料,建议用户下载STM32MP157C-DK2/ STM32MP157C-EV1以及STM32MP157F-EV1三个评估板的资料即可,STM32MP157A-DK1/ STM32MP157A-EV1跟其它3个评估板,相同产品仅处理器差异(Basic security,without Secure boot and cryptography hardware)。

二、处理器电源设计

本章主要讲解分立元件电源设计方案,采用FS-MP1A开发板作为设计讲解平台,用到的文档资源主要有3个(可在上文ST官网或意法半导体stm32中国官网下载,此部分讲解以官方文档翻译与参考设计为主,如翻译或理解有误,请以官方文档为主):

-

AN5031(Application note)-Getting started with STM32MP151, STM32MP153

and STM32MP157 line hardware development -

AN5256(Application note)- STM32MP151, STM32MP153 and STM32MP157

discrete power supply hardware integration -

FS-MP1A开发板原理图(意法半导体stm32中国官网)

1.端口(IOport)电压(VDD)范围为1.71 V~3.6 V。

2.内核(VDDCORE)电压范围为1.18 V~1.25 V。

3.USB(VDD3V3_USBHS/VDD3V3_USBFS)电压范围为3.07 ~3.6 V。

4.内部调整器被用于内部模块(注意:内部调整器不能用于外部组件)

- DSI regulator产生1.2V电源, 通过VDD1V2_DSI_REG引脚输出,用于内部DSI

PLL和VDD1V2_DSI_PHY引脚,范围为1.15 V~1.26 V。 - 1V8 regulator产生1.8V电源,通过VDDA1V8_REG引脚输出,可用于内部USB HS

PHY和供给VDDA1V8_DSI引脚。 - 1V1regulator产生1.1V电源,用于内部USB HS PHY,外部VDD1V1_REG引脚需要增加去耦电容。

- 当BYPASS_REG1V8 = VDD时,必须由外部提供VDDA1V8_REG。在这种情况下,工作电压范围是1.65 V~1.95 V。

5.实时时钟(RTC)和备份寄存器可以从VBAT电压供电,当主VDD电源关闭。内部电源会在VBAT和VDD之间自动切换(VSW域),也用于供应PI8,PC13, PC14, PC15管脚。

- VBAT电压范围为1.20 V~3.6 V。

- 当VDD电压大于VBAT电压时,通过VBAT引脚将为外部备份电压器件(超级电容器)提供一个小的充电电流。

2.2 ADC和DAC转换器独立电源和参考电压

在电路板上给ADC、DAC与参考电压提供一个经过过滤与噪声屏蔽的独立电源,可以提高转换精度与动态范围。

模拟工作电压(VDDA)的范围为1.71 V~3.6 V (当VDDA大于或等于1.8 V时,DAC转换器才能够被使用)。

- 通过VDDA引脚为ADC/DAC/VREFBUF电压提供输入。

- 通过VSSA引脚提供一个隔离的电源接地连接。

- 通常情况下,VSSA引脚应该外部连接到相同的供应地VSS。

外部VREF:通过VREF+引脚可以提供给ADC/DAC转换器一个单独的外部参考电源,要求参考电源范围为1.62 V~VDDA,DAC正常工作需要VREF+的电压高于1.8V。

内部VREF:通过VREFBUF(Reference manual中的Voltage reference buffer (VREFBUF)一章)可以使能内部参考电压。

- VREF+引脚电压可设置为1.5 V、1.8 V、2.048 V和2.5 V。

- VREF+上的参考电压也可用于外部使用(例如模拟比较器的参考电压)。

注意:VREFBUF要求VDDA等于或高于VREF+ + 0.3V。

警告:当可用时(取决于封装),VREF -引脚必须从外部连接到VSSA。

ADC模拟输入开关的升压:ADC输入通过模拟开关复用,当VDDA电源低于2.7 V时,模拟开关的性能降低。为了获得最大的ADC模拟性能,可以为模拟开关提供VDD(如果高于2.7 V)或来自于VDDA的嵌入式3.3 V升压器,通过SYSCFG_PMCR寄存器完成相关设置。

2.3 电池备份

为了保留备份寄存器、BKPSRAM和RETRAM的内容,当VDD关闭时,VBAT引脚可以连接到由电池或其他电源提供的备用电源。

VBAT引脚也为RTC单元供电,允许RTC即使在主数字电源(VDD)关闭时也能工作。VBAT电源的开关由复位块内嵌的电源关闭复位(PDR)电路控制。

如果在应用程序中没有使用外部电池,则需要从外部连接VBAT到VDD。

2.4 电压调整器

如果BYPASS_REG1V8引脚连接VSS, 1.8V的LDO(用于USB和DSI)在上电复位后被使能。它不受LP-Stop/LPLV-Stop模式的影响,但在进入待机模式后被禁用。

1.1V的LDO(用于USB)在上电复位后被使能。它不受LP-Stop/LPLV-Stop止模式的影响,但在进入待机模式后被禁用。

1.2V的LDO(用于DSI)在系统复位后被禁用,在使用DSI之前必须通过软件使能。它不受LP-Stop/LPLV-Stop模式的影响,但在进入待机模式后被禁用。

注:除非特别说明,内部电压调整器不能用于外部组件供电。

2.5 电源供应方案

电路需要多种电源供应:

1.在待机模式下,IOs和内部设备的电源由VDD提供。有用的电压范围为1.71 V~3.6 V(例如:1.8 V, 2.5 V, 3.0 V或3.3 V)。

- 这些电源在外部必须连接去耦电容(详见表4)。

- VDD_DSI, VDD_PLL和VDD_ANA必须连接到VDD。

2.VDDCORE是主要的数字电压,在待机模式下可以关断。运行模式下的电压范围为1.18V至1.25/1.38V(典型值1.2/1.34V)。

- 该电源在外部必须连接去耦电容(详见表4)。

- 通过PWR_ON信号(例如STPMIC1、外部电源管理IC)或PWR_LP信号(分立电源设计组件),在特定的停止模式(LPLV_Stop)下可以进一步降低VDDCORE。

3.VBAT引脚可连接外部电池(1.2V 4.VDDA引脚是模拟(ADC/DAC/VREFBUF)电源,外部必须连接去耦电容(见表4)。 5.VREF+引脚可以连接到VDDA并由外部电源供电。如果在VREF+采用个独立的内部或外部参考电压,则必须在该引脚和VREF-之间连接一个去耦电容(见表4)。请参阅第2.2节。可以采取其它预防措施来过滤模拟噪声。 6.VDDQ_DDR是DDR的IO电源,外部必须连接去耦电容(见表4)。 7.VDDA1V2_DSI_REG引脚是内部稳压器输出,外部必须连接去耦电容(见表4)。 8.VDDA1V2_DSI_PHY是模拟DSI PHY电源。电压范围为1.15V~1.26V(典型值1.2V)。 9.VDD3V3_USBHS和VDD3V3_USBFS分别是USB高速和全速PHY电源。电压范围为3.07 V~3.6 V。外部必须连接去耦电容(见表4)。 10.VDDA1V8_REG引脚是内部稳压器的输出,外部必须连接去耦电容(见表4)。 可通过BYPASS_REG1V8引脚对1.8V电压调整器进行设置,连接到VSS或VDD来激活或停用电压调整器。当VDD低于2.25 V时,1.8V调节器被强制旁路。 11.VDDA1V8_DSI是模拟DSI电源。电压范围为1.6 V~1.98V(典型值1.8 V)。应连接到VDDA1V8_REG,外部必须连接去耦电容(见表4)。 12.VDDA1V1_REG引脚是内部稳压器的输出,外部必须连接去耦电容(见表4),电压范围为1.045 V~1.155 V(典型值1.1V)。 警告:上电时。必须保证VDDA1V8_REG在VDD3V3_USBHS之前存在,否则可能导致处理器永久性损坏。必须确保PMIC或分立电源设计组件的上电顺序。 注意:所有的电源地(VSS、VSS_ANA、VSS_PLL、VSS_USBHS、VSS_DSI、VSSA和VREF-)通过电源平面连接在一起(完整接地平面)。 参考示例的IOs电平为3.3V,采用低成本的DDR3L,支持睡眠/停止/待机模式,在DDR3L上保留了LP-Stop和低功耗待机模式。 FS-MP1A开发板的电源采用分立元件组建而成,输入范围为4.5V~5.5 V,输入部分如下所示: 南风

(PA10)引脚。因此,在使用USB高速双角色端口或USB高速设备时,还必须提供VDD3V3_USBFS。如果不使用,应连接到VDD。

2.6 采用3.3 V I/Os与DDR3L的分立电源设计参考方案

输入电压:应用示例采用5V(典型的)直流电压源(VIN)供电,范围为4.0V~5.5 V。仅使用以下DC/DC降压转换器:

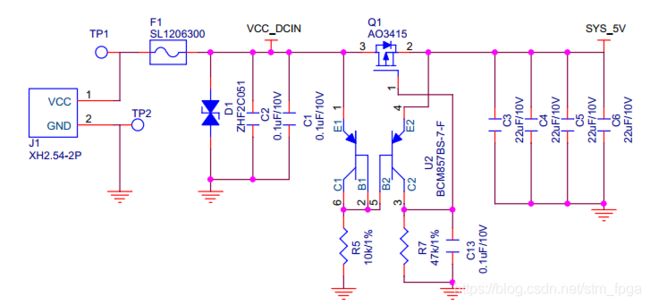

Q1、U1、R5、R7、C13组成单向供电电路,避免开发板采用USB OTG与电源适配器同时供电时产生的灌电。

SYS_3V3由MP2143DJ-LF-Z(3A,1.2MHz,40μA IQ,COT同步降压转换器)产生,可以提供最大3A连续电流,用于STM32MP157处理器的端口与外设供电。

DDR_1V35由RT8059GJ5(1.5MHz,1A,高效率PWM降压DC/DC转换器)产生,可以最大提供1A连续电流,用于STM32MP157处理器DDR部分的电源供给。

SYS_1V2由RT8097CHGB (1MHz, 2A, CMCOT同步降压转换器)产生,可以最大提供2A连续电流,用于STM32MP157处理器内核部分的电源供给。

USB部分需要保证VDDA1V8_REG在VDD3V3_USBHS的上电顺序,VDDA1V8_REG通过控制外部MOS管开关电路保证上电顺序。

通过PWR_ON引脚控制部分外设能够在待机与停止模式下关断电源,以降低功率损耗。

处理器部分的电源供给根据前文中的讲解进行连接即可实现,STM32MP1微处理器之电源篇就写到这里为止了,文中有翻译不准确或有误的地方,可以在论坛中提出以便修改,出现歧义的地方请参考官方文档。STM32MP1处理器其它外设部分的电源供给会在相应的外设部分进行讲解。

2020.09.03