MC9S12XS128 PWM输出配置

文章目录

- MC9S12XS128 PWM输出配置

-

- 一、PWM资源介绍

-

- 1.1 MC9S12 PWM特性

- 1.2 PWM 8通道8位引脚

- 二、PWM寄存器介绍

-

- 2.1 时钟选择寄存器

- 2.2 定时器通道寄存器

- 2.3 PWM 极性选择寄存器

- 2.4 PWM 使能/禁止寄存器

- 2.5 PWM 输出对齐寄存器

- 2.6 PWM 级联寄存器

- 三、PWM配置实例

MC9S12XS128 PWM输出配置

一、PWM资源介绍

1.1 MC9S12 PWM特性

- 8个具有可编程周期和占空比的独立PWM通道

- 4个时钟源

- 每个PWM通道具有专用计数器

- 每个通道可以选择有效电平极性

- 每个PWM通道可以使能 / 禁止

- 每个通道可选择输出波形的对齐方式

- 分辨率:8位(8通道);16位(4通道)

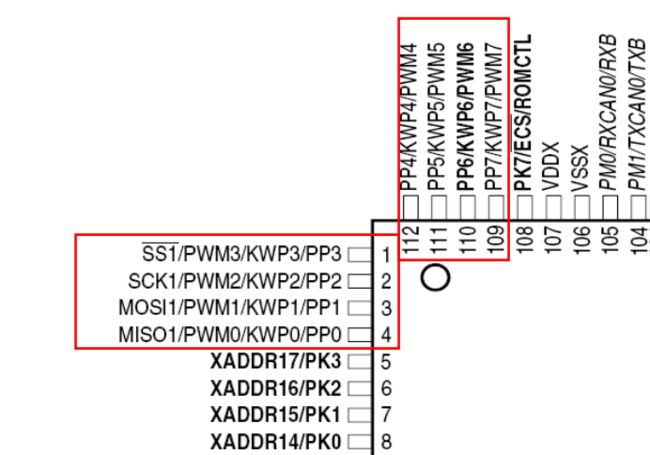

1.2 PWM 8通道8位引脚

芯片引脚分布如下:

二、PWM寄存器介绍

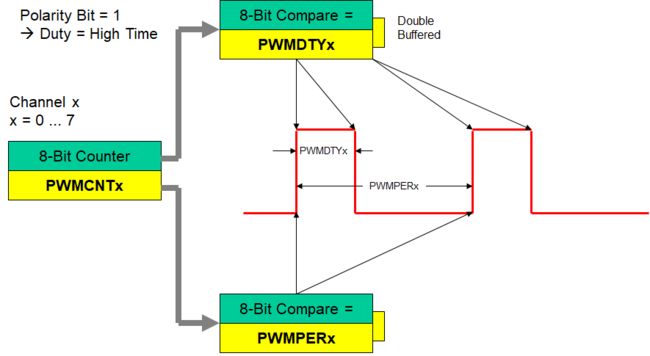

介绍寄存器前先看一下,PWM 的模块框图

从框图可以看到 PWM 的配置主要分为:时钟选择、使能、极性、对齐、PWM 通道等多个方面进行控制,下面一次介绍各个寄存器

2.1 时钟选择寄存器

2.1.1 时钟源

PWM 有四种时钟源,时钟源如下:

- Clock A (Ch 0, Ch 1, Ch 4, Ch 5)

- Clock SA (Scaled A; Ch 0, Ch 1, Ch 4, Ch 5)

- Clock B (Ch 2, Ch 3, Ch 6, Ch 7)

- Clock SB (Scaled B; Ch 2, Ch 3, Ch 6, Ch 7)

时钟源的选择通过 PWMCLK 寄存器来控制,寄存器位如下:

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| Read: Write: | PCLK7 | PCLK6 | PCLK5 | PCLK4 | PCLK3 | PCLK2 | PCLK1 | PCLK0 |

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

寄存器各个位功能

| 寄存器位 | 功能 |

|---|---|

| PCLK7、6、3、2 — PWM通道 7、6、3、2 时钟选择 | 1 = 选择Clock SB 为PWM通道 7、6、3、2 的时钟源。 0 = 选择Clock B 为PWM通道 7、6、3、2 的时钟源。 |

| PCLK5、4、1、0 — PWM通道 5、4、1、0 时钟选择 | 1 = 选择Clock SA 为PWM通道 5、4、1、0 的时钟源。 0 = 选择Clock A 为PWM通道 5、4、1、0 的时钟源。 |

2.1.2 分频器

时钟频率不能直接作为 PWM 定时器的时钟频率的,一般要经过分频才能使用,总线时钟到定时器时钟经过的分频器如下:

PWMPRCLK 寄存器用于独立选择时钟源A、B的预分频系数,寄存器结构如下:

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| R\W: | 0 | PCKB2 | PCKB1 | PCKB0 | 0 | PCKA2 | PCKA1 | PCKA0 |

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

分频值与寄存器位的关系表为:

| PCKx2 | PCKx1 | PCKx0 | Value of Clock x |

|---|---|---|---|

| 0 | 0 | 0 | Bus Clock |

| 0 | 0 | 1 | Bus Clock / 2 |

| 0 | 1 | 0 | Bus Clock / 4 |

| 0 | 1 | 1 | Bus Clock / 8 |

| 1 | 0 | 0 | Bus Clock / 16 |

| 1 | 0 | 1 | Bus Clock / 32 |

| 1 | 1 | 0 | Bus Clock / 64 |

| 1 | 1 | 1 | Bus Clock / 128 |

PWMSCLA 和 PWMSCLB对应的 A、B的定时器分频

PWMSCLA寄存器

| Read: Write: | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|---|

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

PWMSCLB寄存器

| Read: Write: | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|---|

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

定时器频率计算公式:

当 PWM 全为 0 时,分频值为 255 ;其他给多少值,分频多少

2.2 定时器通道寄存器

控制 PWM 输出波形占空比的寄存器主要有三个,

PWM Channel Counter Registers (PWMCNTx):定时计数器,按照设定的时钟频率自加,写0复位

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| Read: | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Write: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

该寄存器任何时刻可以读写,但向计数器中写入任何值会引起计数器复位到$00,且计数器方向被设置为向上计数

PWM Channel Period Registers (PWMPERx):周期寄存器,设定 PWM 的占空比周期,写255复位

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| Read: Write: | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Reset: | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

PWM Channel Duty Registers (PWMDTYx):占空比寄存器,设定 PWM 的占空比,写255复位

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| Read: Write: | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Reset: | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

2.3 PWM 极性选择寄存器

PWM Polarity Register (PWMPOL)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| Read: Write: | PPOL7 | PPOL6 | PPOL5 | PPOL4 | PPOL3 | PPOL2 | PPOL1 | PPOL0 |

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

PPOLx——Pulse Width Channel x Polarity

- 1 = PWM 通道x 周期起始时输出为高电平,当到达占空比寄存器设定值时变为低电平。

- 0 = PWM 通道x 周期起始时输出为低电平,当到达占空比寄存器设定值时变为高电平。

补充 PWMDTYx 、PWMPERx、PPOLx 三个寄存器在临界条件下,PWM 的输出情况

| PWMDTYx | PWMPERx | PPOLx | PWMx 输出 |

|---|---|---|---|

| $00 | > $00 | 1 | 低电平 |

| $00 | > $00 | 0 | 高电平 |

| xx | $00 | 1 | 高电平 |

| xx | $00 | 0 | 低电平 |

| >= PWMPERx | xx | 1 | 高电平 |

| >= PWMPERx | xx | 0 | 低电平 |

2.4 PWM 使能/禁止寄存器

PWM Enable Register (PWME)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| Read: Write: | PWME7 | PWME6 | PWME5 | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Channel x Enable

- 1 = PWM 通道x 使能。

- 0 = PWM 通道x 禁止。

2.5 PWM 输出对齐寄存器

MC9S12 的 PWM 输出有两者对齐方式,左对齐和中央对齐

左对齐

在左对齐模式中,8位计数器配置为向上累加计数器,它和占空比寄存器和周期寄存器两个寄存器比较。当PWM 计数器和占空比计数器中的值相等,输出翻转,PWM 计数器和周期寄存器的值匹配时复位计数器并同时从双缓冲器中载入周期和占空比计数器值。计数器从0计数,到周期寄存器-1结束

中央对齐

这种模式下8位计数器作为一个向上&向下计数器,当计数器值为0时,向上计数。计数器和占空比寄存器及周期寄存器比较,当PWM 计数器和占空比寄存器值相匹配时,输出翻转,PWM 计数器和周期寄存器匹配改变计数器方向,从向上计数变为向下计数,当PWM计数器递减,和占空比计数器再次匹配时,输出再次改变。当PWM计数器递减到0,计数方向从向下计数变为向上计数,并从双缓冲器中载入周期寄存器和占空比寄存器值。计数器从0加到周期寄存器中的值并减回0,因此有效周期为PWMPERx*2

PWM Center Align Enable Register (PWMCAE)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|

| Read: Write: | CAE7 | CAE6 | CAE5 | CAE4 | CAE3 | CAE2 | CAE1 | CAE0 |

| Reset: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

CAEx — Center Aligned Output Mode on channel x

- 1 = 通道x 以中央对齐输出方式工作。

- 0 = 通道x 以左对齐输出方式工作。

2.6 PWM 级联寄存器

2个8位PWM 通道可以被连接成一个16位 PWM通道,如下图

级联后的 PWM 通道数以及对应寄存器如下

| CONxx | PWMEx | PPOLx | PCLKx | CAEx | PWMx OUTPUT |

|---|---|---|---|---|---|

| CON67 | PWME7 | PPOL7 | PCLK7 | CAE7 | PWM7 |

| CON45 | PWME5 | PPOL5 | PCLK5 | CAE5 | PWM5 |

| CON23 | PWME3 | PPOL3 | PCLK3 | CAE3 | PWM3 |

| CON01 | PWME1 | PPOL1 | PCLK1 | CAE1 | PWM1 |

PWM Control Register (PWMCTL) 级联控制寄存器

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| CON67 | CON45 | CON23 | CON01 | PSWAI | PFRZ | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

CONxy——Concatenate channels x and y

- 1 = 通道x和y被连接成一个16位PWM通道。

- 0 = 通道x和y为两个独立的8位PWM。

三、PWM配置实例

配置 PWM 一般按照下面6步骤配置()内是相关的寄存器

- 禁止PWM (PWME)

- 选择PWM时钟,预分频和分频 (PWMPRCLK, PWMSCLA, PWMSCLB, PWMCLK)

- 选择极性(PWMPOL)

- 选择对齐方式 (PWMCAE)

- 编程占空比和周期 (PWMDTYx, PWMPERx)

- 使能PWM (PWME)

初始化子程序示例

void PWM_Init(void)

{

PWME = 0x00; //禁止PWM模块

PWMPRCLK = 0x06; //CLOCKA的预分频设置为6

PWMSCLA = 125; //SA的分频因子设置为125

PWMCLK = 0x01; //通道0选择SA作为PWM时钟

PWMPER0 = 200; //通道0周期寄存器设置为200

PWMDTY0 = 0; //通道0占空比寄存器设置

PWMPOL = 0x01; //PWM输出先为高电平,之后变为低电平

PWMCAE = 0x00; //左对齐输出

PWMCTL = 0x00; //不级联

PWME = 0x01; //使能PWM通道0

}