处理器芯片开源设计与敏捷开发方法思考与实践

【本文发表在最新一期《中国计算机学会通讯(CCCF)》】

处理器芯片开源设计与敏捷开发方法思考与实践

包云岗,张科,孙凝晖

中国科学院计算技术研究所

处理器芯片是中国半导体产业的软肋,如何破解中国半导体产业面临的“卡脖子”问题,各界都在积极实践与探索。本文从分析降低芯片设计门槛的三大需求出发,提出可借鉴互联网产业的开源理念,通过构建开源芯片生态来应对。同时,进一步梳理构建开源芯片生态的四个要素,提出可通过打造芯片敏捷开发平台来落地,并介绍中科院计算所开发平台方面的近期进展。

一、降低芯片设计门槛的三大需求

(1)应对摩尔定律终结的技术发展需求

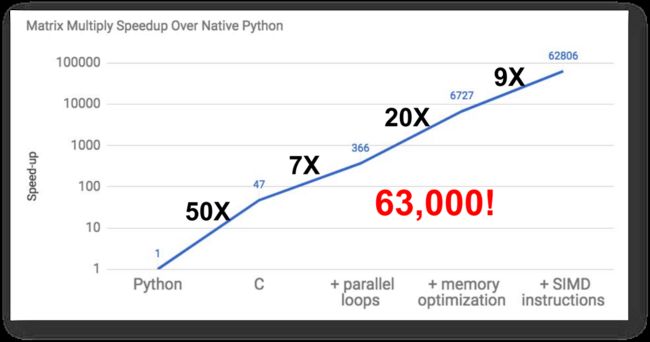

摩尔定律逐渐走向终结,但摩尔定律赋予芯片的能力并未充分挖掘出来。如图1所示,以实现一个矩阵乘法为例,普通程序员写的程序和懂体系架构的专家写的程序在性能上甚至会差63000倍 [1] 。因此,如果将面向某个特定领域的专家知识实现到芯片中,就有可能将性能功耗比提升几百甚至几千倍,从而充分挖掘芯片上晶体管的潜力。但这种领域专用体系结构 (DSA) 会带来碎片化问题,需要从芯片设计成本与周期两个维度同时降低门槛,才能应对种类繁多的领域专用加速器。

图1. 矩阵乘法不同实现的性能差别[1]

(2)激发创新活力、繁荣芯片产业的市场需求

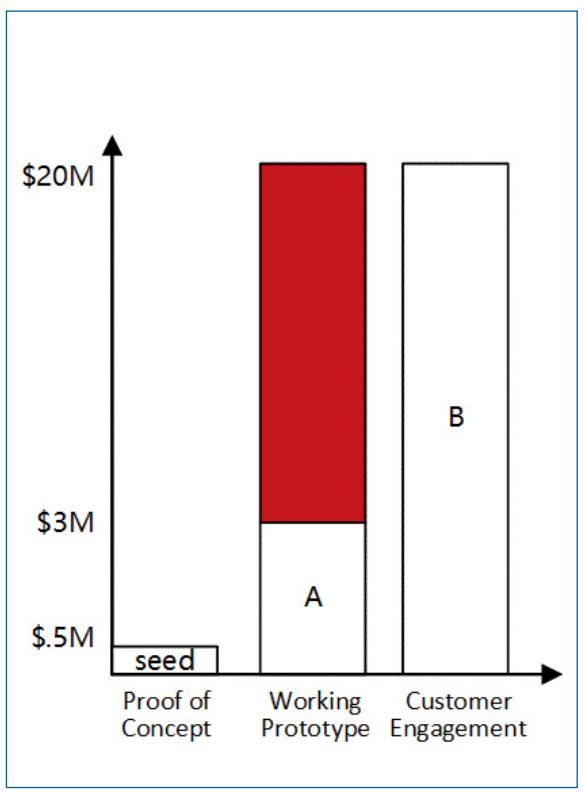

长期以来芯片研发成本高、周期长,导致了该领域的高门槛,严重阻碍了创新。即使研制一款中档芯片,也往往需要数百人年、数千万甚至上亿美元的研发投入,导致社会资本不愿投资。因此,只有少数企业才能承担,资本市场对芯片投资也是极其谨慎保守,影响整个产业的繁荣。图2显示传统初创企业种子轮/A轮/B轮融资额度稳步提升,但芯片初创企业A轮就需要2000万美元 [2],这严重制约了芯片领域的创新活力。

图2. 芯片初创企业创新门槛高

(3)培养高水平芯片设计人才的教育需求

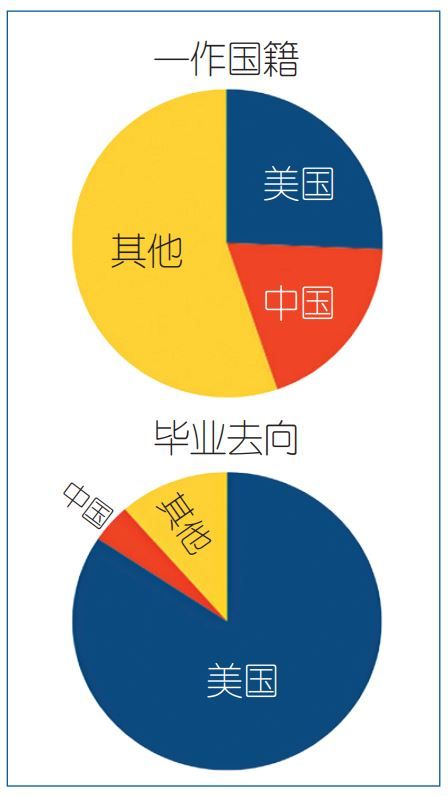

中国芯片领域面临的“卡脖子”问题根源在于优秀人才储备严重不足。我们统计了芯片架构研究优秀人才(以体系结构顶级会议ISCA论文第一作者作为采样样本)的毕业去向。统计数据显示,过去十年(2008~2017年)这些优秀人才 85%选择在美国就业,仅有 4%在中国就业,差距巨大(图 3)。这与当前芯片设计门槛过高,导致中国大学无法开展芯片相关教学与研究密切相关。

这种人才危机美国也曾经历过,1982 年全美上千所大学中只有不到100 位教授和学生从事半导体相关的研究[3] 。为了应对人才危机,美国国防部高级研究计划署 (DARPA) 在1981年启动MOSIS 项目,为大学提供流片服务,通过MPW模式大幅降低芯片设计门槛。30 余年来MOSIS为大学和研究机构流了60000多款芯片,培养了数万名学生[4]。因此,降低芯片设计门槛可大幅提高人才培养效率。

图3. ISCA2008~2017年论文一作情况

由此可见,从学科自身发展、产业创新活力与人才培养三个角度,都希望降低芯片设计门槛,但应该如何实现?

二、构建开源芯片生态是降低芯片设计门槛的有效途径

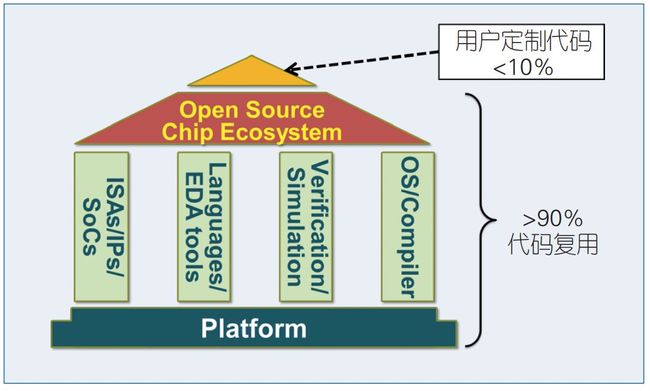

开源软件生态是一个降低互联网创新门槛的成功例 子。事实上,中国互联网产业的成功正得益于开源软件的广泛应用。开源软件为互联网产业带来两大作用:一方面开源软件提供了90%的基础功能, 允许开发者专注于10%的创新功能,这降低了互联网领域创新门槛,培育了“大众创业、万众创新”的土壤,从而使3~5位开发人员在几个月时间里便能快速实现出滴滴、摩拜单车等互联网新兴业务的原型,繁荣了整个互联网产业,培养出大量优秀技术人才,也吸引了许多海外人才回国投身互联网产业 ;另一方面开源软件允许开发者自由获取源代码、文档等,提高了互联网企业的安全可控能力, 让它们在软件关键技术方面不再面临“卡脖子”问题,从而让中国的互联网企业能与硅谷企业在同一起跑线上竞争,甚至在共享经济、移动支付等领域更具竞争力。

芯片设计过程与软件开发有很多相似之处。自 上世纪 80 年代 Verilog/VHDL 硬件描述语言与综合器技术逐渐成熟,芯片设计的过程也转变为用编程语言编写代码,与软件开发类似。因此,借鉴开源软件的成功理念,将处理器芯片设计开源(即将硬件描述语言编写的处理器设计代码开源),并进一步构建开源芯片生态,有望实现大幅降低芯片开发的门槛——数量级地降低芯片开发费效比,将开发成本从几千万甚至上亿元降低至几百万甚至几十万元, 并将整个芯片及硬件开发周期从几年降低至几个月。

三、打破开源芯片“死结”的机遇

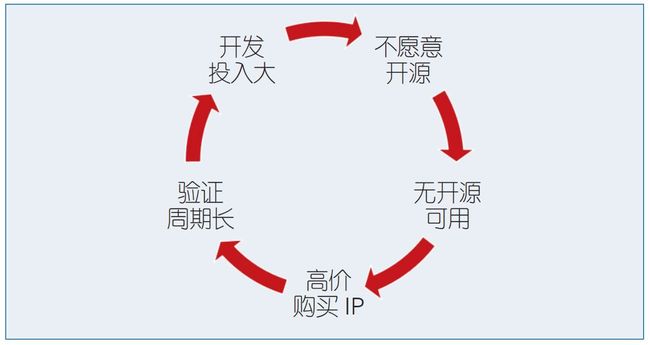

当前开源芯片仍存在“死结”(如图 4)。具体而言,芯片设计阶段需要投入大量的人力、电子设计自动化 (EDA)和IP成本,因此开发人员或企业不愿意将其设计的芯片与IP开源 ;这导致业界与社区无高质量的开源芯片与 IP 可用,于是企业只能购买高价的 IP ;这进一步推高了开发代价,导致企业希望充分验证设计来提高流片的成功率,这又需要投入更多的人力和时间进行验证⋯⋯如此循环,最终形成了一个“死结”。

图4. 开源芯片“死结”

通过深入的调研并结合近年来的一些实践经 验,中科院计算所团队分析了国内外开源芯片生态发展现状与趋势[5] ,认为随着开放指令集(如 RISC-V)、硬件描述新语言(如 Chisel [6] )、硬件生成器敏捷开发模式、开源 EDA 工具、云计算等技术涌现与普及,多种技术之间相互组合并不断产生新的“化学反应”,促进开源芯片发展到了一个新的转折点,因此开源芯片面临的“死结”有望被打破。

但是构建完善的开源芯片生态是一个长期而艰巨的系统工程,正如今天开源软件生态也是 20 余年积累而成。目前的开源芯片生态就如 1990 年代初的开源软件生态,全世界范围都处于起步阶段,尚无法构成一个独立 (self-contained) 生 态——即完全采用开源模式,用开源EDA工具链开发开源 IP,进而完成开源 SoC 芯片设计。

四、构建开源芯片生态的四要素

要实现开源芯片生态目标,我们认为需要在四个方面积极投入(如图 5)并取得突破 :(1) 开放指令集、开源IP与SoC设计 ;(2) 开源EDA工具链 ;(3) 低成本的芯片开发验证平台 ; (4) 快速适配芯片的系统软件。

图5. 开源芯片生态要素

(1)开放指令集、开源 IP 与 SoC 设计

“指令集→处理器核→ SoC 芯片”是芯片设计的三个阶段,每个阶段均存在三种模式 :开放免费 (open & free)、可授权 (licensable)、封闭 (closed)。

在 2010 年左右,加州大学伯克利分校 (UC Berkeley) 认识到只有基于开放的指令集,才能实现开源处理器核以及开源 SoC 芯片。因此他们推出了 一套开放指令集 RISC-V,允许全世界免费自由地使用 RISC-V 指令集规范设计各自的处理器。但值得一提的是指令集 (ISA) 仅仅是规范标准,往往用一本书甚至几张纸即可描述,需要根据规范编写出相应的源代码,才是处理器核。因此仅有开放指令集还远不足以构建开源芯片生态,还需要一系列开源的 IP 和 SoC 设计。

开源IP和SoC设计要成为主流需要解决两个问题 :一是解决 IP 核的质量控制难题。开源 IP 核并不是一种新的模式,事实上提供开源 IP 核的OpenCores 社区已经存在了 20 年,到如今已经拥有超过 30 万会员。但是 OpenCores 存在的核心问题是绝大多数开源 IP 核未经严格测试验证,质量不可靠。解决 IP 质量控制问题可以从两方面入手, 首先是完善芯片敏捷开发流程,通过 Chisel 这样的具有更高抽象的硬件描述语言,实现基于一套代码同时生成用于测试的仿真模拟代码以及用于流片的代码,提高测试效率,快速定位错误,从而改善 IP 核质量 ;其次实现 IP 核与工艺库高效对接的流程,从而推进 IP 核达到可流片的成熟度,并通过建立快速流片认证与测试机制,为开源社区提供经过流片验证的 IP 核组合。通过这两种方式积累出一定数量的高质量 IP 核,就可以形成支持 90% 重用的开源 SoC 框架.

二是可扩展的松耦合架构支持社区协作开发。传统处理器采用紧耦合架构,模块之间的交互非常紧密,不利于开源社区多人协作开发,也不利于用户的自定义扩展。传统基于互连总线的可扩展方式具有较好的灵活性,但编程与访存效率低下, 需要软件显式地进行数据移动。基于 RISC-V 进行可扩展指令是一种更高效的机制,但仍需要深入研究。

对比开源软件生态,大型开源软件的多人协作开发模式已经比较成熟,面向对象思想、微内核思想等一系列新技术与理念使大型软件开发可分解、 可扩展、可组合,这些思想与理念值得处理器设计领域学习与借鉴。

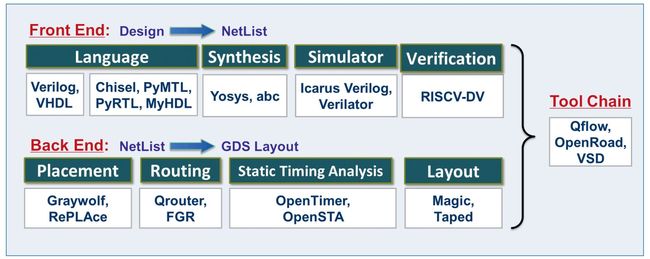

(2)开源 EDA 工具链

开源 EDA 工具链涉及硬件开发语言与综合、 布局布线工具,类比于开源软件生态中的编程语言与编译器。

如今工业界广泛使用的硬件描述语言 Verilog 已经是 1980 年代初的产物,一直沿用到今天。但相 比于软件领域,几乎每十年都有更高效、更抽象的开发语言出现,比如 C、C++、Java、Python、Go、 Rust 等。近年来,硬件开发语言开始出现变革, Chisel、PyMTL[7] 等更高抽象的硬件开发新语言涌现出来。以 Chisel 为例,它基于函数式语言 Scala, 通过元编程、面向对象、函数式编程等诸多高级特 性,极大地提升了开发效率。我们团队前期研究工作也证明了 Chisel 比传统 Verilog 在开发效率方法可提升一个数量级,且具有相当的开发质量 [8] 。

近年来, 在DARPA 的支持和推动下,出现了越来越多的开源EDA项目。如图 6 所示,在芯片设计的前端(从RTL到网表)与后端(从网表到GDS版图)均有一系列开源工具组件。同时也出现像 Qflow、OpenRoad、Hammer 等开源EDA框架。我们通过实验验证了现有开源 EDA 工具链已经可以满足小规模芯片开发——基于中芯国际 180nm 工艺库,使用全开源 EDA 工具链可将一个 32 位的 RISC-V 开源核生成 GDS 版图。但是,当前开源EDA工具链的挑战是在先进工艺支持、稳定性和可用性方面仍与商业版有很大差距。

图6. EDA 工具链的开源组件

未来,提升开源 EDA 工具链质量可在四方面加强研究 :一是与先进工艺库有机结合,二是提高开源组件的算法效率,三是针对领域专用加速器设计定制开源 EDA 组件,四是更好地支持 Chisel 等更高级硬件描述语言。今年 8 月在 CCF容错大会上, 北京大学、中科院计算所、清华大学、复旦大学等国内十余所大学与研究机构共同发起了 OpenBelt 倡议,将会在开源 EDA方向积极投入,做出中国的贡献。

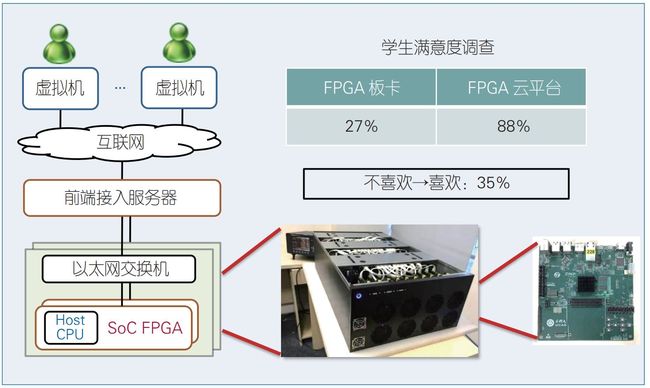

(3)低成本的芯片开发验证平台

芯片开发过程中的模拟仿真与验证环境是非常耗时耗钱的环节,一些加速仿真平台(如 Cadence 的 Palladium 平台)甚至单台价格就达上千万元人民币。是否有可能将模拟仿真与验证的成本降低 1~2 个数量级?我们认为基于云租赁模式可降低这方面的门槛。而基于云平台进行芯片开发、仿真与验证平台将是未来趋势,尤其是针对中小企业用户。

过去几年我们在中国科学院大学开展了基于FPGA 云平台的本科生处理器芯片设计教学实践。两年来已为 200 多位中国科学院大学本科生提供基于 FPGA 教学实验云的 CPU 模块仿真与原型验证,取得了显著效果。相比在实验室固定位置利用调试线缆直接接入 FPGA 板卡的方法,使用云模式可以随时随地访问 FPGA 资源,学生满意度从 27% 跃升到 88%, 并且有 35% 的学生从不喜欢变成喜欢芯片设计与体系结构方向。这是国际上最先采用 FPGA 云开发的处理器芯片设计教学实践,发表于 2019 年度计算机教育旗舰会议 (ACM SIGCSE) [9] 。这项科教融合的工作也给我们极大的鼓舞——降低芯片设计门槛确实有助于人才培养。

图7. 基于 FPGA 云平台的国科大教学实践效果

FPGA 云平台只是芯片设计过程中的一个环节,要更大幅度地降低成本,还需进一步与公用云平台结合,支持运行开源 EDA 工具链、下载与集成开源 IP 核的开源 SoC 芯片完整开发流程,实现构建更完善的芯片开发 / 验证 / 测试云平台。

国际一些大学与企业也在朝着这个方面努力 :加州大学伯克利分校基于亚马逊F1 FPGA云平台研制了 FireSim平台,目标是构建使用 FPGA 加速的时钟级精确的全系统硬件模拟平台 ;SiFive 公司正在研发的 DesignShare 平台则希望在云平台上提供芯片开发所需要的各种资源,包括 IP 库、 EDA 工具链等 ;Astera Lab 与 Synopsys 合作,实现了完全在云上进行设计与验证的 SoC。

(4)系统软件与开发环境

上述三方面的目标是允许开发者重用 90% 的已 有功能、只需专注 10% 的创新功能,从而数量级降低芯片开发成本与周期。而快速经济地定制领域专用芯片是应对物联网 (IoT) 面临的“昆虫纲”挑战(碎 片化问题)的有效途径。但这对系统软件与软件开发环境如何能快速适配新芯片则是很大的挑战。

当一款新的芯片推出,软件需在三个层次予以适配 :第一层是操作系统与编译器,针对新扩展的指令或者新加的传感器等 ;第二层是功能软件层, 如 Apache、MySQL 等;第三层是面向用户和程序员, 需要为用户提供易用的操作方式,也需要为程序员提供更好统一的 API,就如移动领域安卓的作用。

五、中科院计算所近期进展

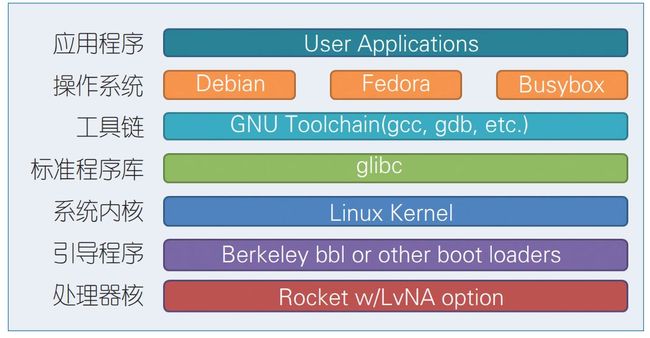

中科院计算所过去几年在 RISC-V、Chisel 和 FPGA 云平台等方面积累了丰富的实践经验。近期, 我们正式对外开放了自行研发的一套基于 RISC-V 的 面向开源芯片设计的系统级验证和原型 SERVE 平台(System Emulation and Prototyping for RISC-V Environment),如图 8 所示。SERVE 平台基于目前市场上主 流的 SoC-FPGA 可编程逻辑器件及板卡,涵盖 r、i、 s、c、v 五个版本,分别是 :精简普及型 (SERVE.r)、 高性能增强型 (SERVE.i)、多节点集群型 (SERVE.s)、 云化服务型 (SERVE.c) 以及支持标签化冯·诺伊曼体系结构 LvNA 版本 (SERVE.v) 等多种不同规格版本, 满足不同类型用户进行 RISC-V 软硬件系统级协同设计及验证评估的差异化需求,如图 8 所示。

图8. SERVE:基于 RISC-V 的面向开源芯片设计的系统级验证和原型平台

与国内外现有 RISC-V 的 FPGA 系统级验证平台相比,SERVE 平台实现了 RISC-V 硬件系统的独立自治,可在上电后自动运行并直接控制平台上真实的物理接口 ;同时 SERVE 支持在 RISC-V 处理器核上运行标准 Linux 和 Debian 等主流软件生态,便于用户快速开展各类 RISC-V 系统级研究工作(如 图 9)。目前 SERVE 平台的相关源码已在鹏城实验室 iHUB 托管平台上全面开源 。

图9. SERVE 平台支持全系统开发

目前我们正在进一步扩展 SERVE 平台,使其成为一个有机集成开源芯片生态四方面要素的芯片设计平台,并结合“一生一芯”人才培养计划,第一阶段实现使本科生能在该平台上用开源的 EDA 工具链开发开源 SoC 芯片。

六、总结与展望

开源芯片生态仍处于起步阶段,中国的学术界 与企业界对开源芯片还存在诸多质疑与不解,需要在两方面扭转观念。

一方面,加强对开源芯片的价值与意义的认 识与理解。相比而言,美国各界已经达成共识,均 开始积极投入。本文一作受邀参加 2019 年 6 月远 景研讨会(SIGARCH Visioning Workshop)并作报告。 整个远景研讨会共有 11 个报告,包括 ACM 图灵奖 得主大卫·帕特森 (David Patterson) 教授、多位美国 工程院院士,还有来自麻省理工学院 (MIT)、加州 大学伯克利分校 (Berkeley)、斯坦福大学 (Stanford)、 加州大学圣迭戈分校 (UCSD)、谷歌 (Google)、英伟 达 (NVIDIA)、美国国防部高级研究计划署 (DARPA) 等顶尖大学、企业和政府机构的专家。而本文作者 成了唯一的一位来自美国以外的报告人,也反映出 国内在开源芯片方向的研究力量还比较薄弱。但同时也要认识开源处理器方法的外延,避免建立 不恰当的期望,因为并不是所有芯片都能在短 期内用开源芯片方式来设计。未来 3 年内开源处 理器的最佳切入点还是以面向物联网的 AIoT 芯片 为主。这些芯片对功耗、成本、开发周期等需求较 为敏感,对制造工艺节点并不高,28nm、40nm 甚 至 65nm 即可满足。随着开源芯片生态的不断成熟, 相信一些开源组件和技术将会被应用到大型高端芯片的设计开发中,就如今天许多商业软件企业如微软等也会积极使用开源软件一样。当然这会需要相当长的一段时间。

另一方面,中国各界需要改变“开源芯片就 是 RISC-V”、“开源就是公开源代码”的片面观念。 一方面,开源芯片涵盖的内容很广,RISC-V 只是其中一部分。RISC-V 指令集规范可类比于操作系统领域的 POSIX 系统调用标准,而开源 RISC-V 处理器核则可类比于 Linux。正如开源软件涵盖的内容要远远超过 Linux,还包含 GCC/LLVM 等编译器、 Python/Go等编程语言、Apache/MySQL/Spark等软件、 GitHub 等托管平台等,开源芯片涵盖的内容同样也 很广,除了 RISC-V 以外还包括外围 IP、EDA 工具、 验证工具等。另一方面,处理器开源并不仅仅是将源码公开,而是一种对处理器设计方法的变革,这需要大量基础研究。事实上 6 月份举办的 远景研讨会报告主题也是很好的体现,涵盖了处理 器核的自动生成技术、更高抽象的硬件开发语言、 敏捷开发工具、领域专业设计语言、EDA 工具链的 智能化、端到端形式化验证等(详细内容请阅读《远景研讨会纪要:面向下一代计算的开源芯片与敏捷开发》)。开源芯片打开了 一个充满各种新挑战的学术新疆域。

因此,在此也积极呼吁国内有更多人能参与一起构建开源芯片生态。如果中国能主导开源芯片生态的构建,将有助于提升中国在半导体芯片领域的人才储备、供应链安全、技术自主能力与国际竞争力。

致谢

感谢普林斯顿大学李凯院士的具体指导。感谢中科院计算所李国杰院士、中国开放指令生态 (RISC-V) 联盟理事长倪光南院士、北京大学 / 鹏城实验室高文院士、国防科技大学廖湘科院士、中科院计算所首席科学家徐志伟研究员、RISC-V 基金会中国委员会主席方之熙博士等资深专家的支持和鼓励。感谢中科院计算所先进计算机系统研究中心开源芯片设计工作组的辛勤付出,感谢深圳鹏城实验室、北京智源人工智能研究院的支持。

作者简介

包云岗 CCF 理事、CCCF 专栏主编、CCF 普及 工委主任。中科院计算所研究员,先进计算机系统研究中心主任。主要研究方向为计算机系统结构。 [email protected]

张科 CCF 高级会员、计算机工程与工艺专委委员。中科院计算所高级工程师,中国科学院大学岗位教师。主要研究方向为计算机系统结构与异构加速计算。 [email protected]

孙凝晖 CCF 副理事长。中国科学院计算技术研究所研究员。主要研究方向为计算机体系 结构、高性能计算机。 [email protected]

参考文献

[1] David Patterson. A New Golden Age for Computer Architecture: History, Challenges, and Opportunities, 2018

[2] Serge Leef, DARPA, Automatic Implementation of Secure Silicon, SIGARCH Visioning Workshop, 2019

[3] Ralph Cavin, SRC: Celebrating 30 Years, 2012.

[4] http://www.mosis.com

[5] 中国开放指令生态(RISC-V)联盟,开放指令集与开 源芯片发展报告 , 2019.1.

[6] Jonathan Bachrach, Huy Vo, Brian Richards, et al. Chisel: constructing hardware in a Scala embedded language[C]// Proceedings of the 49th Annual Design Automation Conference (DAC). 2012

[7] D. Lockhart, G. Zibrat, C. Batten. "PyMTL: A Unified Framework for Vertically Integrated Computer Architecture Research." 47th ACM/IEEE Int'l Symp. on Microarchitecture (MICRO-47), Dec. 2014.

[8] 余子濠 , 刘志刚 , 李一苇 , 黄博文 , 王卅 , 孙凝晖 , 包 云岗 . 芯片敏捷开发实践:标签化 RISC-V[J]. 计算机 研究与发展 , 2019, 56(1): 35-48

[9] Zhang K, Chang Y, Chen M, et al. Computer Organization and Design Course with FPGA Cloud[C]// Proceedings of the 50th ACM Technical Symposium on Computer Science Education (SIGCSE '19), 2019.