沧小海笔记之xilinx 7系列的时钟架构(下)

四、时钟资源介绍

4.1 BUFG

BUFG在“Device”中如图2-1-1所示,其中它有多种模式可根据需求来选择使用,可以实现将时钟传递到FPGA中的各种资源,具体架构在上文已做阐述,本文就对BUFG本身特性进行详细的说明。

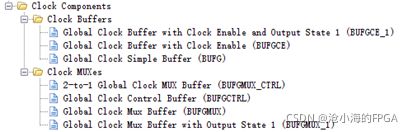

如下图是关于BUFG的所有原语,主要分为两个部分,一部分是带有各种功能的BUFG,另一种是用于时钟选择的BUFGMUX,这部分内容在《UG472》和》《UG768》均有介绍。

1、BUFGCTRL

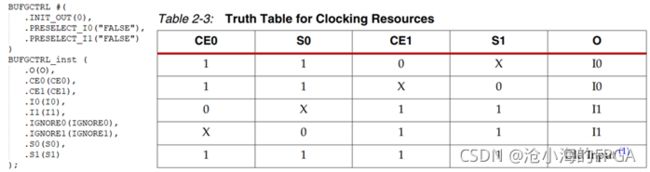

BUFGCTRL保留了该缓冲器的所有接口,有四个选择线S0、S1、CE0和CE1,两条额外的控制线IGNORE0和IGNORE1。这六个控制线用于控制输入信号I0和I1的输出。如同3-1-3是BUFGCTRL的真值表。

图3-1-3 BUFGCTRL真值表

其中“O”是输出时钟,I0和I1是出入时钟,其它六个信号是用不用控制的,CE是使能信号,S是选择信号,IGNORE是旁路信号。这也是为啥CE和S都是1的时候才能表示选择了该路,所以这两个信号都可以用于时钟选择,例如S1和S0都是1,用CE进行选择,或反之。CE和S也是有区别的,CE用于选择需要保证建立时间和保持时间,否则会出现毛刺,用S没有这个问题,顶多晚一个时钟周期,我觉得用S比较好。

IGNORE本身就是忽视的意思,从《ug472》的第40页来看置1就忽视了对应的时钟属于与选择,但仿真来看是置0就忽略了对应时钟和选择,所以还是按照实际的来吧。

BUFGCTRL还有三个配置参数,其中INIT_OUT有三个作用,确定初始输出值、敏感沿和切换后的时钟电平。如果设置0则初始输出为低电平,在下降沿时切换且切换后的是低电平。PRESELECT是预选择时钟的意思,选择“true”表示就使用对应时钟,无论怎么操作都不会改变的,但仿真看不是,可能是有区别吧。

了解了BUFGCTRL,其他时钟也就好说了,因为都是在这基础上的更改。

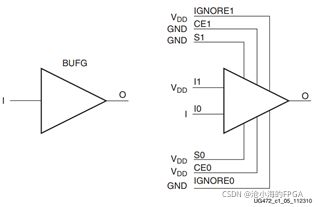

2、BUFG

BUFG如下所示,选择使能等位置固定置,输入即输出,这也是用的最多的BUFG。

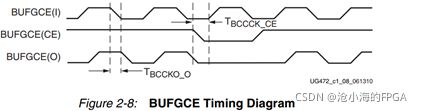

3、BUFGCE和BUFGCE_1

如下图所示,也就是加了一个使能信号,是用的CE0,也可以用CE1,是没有区别的。

如下是时序图

3、BUFGMUX and BUFGMUX_CTRL

是用来做时钟选择的,这个有两个,从样子上看没啥区别,实际上就是选择用S和CE的差别,这也导致了在时钟切换时候的时序差别。

4.2 区域时钟

4.2.1 CC

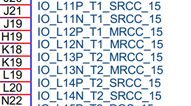

“Clock-Capable”是时钟功能的意思,外部时钟信号必须通过具有时钟功能的引脚接入FPGA,这个引脚称之为MRCC和SRCC。如下图原理图所示,每个BANK有两个MRCC,即Multi-region clock-capable I/O,多区域时钟功能I/O。每个bank有两个SRCC ,即Single-region clock-capable I/O,单区域时钟功能I/O。它们都是差分的,如果接单端时钟则需接到“P”上,对应的“N”引脚不可用。

根据《ug472》第24页介绍,这两种信号可以连接到

1、同BANK也就是同时钟域的4个BUFIO、4个BUFR和2个BUFMR

2、本BANK或上下BANK CMT的MMCM和PLL

3、连接到16个BUFG,也就是处于同一侧的

4、同时钟域的BUFH

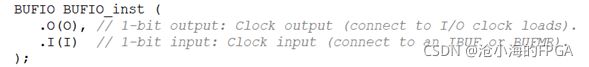

4.2.2 I/O Clock Buffer—BUFIO

每个BANK都有这么四个BUFIO,输入时钟与输出时钟有一定的相位延迟。BUFIO可被MRCC、SRCC、MMCM的CLKOUT0到3、CLKFBOUT以及同一时钟域和上下时钟域的BUFMR驱动,而BUFII仅可驱动IO BANK的ILOGIC和OLOGIC相关时钟,所以BUFIO是区域时钟。因此,BUFIO非常适合源同步数据捕获。

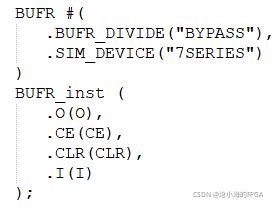

4.2.3 Regional Clock Buffer—BUFR

这是7系列中可用的另一个区域时钟缓冲器,位置就在BUFIO旁边,支持的驱动源于BUFIO一致,但它可用连接到BUFG和CMT,进而引入逻辑中去。如下图是BUFR的原语“BUFR_DIVIDE”是确定输出时钟分频比的,可用是1到8,如果选择“BYPASS”则不分频。“O”是时钟输出,CE是异步的输出时钟使能端口,在“BYPASS”模式下不能用,“CLR”分频逻辑异步清零,并将输出设置为低电平,不能在旁路模式下使用。

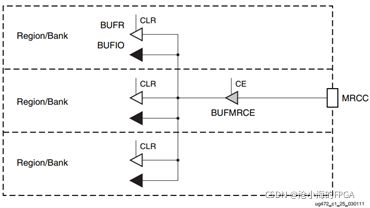

4.2.4 Regional Clock Buffer—BUFMR/BUFMRCE

BUFMR也是区域时钟,每个I/O bank都有两个,可由MRCC、GT的CLK驱动,它可以驱动本BANK和上下相邻BANK的BUFIO和BUFR,起到了扩展连接的作用。

如下图是BUFMR的原语,其中“INIT_OUT”是初始化BUFMRCE输出指定的值,“CE_TYPE”是设置CE与时钟的关系,是同步“SYNC”还是异步“ASYNC”。

4.2.4 水平时钟缓冲器——BUFH

BUFH(Horizontal Clock Buffer)水平时钟缓冲器也是个区域时钟,每个BANK有12个BUFH,用来驱动本BANK的各种资源,BUFH相比较BUFG抖动和功耗都更低。BUFH可以由MMRC、SRCC、MMCM的CLKOUT0到3、CLKFBOUT、和来自同一时钟域(同一bank)和上下相邻BANK的BUFMR,输出时钟可以连接到CMT、BUFG和逻辑资源。如下图是BUFH的两个原语,一个不带CE一个带CE的,与BUFMR差不多,就不在赘述了。

第五章 CMT的介绍

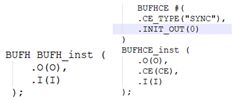

在7系列FPGA中,时钟管理块(CMT)包括混合模式时钟管理器(MMCM)和锁相环(PLL)。PLL可以说是MMCM的阉割版。 每个BANK至多包含一个CMT,具体视芯片资源而定,如下图是CMT的框图,可见输入到CMT也就是PLL或MMCM的时钟可以有多种选择,甚至是本地逻辑路由,但并不建议这样搞,输出时钟会连接到BUFH或者BUFG,这些如果没有特殊要求都会自动实现的。

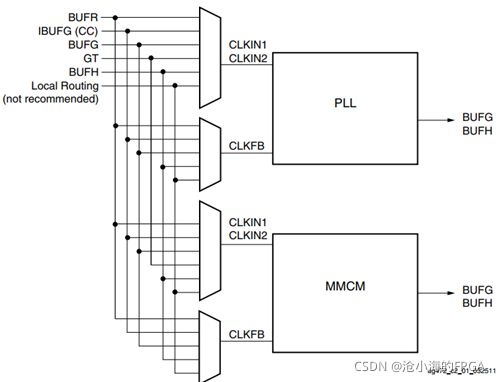

无论是MMCM还是PLL,其功能实现的基本原理是一致的,如下图所示是MMCM产生多个时钟的流程图。每个时钟输入都有一个可编程的计数分配器,也就是“D”,可控制对输入时钟进行分频,PFD是相位检测器,用来比较输入时钟和反馈时钟上升沿的相位和频率进而生成与两个时钟之间的相位和频率成比例的信号,这是一个上升或下降的信号,该信号驱动电荷泵(CP)和环路滤波器(LF)产生VOC的参考电压。当VCO频率过高时,PFD会激活一个下降信号,从而将电压降低,上升信号将增加电压抬高频率。VOC即压控振荡器(Voltage Controlled Oscillator),就是输出频率与输入控制电压有对应关系的振荡电路,有LC和RC压控振荡器,一般用的是RC的。MMCM原理是在VCO输出时钟的基础上可对其进行分频、相位和占空比的调整,已产生我们所需时钟。

CMT具有时钟矫正网络,可实现输出时钟频率与输入时钟频率相位一致,这就为需时钟同步的相关设计提供便利,最起码不需要在这基础上花费时间调整时钟相位,并且具有抖动滤波的功能。我们可以调用相关原语或IP核来实现相关设计。

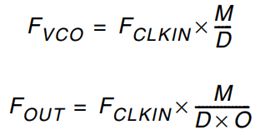

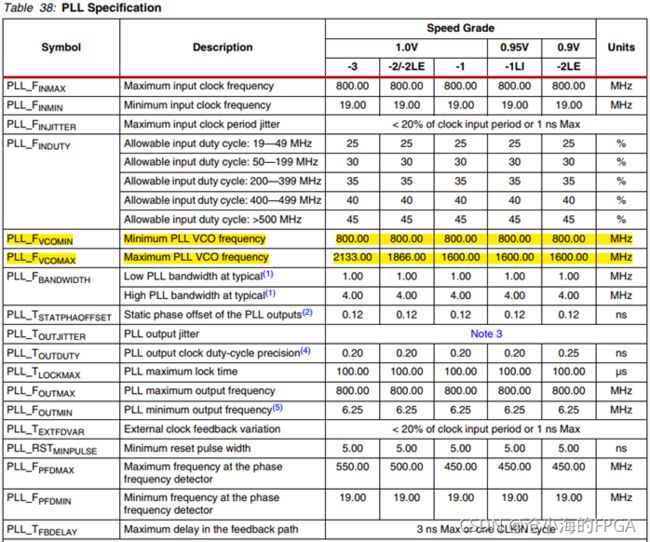

根据上述描述可知,根据CMT产生所用时钟的原理就是首先产生VCO这个基础时钟,然后在其基础上进行分频得到我所需时钟,具体公式如下所示,其中“M”和“D”是可编程控制的,而且CVO的频率也是有限制的,在《DS181》有相关描述,如下表所示。“O”是每路输出时钟对应一个。就CMT内部而言,输出时钟频率的产生有两种情况,一种是仅适用整数除法进行频率合成,另一种是使用小数分频产生所用时钟,为什么要分这两种呢,因为用整数除法我们可以调整时钟占空比,用小数则不能调整,而这个是其内部自动选择的,我们只需知道即可。

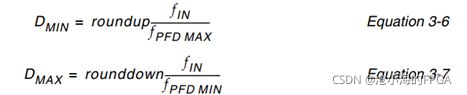

那么我们如何去确定VCO频率呢?在UG472给出了方案,其中PFD是有频率限制的,这在上表中也有描述,例如上表写着不得低于19M,不得高于550或其他。所以由此可以确定D的最大值和最小值,如下

VCO也有频率限制,如上表不得低于800M,不得高于一定值。所以当确定D的值后,M的范围也可大致确定,如下表所示。

当确定D和M的范围后就需要确定其最佳值了。首先确定M的值,这是基于VCO目标频率考虑的,即VCO的理想工作频率。确定方法就是使D和M尽可能的小,同时使ƒVCO尽可能高。

相位的确定逻辑,输出时钟的相位范围是-360度到360度。

输出时钟相位是可配置的。其内部的实现方案是与VCO有关。CMT内部可以提供8个相移时钟,每个相移45°。始终为0°,45°,90°,135°,180°,225°,270°和315°的相移提供可能的设置。VCO频率越高,相移分辨率越小。所以输出时钟的相位刻度等于45/CLKOUT_DIVIDE。当CLKOUT_DIVIDE小于64时,最大相移是360度,当大于64时最大相移为如下公式所得,也就是相位是由两部分决定的,但在实际编程时我们只需要填写相位就可以了。

![]()

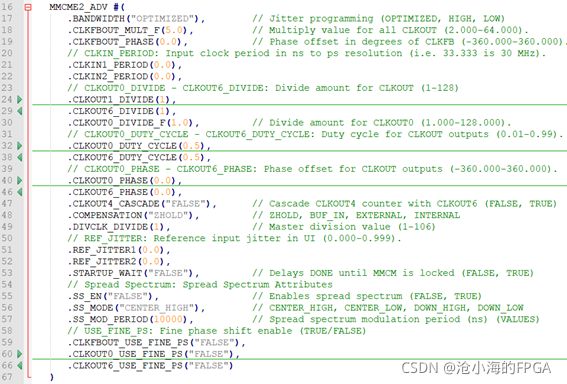

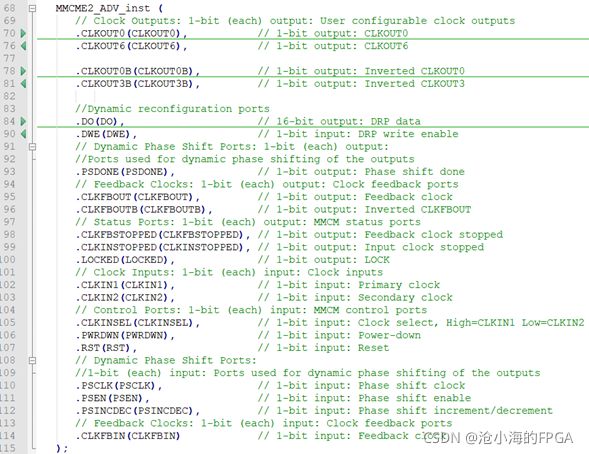

如下是MMCM的原语,其中隐藏内容与上下行一致,下面就对这些信号进行阐述。

1、BANDWIDTH

指定影响抖动、相位裕度和MMCM其他特性,有“HIGH”、“LOW”和“OPTIMIZED”三个选项,默认OPTIMIZED

即可

2、CLKFBOUT_MULT_F

即上述的M,整数的范围是2到64,小数的最小刻度是0.125。

3、CLKFBOUT_PHASE

指定时钟反馈输出的相位偏移(以度为单位)。对反馈时钟进行移位会导致到MMCM的所有输出时钟的负相移。范围是0到360,默认是0。

4、CLKIN1/2_PERIOD

输入时钟的周期,以ns为单位,最小刻度到ps。允许范围是0.938到100ns。

5、CLKOUT[1:6]_DIVIDE和CLKOUT[0]_DIVIDE_F

确定输出频率的,也就是对VCO的分频值,范围是1到128,其中CLKOUT0可以精确到0.125,CLKOUT1到6是整数。

6、CLKOUT[0:6]_DUTY_CYCLE

以百分比的形式关联输出时钟占空比,范围是0.01到0.99

7、CLKOUT [0:6]_PHASE

输出相位,范围是-360到360,具体多少输入度数即可,但实际不一定是对应度数。

8、CLKOUT4_CASCADE

布尔值,将输出分频器(计数器)CLKOUT6级联到CLKOUT4分频器的输入中,以得到大于128的输出时钟分频器,有效地提供了16384的总分频值。

9、COMPENSATION

时钟输入补偿。 必须设置为ZHOLD。 定义MMCM反馈的配置方式。

ZHOLD:表示MMCM配置为在I / O寄存器中提供负的保持时间。

EXTERNAL:表示正在对FPGA外部的网络进行补偿。

INTERNAL:表示MMCM正在使用其自己的内部反馈路径,因此不会补偿任何延迟。

BUF_IN:表示该配置与其他补偿模式不匹配,并且不会补偿任何延迟。 如果时钟输入由BUFG / BUFH / BUFR或GTX / GTH / GTP驱动,则是这种情况。

10、SS_*

扩频相关的

11、*_USE_FINE_PS

对应的精细相移使能

1、CLKOUT[0:6]

这些用户可配置的时钟输出(对于MMCM为CLKOUT0至CLKOUT6,对于PLL为CLKOUT0至CLKOUT5)可以将VCO相位输出(用户可控)从1(旁路)到128分频。输入时钟和输出时钟可以为 相位对齐。

当与BUFR或BUFIO一起使用时,只有MMCM可以从时钟输出CLKOUT0至CLKOUT3直接连接到HPC。 此外,CLKOUT0至CLKOUT3可以连接到CMT主干,以级联MMCM和PLL。 类似于将MMCM和PLL从CCIO引脚驱动到相邻区域(请参见具有时钟的输入),级联使用CMT主干中可用的一些有限资源来直接在相邻区域中连接时钟资源。 同一列内级联元素之间也会产生相位偏移。

有关可能的配置,请参见MMCM和PLL使用模型。 在MMCM中,CLKOUT0和CLKFBOUT可以在小数分频模式下使用。 所有CLKOUT输出均可在非小数模式下使用,以提供静态或动态相移。 在小数模式下,仅允许固定相移。 有关更多信息,请参见静态相移模式。

2、CLKOUTB[0:3]

CLKOUT [0:3]的反相(180°相移)。 在PLL中不可用。

3、动态配置端口,暂不描述

4、PSDONE

完成相移的输出信号与PSCLK同步。 当前的相移操作完成后,将在一个时钟周期内声明PSDONE信号,以指示可以启动一个新的相移周期。 在PLL中不可用。

5、CLKFBOUT

提供反馈时钟的。

6、CLKFBOUTB

没啥用

7、CLKFBSTOPPED

状态引脚,指示反馈时钟已停止。 该信号在时钟停止的一个时钟周期内有效。 反馈时钟重新启动并且MMCM重新锁定后,信号将置为无效。 在PLL中不可用。

8、CLKINSTOPPED

状态引脚,指示输入时钟已停止。 该信号在时钟停止的一个时钟周期内有效。 时钟重新启动并达到LOCKED(锁定)或时钟切换到备用时钟输入且MMCM重新锁定后,信号将置为无效。 在PLL中不可用。

9、LOCKED

MMCM / PLL的输出,用于指示MMCM / PLL在输入引脚上何时实现了参考时钟和反馈时钟的相位和频率对准。 相位对齐在预定义的窗口内,频率匹配在预定义的PPM范围内。 MMCM上电后自动锁定,不需要额外的复位。 如果输入时钟停止,违反相位对齐(例如,输入时钟相移)或频率已更改,则在一个PFD时钟周期内将LOCKED置为无效。 解除锁定时必须复位MMCM / PLL。 在声明LOCKED之前,不应使用时钟输出。

10、CLKIN1/2

CLKIN1是主要参考时钟输入,可以由SRCC或MRCC I / O直接在同一时钟区域内驱动,SRCC或MRCC I / O可以通过垂直相邻时钟区域内的CMT主干,BUFG,BUFR,BUFH,互连(不推荐)来驱动,或直接通过 高速串行收发器。 当时钟输入来自用于级联CMT功能的另一个CMT模块时,只能使用CLKOUT [0:3]。

CLKIN2是辅助时钟输入,用于动态切换MMCM / PLL参考时钟。CLKIN2可以由SRCC或MRCC I / O直接在同一时钟区域内驱动,SRCC或MRCC I / O通过CMT主干在垂直相邻的时钟区域内进行驱动,BUFG,BUFR,BUFH,互连(不推荐),或直接通过 高速串行收发器。

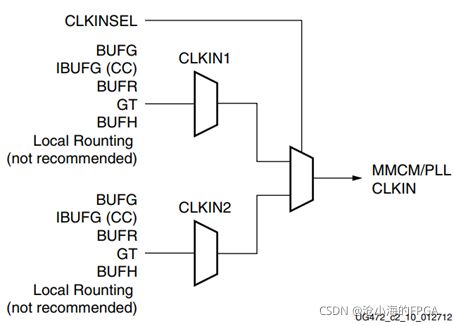

11、CLKINSEL

CLKINSEL信号控制时钟输入MUX的状态,高= CLKIN1,低= CLKIN2。 时钟切换期间,MMCM / PLL必须保持在RESET状态。MMCM和PLL参考时钟可以通过使用CLKINSEL引脚动态切换。 切换是异步完成的。 时钟切换后,MMCM / PLL可能会丢失“锁定”并自动锁定到新时钟上。 因此,一旦时钟切换,则必须复位MMCM / PLL。 MMCM / PLL时钟MUX切换如图3-10所示。 CLKINSEL信号直接控制MUX。 不存在同步逻辑。

12、PWRDWN

关闭已实例化但当前未使用的MMCM / PLL。 此模式可用于为设计中暂时不活动的部分和/或在某些系统配置中不活动的MMCM / PLL节省功率。 在此模式下不消耗MMCM / PLL功耗

13、RST

RST信号是MMCM / PLL的异步复位。 当该信号无效时,MMCM / PLL将被同步重新启用。

14、PS*

这三个信号是动态相移接口,暂不阐述

15、CLKFBIN

必须直接连接到CLKFBOUT以获得内部反馈或IBUFG(通过具有时钟偏移功能的外部去歪斜引脚),BUFG,BUFH或互连(不推荐)。 对于外部时钟对齐,除了BUFR以外,反馈路径时钟缓冲器类型应与正向时钟缓冲器类型相匹配。BUFR无法补偿

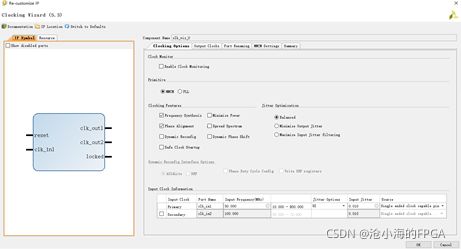

第六章 Clocking Wizard的几点介绍

Clocking Wizard就是用来产生不同频率、相位甚至占空比的IP核。该核对每一个FPGA开发中可以说是再熟悉不过了,故本文仅对该核在配置过程中的选项卡内容进行简单的阐述。

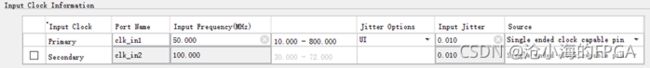

第一部分 :Clocking option

这部分是用来配置时钟网络功能和输入时钟的。

1、Enable Clock Monitoring

Monitoring具有检测的意思,使能该选项就是可以最多监视4个时钟,监视输入频率是否超出渔区频率范围,检测时钟是否停止是否存在毛刺。

2、Primitive

这是选择调用的硬核资源是MMCM还是PLL,一个CMT上既有MMCM也有PLL,PLL是MMCM的一个子集,在绝大多数情况下,如果需要两个锁相环,我们可以调用一个MMCM一个PLL,这样保证时钟来自同一个BANK。

3、Clocking Feature

我们可以看到有7个时钟功能选项,这些其实就是与原语的一个封装调用。

Frequency synthesis:

这是必选项,如果不选就无法产生于输入时钟不同频率的时钟了。

Phase alignment:

此功能允许将输出时钟锁相至参考时钟,实现相位对齐。

Dynamic reconfiguration:

动态重配置,也就是调用硬核的重配置功能,对外接口可以是AXI4-Lite也可以是DRP接口。

安全时钟启动和排序

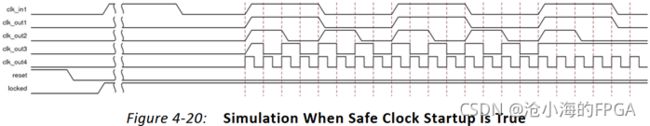

Safe Clock Startup:

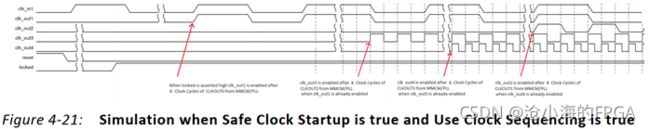

此功能对于在输出端获得稳定有效的时钟很有用。安全时钟启动功能可在8个输入时钟被采样为“高”后,使用BUFGCE在输出上提供稳定有效的时钟。排序功能可根据通过GUI输入的数字按顺序启用时钟。 顺序使能的两个输出时钟之间的延迟是顺序时钟中第二个时钟的8个周期。此功能对于需要模块一个接一个地运行的系统很有用。

Minimize power:

该功能以可能的频率,相位偏移或占空比精度为代价,将芯片所需的功率最小化。选择“扩频”功能后,此功能不可用

Spread Spectrum (SS)

此功能提供调制的输出时钟,可降低电子设备产生的电磁干扰(EMI)的频谱密度。 此功能仅适用于MMCM(E2 / E3)原语。当扩频为TRUE时,Minimize power和Dynamic reconfiguration功能不可用。

Phase alignment

此功能允许将输出时钟锁相至参考,例如设备的输入时钟引脚

3、Jirtter Optimization

Balanced:

选择“平衡”会导致软件选择正确的带宽来优化抖动。

Minimize output jitter

此功能可最大程度地减少输出时钟上的抖动,但会降低功耗,并可能会产生输出时钟相位误差。 此功能不适用于“最大化输入抖动过滤”。

Maximize input jitter filtering

此功能允许输入时钟上更大的输入抖动,但会对输出时钟上的抖动产生负面影响。 此功能不适用于“最小化输出抖动”。