计算机组成原理---第四章 存储器(下)

高速缓冲存储器

我所做的一切最终都是为了自己,但是没有你,我根本不会去做那些事情

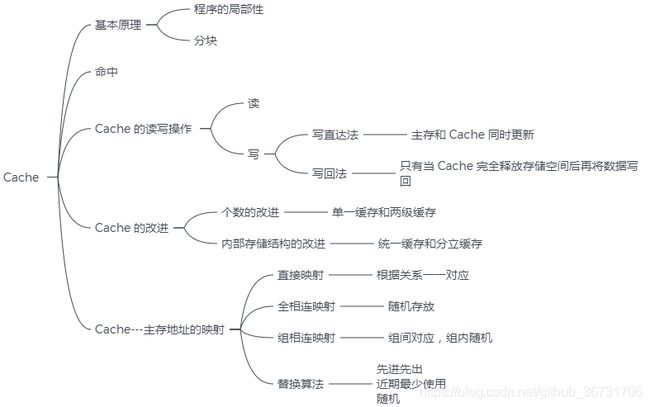

笔记框架:

-

4.3.1 高速缓冲存储器

- 1.Cache 产生的原因

- 2.Cache 的工作原理

- 3.Cache 的基本结构

- 4.Cache 的读写操作

- 5.Cache 的改进

-

4.3.2 Cache —主存地址映射

-

4.3.3 替换算法

-

4.4 辅助存储器

-

总结

4.3 高速缓冲存储器

4.3.1概述

1.Cache 产生的原因

程序访问的局部性:指令和数据在主存的地址分布不是随机的,是相对的簇聚。

CPU 将近期用到的程序和数据提前从主存送进 Cache

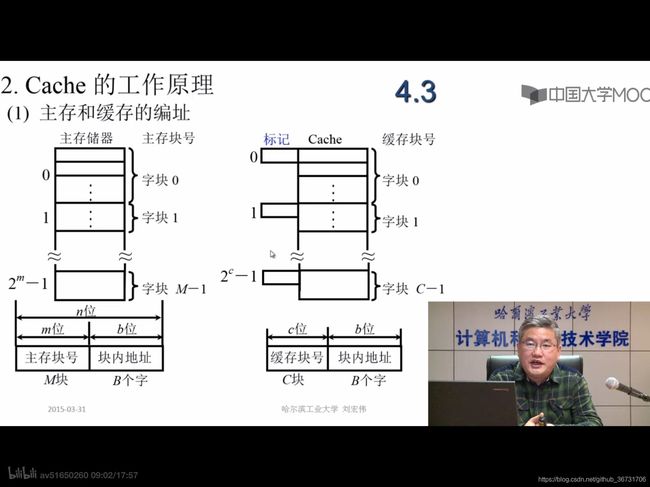

2.Cache 的工作原理

将主存可缓存处进行分块,块的大小相同。

主存地址:主存块号+块内地址;缓冲区地址:块号+块内地址。其中在标记处记录此块在内存中的地址。

主存和缓存按块存储,块的大小相同

(2)命中不命中

Cache 的容量有限,只能将主存的部分块存放在 Cache 中。

命中:主存的块在 Cache 中,与主存建立了对应关系

不命中:主存的块不在 Cache 中,没有与主存建立关系

(3)Cache 的命中率

命中率:CPU 欲访问信息在 Cache 中的命中率

命中率与Cache 的容量和块长有关

块长取一个存储周期内从主存调出的信息长度

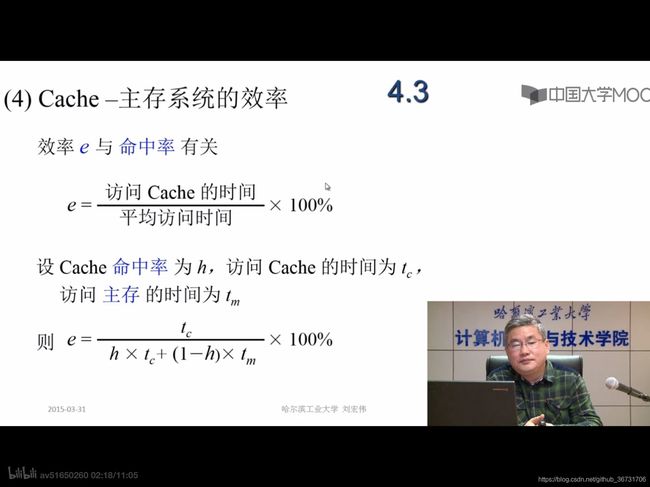

(4)Cache 主存系统的效率

ta =访问Cache 的概率 + 访问内存的概率。 (分母处的那一段长式子就是 ta)

这里的分母可以看出,CPU 在调用一个数据的时候 对于 Cache 和内存的访问是同时的。如果不是同时的分母上就不会乘命中率再相加(相当于看为了一个整体 t),而是两个总时间的相加

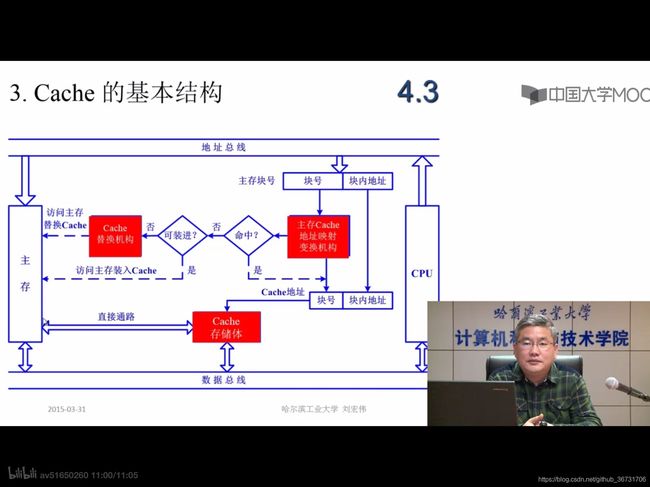

3.Cache 的基本结构

4.Cache 的读写操作

(1)读

读操作没有对 Cache 和 内存的信息修改

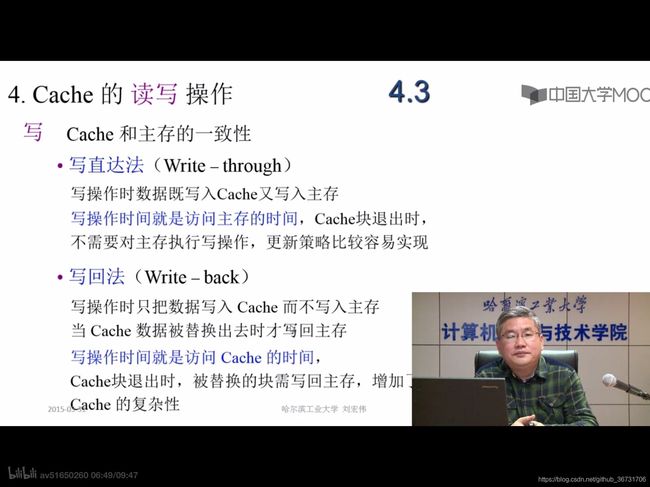

(2)写

Cache 和主存内容的一致性进行分类

a. 写直达法

写操作要同时改变两个存储介质的内容

优点:时刻保持 Cache 内容与主存内容一致

缺点:如果频繁的对数据进行变动就要则 Cache 与 主存的交互也会变频繁

b.写回法

允许一段时间内 Cache 内容与主存内容不一致

优点:减少了 Cache 和 主存的频繁交互

缺点:有时会有多个 CPU ,当不同 CPU 调用同一块主存放入 Cache 的时候会导致数据更新不一致

5.Cache 的改进

(1)单一缓存和两级缓存

改进的为缓存的个数和位置

单一缓存:在CPU 与主存之间只设置一个缓存,后期直接将这个缓存放在 CPU 内部,又称片内缓存(片载缓存)

两级缓存:由于片内缓存的大小十分有限,所以在主存和片内缓存之间又增加了一级缓存成为片外缓存

(2)统一缓存和分立缓存

改变的为 Cache 内部存储的数据和指令的方式

统一缓存:将数据和指令都放在同一个 Cache 中

分立缓存:指令和数据分别放在两个缓存中。如奔腾的 Cache 8K 用于存放指令,8K用于存放数据

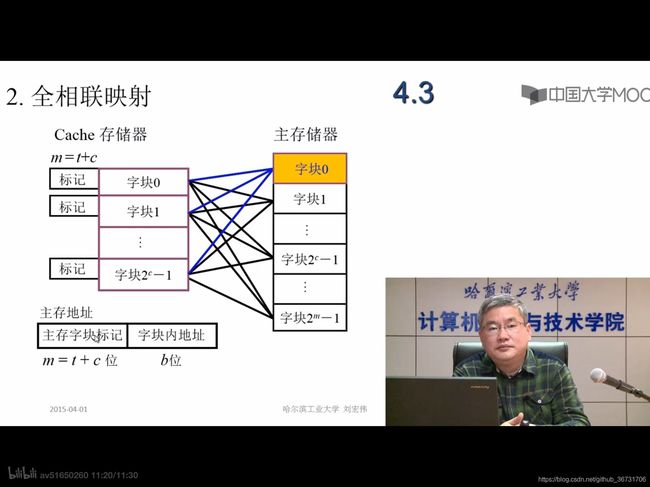

4.3.2 Cache ---主存地址映射

Cache —主存地址映射:主存地址映射到 Cache 地址。主要映射方式有三种:直接映射,全相连映射,组相连映射

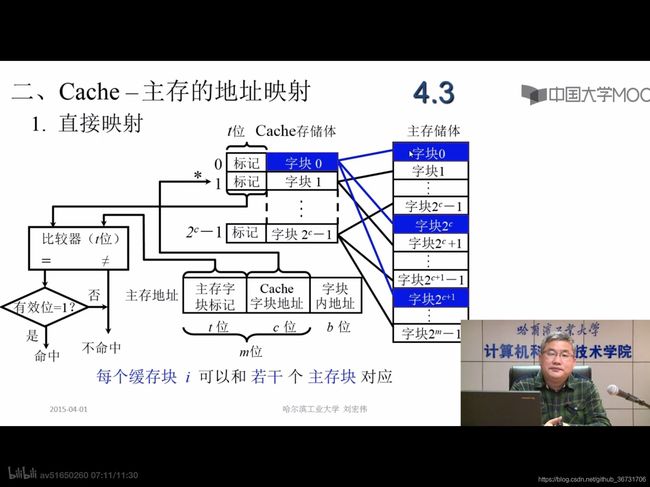

1.直接映射

按照一定的映射关系(类似于函数关系),主存中的存储单元在Cache 中的存储地址固定

优点:在 Cache 中寻找速度快

缺点:1.每个主存块只能放到固定的位置,导致 Cache 中大量的位置空闲

2.如果程序恰好需要不断需要访问同一缓存位置的不同主存块,就要不停地切换

2.全相联映射

主存中的任意一块可以放在 Cache 中的任意位置,只要 Cache 中还有空闲位置。

优点:解决了直接映射的空间浪费问题

缺点:CPU 根据标记中的主存地址寻找想要的数据在 Cache 中的位置,要一个个的进行比较看是否符合,大大增加了寻找时间

3.组相连映射

直接相联+全相联

原理: 将内存分为多个区,按照区的大小将Cache 分为多个组。不同区(主存中)的块根据映射放入 Cache 对应的组内(直接相连),选定放入的组后再将相应的块随机放入组内的空闲区域(全相连)

组内随机,组间有序

特殊情况:

Cache 只分为 1组------全相连

Cache 每组只能放一个------直接相连

根据特性 :有时将频繁调用的数据以直接相连的方式放在靠近 CPU 的 Cache 层次,中间层次用组相连,离 CPU 最远的层次用全相连

4.3.3 替换算法

替换算法: 当新的主存块需要调入 Cache 并且它的可用空间又被占满时,需要替换掉 Cache 中的数据,替换算法决定了要将哪个数据进行替换

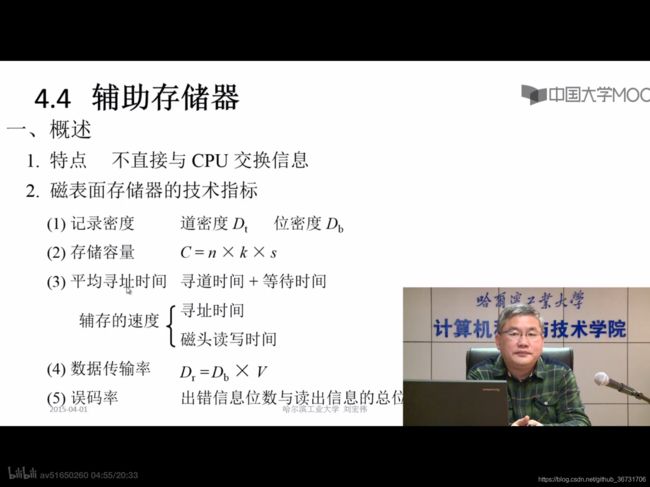

4.4 辅助存储器

(非重点)4.4.1概述

1.辅助存储器特点 辅助存储器不可以直接和 CPU 进行交换,要先将辅助存储器的数据传送到内存2.磁表面存储器的技术指标

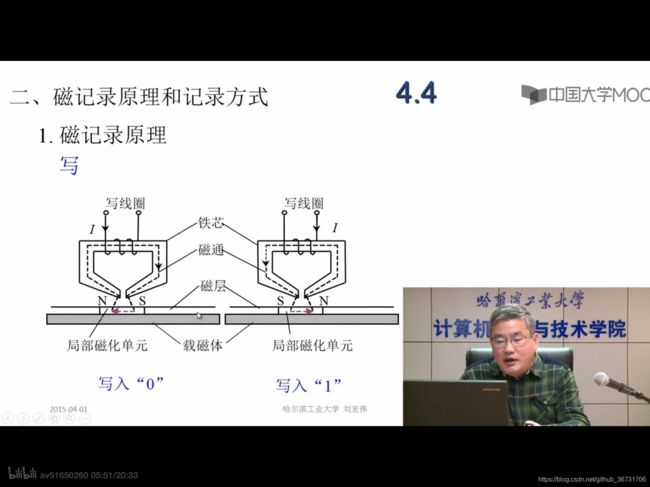

4.4.2磁记录原理

写线圈同上不同的磁极将载磁体进行磁化,不同的磁极可看为 0,1

读取的时候通过磁载体上面的磁进行磁感线的切割,读线圈就可以读出相应的极,代表 0,1

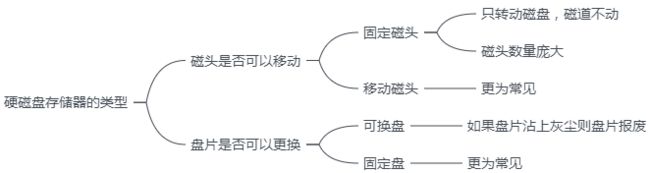

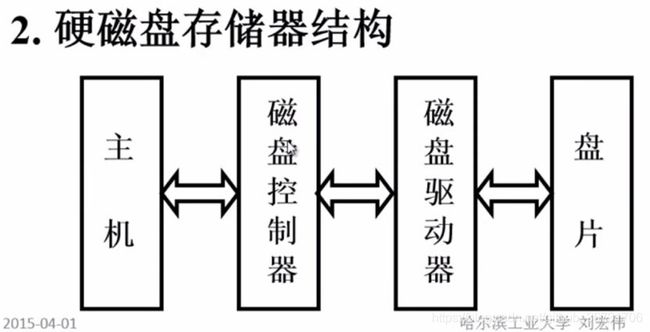

4.4.3 硬磁盘存储结构

1.硬磁盘存储器类型

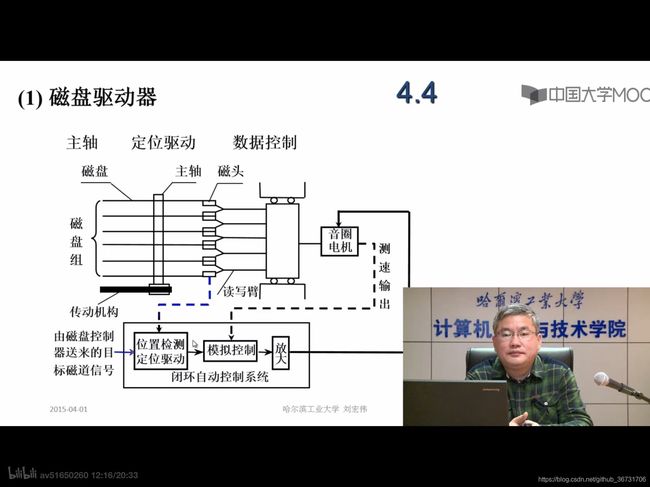

磁盘驱动器接收磁盘控制器传来的信号进行转换控制音圈电机的移动从而带动磁头移动,最终将数据写入磁盘组

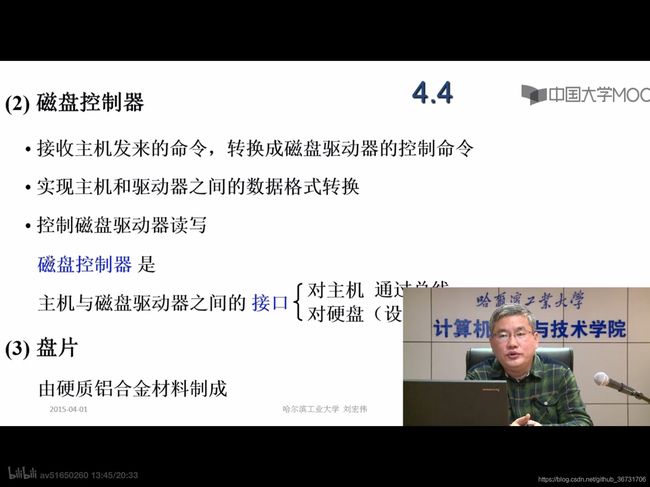

(2)磁盘控制器

磁盘控制器是主机与磁盘之间交换数据的一个接口

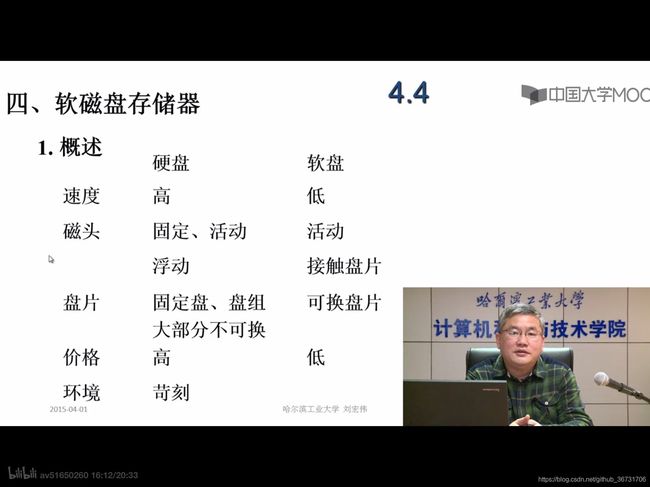

4.4.4软磁盘存储器

进行一个大体的了解即可,现在市场上已经几乎看不到软盘了

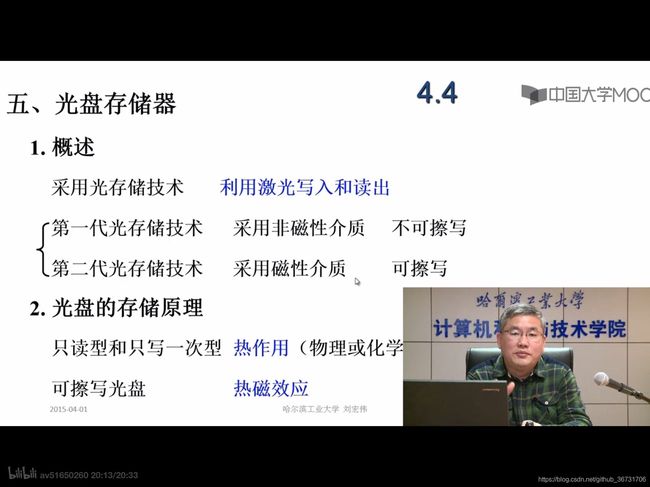

4.4.7 光盘存储器

总结

硬件主要是了解了 : 硬盘,软盘,光盘

由于不是很重要就不展开了