DDR3基础详解

最近在IMX6平台下做DDR3的测试接口开发,以前在学习嵌入式时,用的是官方源码,没有做过多的研究。此时需要仔细研究DDR3的引脚与时序,此篇是我在学习DDR3做的归纳与总结,其中有大部分内容是借鉴他人的 博客,大部分博客的链接我已经贴出来了,如果存在版权或知识错误请直接联系我。

PS:本着知识共享的原则,此篇博客可以随意转载,不过请标明出处(虽然大部分内容不是我写的,但是整理也挺累的 _ !)

一、专有名词索引表

优化分类中ing…

| 名称缩写 | 名称含义 | 名称描述 |

|---|---|---|

| RAS | 行地址选通脉冲 | Row Address Strobe |

| CAS | 列地址选通脉冲 | Column Address Strobe |

| RCD | 行选通到读写命令的延时 | (RAS to CAS Delay)决定了行寻址和读写命令的间隔 |

| CL | 读命令到数据真正输出的时延 | (CAS latency) 内存读写操作前列地址控制器的潜伏时间 |

| BL | 突发长度 | (Burst Length) |

| DLL | 延迟锁定回路 | |

| tRAS | 行激活时间 | 是存储区激活命令与发出预充电命令之间所花费的时钟周期数 |

| tRCD | 行地址到列地址的延迟 | (RAS-to-CAS Delay) 发出活动命令和读取写入命令之间花费的时钟周期数 |

| tRC | 行循环时间 | (Row Cycle Time)同一个Bank之间激活命令的时间间隔 tRC=tRAS+ tRP |

| tRRD | 行单元到行单元的延时 | (Row to Row Delay)不同Bank之间的激活命令时间间隔被称为tRRD |

| tCPC | 首命令延迟 | (Command Per Clock) 在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令 |

| ACTIVE | 激活命令 | 激活指定Bank和行,在READ和WRITE命令前 |

| PRECHARGE | 预充电 | 读写完成后,对同一Bank中另一行操作前,需要关闭现在的工作行,才能打开新一行 |

| REFRESH | 刷新 | 长时间没有对电容充电会导致数据丢失,定期刷新,对数据进行重写,保证数据不丢失 |

| tRP | 行预充电时间 | 发出预充电命令和活动命令之间花费的时钟周期数 |

| tRPA | 所有BanK的预充电命令发出需要的时间 | |

| tRAS | 内存行有效至预充电的最短周期 | t(RAS Active Time) |

| tRFC | 刷新时间间隔 | |

| DQS/TDQS | 数据选取脉冲 | 用于数据同步 |

| tDQSCK | 差分时钟的交叉点到数据选通脉冲的交叉点的时间 | |

| tQSH | DQS的差分输出高电平时间 | |

| tQSL | DQS的差分输出低电平时间 | |

| tDQSQ | 最近数据选通脉冲到数据有效的时间 | |

| tRPRE | DQS读操作前同步 | |

| tRPST | DQS读操作后同步 | |

| DQS Skew Control | DQS时间差控制 | |

| tAL | 附加延时 | RAS后,可以立即CAS读命令。但是需要保持AL个周期,可以提高总线的效率 |

| tCCD | 读命令之间的时间间隔 | CAS#-to-CAS#命令之间的时延 |

| tRL | 读取延迟 | 从列地址发出到数据端口上有效的数据输出延时 RL = AL + CL |

| tAC | 表示命令被重新传输后通过S-AMP放大传输到/O脚的时间 | |

| tWL | 总的写潜伏 | (Write Latency) tWL= tAL+ tCAS; |

| tCWL / tWCL | 列写潜伏期 | (CAS Write Latency)内部写命令和第一个bit有效数据输入之间的时钟周期延时, |

| tDQSS | 写入延迟 | 写入数据与DQS 相对于写入命令的延迟时间 |

| tWR | 写恢复时间 | 写数据和发出预充电命令之间所需时钟周期,写突发之后一定要跟随一个预充电命令 |

| Write Leveling | 写入均衡(写调平) | (Write Leveling)调整DQS差分对和CK差分对的相对位置,利用DQS差分对路径上的可调整延时来达成该目的,调整DQS信号和CLK信号边沿对齐。 |

| tWPST | 写后同步周期 | |

| tWTR | 写到读命令的延时 | 当写命令之后跟随 读命令时的延时 |

| tFAW | (Four Active Window)同一rank中允许同时发送大于四个行激活命令的间隔时间 tFAW ≥ 4*tRRD |

|

| tRTP | ||

| tDLLK | ||

| tMRD | 模式寄存器的设置命令周期(两次操作的最小时间) | |

| 10.0刷新 | 注意:无需外部提供刷新指令 | |

| ASR | 自动自刷新 | |

| AR/CBR | 自动刷新 | Auto Refresh/CAS Before RAS |

| SR | 自刷新 | Self Refresh |

| PASR | 局部自刷新 | |

| tREF | 刷新周期 | (Refresh Period)内存模块的刷新周期 |

| tRFC | 两次刷新时间间隔 | (Row Refresh Cycle Time) |

| tQH | 数据选通脉冲到最早的无效数据无法正确判断数据是否为1的时间 | |

| tIS | 命令建立时间 | tis(total setup time)=tis(base)+ ∆tis |

| tIH | 命令保持时间 | tih(total setup time)=tih(base)+ ∆tih |

| tDS | 数据建立时间 | tDS(total setup time)=tDS(base)+ ∆tDS |

| tDH | 数据保持时间 | tDH(total hold time)=tDH(base)+ ∆tDH |

| OCD | 离线驱动调整 | Off-Chip Driver 通过OCD减少DQ-DQS的倾斜来提高信号完整性 |

| RTT | ODT的有效阻抗 | 在DDR3 标准中定义了两种RTT,即RTT_nom 和RTT_wr,两者分别在MR1和MR2寄存器中设定 |

| RTT_nom | 在写调平(write leveling)模式下,仅RTT_nom可用。 | |

| RTT_wr | 在写模式下,可以使能RTT_wr来动态改变ODT而不需要重新设置MR寄存器。 | |

| 参考电压: | ||

| VDDQ | DQ供电电压 | VDDQ是DQ的供电电压 |

| VTT | RTT的参考电压 | VTT = VDDQ / 2; |

注意:Delay(延迟)和Latency(潜伏)本质是不同的:

1.Delay:事情要在这个时间之后开始。

2.Latency:事情已经发生,但是还不够稳定需要一个稳定时间。

二、DDR 引脚说明

为了帮助我们认识,而且不同的功能引脚有不同的要求,DDR3物理引脚可划分为4类:地址总线、数据总线、控制线、电源与参考电压。

1.数据线

1)DQ[13:0] 数据总线:

2)DQS,DQS# 数据选通:

用于数据同步,读时是输出,边缘与读出的数据对齐。写时是输入,中心与写数据对齐。3)TDQS,TDQS# 数据选通:

功能与DQS相同,只是当两种不同的DIMM混合应用在同一个系统时,DQS的负载就会不同,这样会造成信号完整性问题,TDQS就是为了解决这个问题的。当TDQS使能时,DM禁止,TDQS和TDDS提供终端电阻。注意:TDQS与DM共用一个物理引脚。4)DM 数据屏蔽:

DM是写数据的输入屏蔽信号,在写期间,当伴随输入数据的DM信号被采样为高时,输入数据被屏蔽。最然DM仅作为输入脚,但是,DM负载被设计成与DQ和DQS脚负载相匹配。DM的参考值是 VREFCA引脚。注意: DQS与DM共用一个物理引脚,所以DM可选作为TDQS。

2.地址线

1)A[14:0] 地址总线:

为地址输入,为 ACTIVATE命令提供行地址,同时为READ/WRTE命令提供列地址和自动预充电位(A10),以便从某个Bank的内存阵列里选出一个位置。LOAD MODE命令期间,地址输入提供一个操作码。地址输入的参考值是 VREFCA引脚。

A12/BC#: 在模式寄存器(MR)使能时,A12在READ和 WRITE命令期间被采样,以决定burst chop(on-the-fly)是否会被执行(HIGH=BL8执行 burst chop),或者LoW-BC4不执行 burst chop。2)BA[2:0] bank选通线: 确定要操作的Bank,参考值是ⅤREFCA引脚。

3.命令&控制&时钟

- 1)CKE 时钟使能引脚(输入):

CKE为高电平时,启动内部时钟信号、设备输入缓冲以及输出驱动单元。CKE低电平时则关闭上述单元。当CKE为低电平时,可使设备进入PRECHARGE POWER DOWN、SELF-REFRESH以及ACTIVE POWER DOWN模式。CKE与SELF REFRESH退出命令是同步的。在上电以及初始化序列过程中,VREFCA与VREF将变得稳定,并且在后续所有的操作过程中都要保持稳定,包括SELF REFRESH过程中。CKE必须在读写操作中保持稳定的高电平。在POWER DOWN过程中,除CK_t,CK_c,ODT以及CKE以外的所有输入缓冲都是关闭的。在SELF REFRESH过程中,除CKE以外的所有输入缓冲都是关闭的。在正时钟上升边沿采样。- 2)CK. CK# 差分时钟信号(输入):

差分时上钟输入,所有控制和地址输入信号在CK上升沿和CK#的下降沿交叉处被采样,输出数据选通(DQs,DQS#)参考与CK和CK#的交叉点。- 3)CS# 片选信号:

使能(低)和禁止(高)命令译码,当CS#为低时DDR芯片使能、CS#的参考值是 VREFCA引脚。- 4) RAS#,CAS#,WE#:这3个信号,连同CS#,定义一个命令,其参考值是ⅤREFCA。

- 6)RESET# 复位信号: 低位有效,参考值是VSS,复位的断言是异步的

- 7)ODT 片上终端使能:

ODT使能(高)和禁止(低)片内终端电阻,在常操作使能时,ODT仅对下面的引脚有效:DQ[7:0]、DQS、DQS#和DM。如果通过LOADMODE命令禁止,ODT输入被忽略。ODT的参考值是VREFCA引脚。- 8)ZQ#: 输出驱动校准的外部参考,这个引脚应该连接240欧姆电阻到VSSQ。

4.电源与参考引脚

1)VDD: 电源电压,1.5V±0,075V。

2)VEDO: DQ电源,1.5V±0.075V。为了降低噪声,在芯片上进行了隔离。

3)VREFCA: 控制、命令、地址的参考电压。 VREFCA在所有时刻(包括自刷新)都必须保持规定的电压。

4)VREFDQ: 数据的参考电压。 VREFDQ在所有时刻(除了自刷新)都必须保持规定的电压。

5)VSS: 地.

6)VSSQ: DQ地, 为了降低噪声,在芯片上进行了隔离

5.引脚功能

1)ODT ( On-DieTermination ,片内终结)

所谓的终结(端接),就是让信号被电路的终端吸收掉,而不会在电路上形成反射, 造成对后面信号的影响。 顾名思义, ODT 就是将端接电阻移植到了芯片内部,主板上不再有端接电路。在进入DDR 时代, DDR 内存对工作环境提出更高的要求,如果先前发出的信号不能被电路终端完全吸收掉而在电路上形成反射现象, 就会对后面信号的影响造成运算出错。因此目前支持DDR主板都是通过采用终结电阻来解决这个问题。 由于每根数据线至少需要一个终结电阻, 这意味着每块DDR 主板需要大量的终结电阻, 这也无形中增加了主板的生产成本 ,而且由于不同的内存模组对终结电阻的要求不可能完全一样,也造成了所谓的“内存兼容性问题”。而在DDR-II 中加入了 ODT功能,当在DRAM 模组工作时把终结电阻器关掉, 而对于不工作的 DRAM 模组则进行终结操作,起到减少信号反射的作用,如下图二所示。ODT 的功能与禁止由主控芯片控制,在开机进行 EMRS 时进行设置, ODT 所终结的信号包括 DQS 、DQS# 、DQ 、DM 等。这样可以产生更干净的信号品质,从而产生更高的内存时钟频率速度。而将终结电阻设计在内存芯片之上还可以简化主板的设计,降低了主板的成本, 而且终结电阻器可以和内存颗粒的“特性”相符, 从而减少内存与主板的兼容问题的出现.ODT将终结电阻移植到了芯片内部,主板上不在有终结电路。ODT的功能与禁止由北桥芯片控制,主要用来简化一个模组中同时使用4与8bit位宽芯片时的控制设计)、DQ、DM等。

2)ZQ 校准

如下所示, ZQ 是DDR3一个新增的引脚,在这个引脚上接有一个 240 欧姆的低公差参考电阻。这个引脚通过一个命令集,通过片上校准引擎( ODCE ,On-DieCalibrationEngine )来自动校验数据输出驱动器导通电阻与 ODT 的终结电阻值。 当系统发出这一指令之后, 将用相应的时钟周期 (在加电与初始化之后用 512 个时钟周期,在退出自刷新操作后用 256 时钟周期、在

其他情况下用 64个时钟周期)对导通电阻和 ODT 电阻进行重新校准。

ODT是终端匹配,那就是要在你的信号线终端上拉一个电阻,但是这个内部电阻随着温度会有些细微的变化,为了保证信号被准确的进行终端匹配,就需要ZQ了,ZQ的作用就是使用你外面连接的,高精度240R电阻来对这个内部的电阻进行校准。

4)外驱动调校 OCD ( Off-ChipDriver )

OCD 是在 DDR-II 开始加入的新功能,而且这个功能是可选的,有的资料上面又叫离线驱动

调整。 OCD的主要作用在于调整 I/O 接口端的电压,来补偿上拉与下拉电阻值, 从而调整

DQS 与 DQ 之间的同步确保信号的完整与可靠性。 调校期间,分别测试 DQS 高电平和 DQ

高电平,以及 DQS 低电平和 DQ 高电平的同步情况。 如果不满足要求,则通过设定突发长

度的地址线来传送上拉 / 下拉电阻等级(加一档或减一档),直到测试合格才退出 OCD 操作,

通过 OCD 操作来减少 DQ 、 DQS的倾斜从而提高信号的完整性及控制电压来提高信号品质。

具体调校如下所示。

不过,由于在一般情况下对应用环境稳定程度要求并不太高,只要存在差分 DQS时就基本可以

保证同步的准确性, 而且 OCD 的调整对其他操作也有一定影响, 因此 OCD 功能在普通台式/

机上并没有什么作用,其优点主要体现在对数据完整性非常敏感的服务器等高端产品领域。

5) 参考电压:VREFCA & VREFDQ

对于内存系统工作非常重要的参考电压信号VREF,在DDR3系统中将VREF分为两个信号.

一个是为命令与地址信号服务的VREFCA,另一个是为数据总线服务的VREFDQ,

它将有效的提高系统数据总线的信噪等级,如下图所示。

6) 重置(Reset: 低功耗)

重置是DDR3新增的一项重要功能,并为此专门准备了一个引脚。这一引脚将使DDR3的初始化处理变得简单。

当Reset命令有效时,DDR3 内存将停止所有的操作,并切换至最少量活动的状态,以节约电力。在Reset期间,

DDR3内存将关闭内在的大部分功能,所有数据接收与发送器都将关闭,且所有内部的程序装置将复位,DLL(延迟锁相环路)

与时钟电路将停止工作,甚至不理睬数据总线上的任何动静。这样一来,该功能将使DDR3达到最节省电力的目的,新增的引脚如下图所示。

7)数据掩码 Data Mask(DM)

数据掩码功能也称为部分写。只支持x8和x16配置。DM功能与DBI和TDQS功能共用相同的管脚。DM功能只用于写操作,且不能与写DBI功能同时使能。

TDQS功能的优先级最高,如果使能了TDQS那么DM和DBI功能都被禁止。

8)终端数据选通Termination Data Strobe (DQS/TDQS)

对于x8的DIMMs,每一个8位字节需要一个DQ选通道对(DQS/DQS#);对于x4的DIMMs,第半个字节需要一对DQ选通对(DQS/DQS#)。当这两种不同的DIMM混合应用在同一个系统时,DQS的负载就会不同,这样会造成信号完整性问题。TDQS就是为了解决这个问题的。TDQS只用于x8 DRAM,不过TDQS还会和DM共同用用DM功能。

RDIMM0是x4 DRAM, RDIMM1是x8 DRAM, 由x4组成的RDIMM需要两个DQ选通对,其中一对连接到x8的RDIMM1上实现同样的功能,另一个选通对对于RDIMM1是没有用处的,但是连接到了TDSQ对上,当使能TDQS后,可以保证所有的选通脚负载一样。这样保证了信号的完整性。RDIMM0是x4 DRAM, RDIMM1是x8 DRAM, 由x4组成的RDIMM需要两个DQ选通对,其中一对连接到x8的RDIMM1上实现同样的功能,另一个选通对对于RDIMM1是没有用处的,但是连接到了TDSQ对上,当使能TDQS后,可以保证所有的选通脚负载一样。这样保证了信号的完整性。

DQS是内存和内存控制器之间信号同步用的。

由DQ信号发出端发出DQS,信号接收端根据DQS的上、下沿来触发数据的接收。

简单点说,如果是从内存中读取信号,那么主板北桥(内存控制器)根据内存发出的DQS来判断在什么时候接收读出来的数据。如果是写的话,就正好相反,内存根据北桥发出的DQS来触发数据的接收。

DDR2每芯片有一个读、写双向的DQS,DDR3是有读和写两个DQS(2个DQS的好处是,不必等待DQS反向)。

2、DDR的内核时钟只有100M 133M 166M 200M四种,由于几代预读取能力不同,那DDR3举例,它的等效频率就成了800M —1600M这个应该是它的范围吧?

是的。内核时钟预读取位数2=等效时钟频率。

9) ZQ 校准

关于ZQ校正有两个命令ZQCL (ZQ CALIBRATION LONG )和ZQ CALIBRATION SHORT (ZQCS) ZQCL主要用于系统上电初始化和器件复位,一次完整的ZQCL需要512个时钟周期,在随后(初始化和复位之后),校准一次的时间要减少到256周期。ZQCS在正常操作时跟踪连续的电压和温度变化,ZQCS需要64个时钟周期。

在RESET之后的第一次ZQCL必须要512个时钟(tZQINIT)周期进行一次完整的校准。在之后 ZQCL 必须要tZQOPER(256个时钟周期)ZQCS命令在除了ATCIVITIES的任何时间发送,所有的BANK必须Precharged 并要满足tRP的时间要求.

原文地址:参考链接

三、DDR3 工作原理与时序参数

1.DDR3 存储单元结构和原理

一个基本存储单元结构图如下图, storage capacitor为一个基本存储单元,当access transitor被选通时,可读可写:

一个4行3列的DDR 存储器如下图所示:

上图中蓝色的为bit line。相邻行的对应bit的bit line之间有一个两个反相器首尾相连的sense amplifier。红色的为word line,连接了同一行的所有的存储电容的transistor的栅极。

DDR只能选中其中一行,不可同时对两行进行访问。

读操作原理:

- 如上图所示,预充电开关闭合,旁路了sense amplifier,所有的bit line都被充电至1/2 VDD。

- 预充电关闭,因bit line足够长,其可短时间维持1/2 VDD的电压值。

- 所访问行的word line打开,则与存储电容连接的晶体管导通。

- 若电容储存值为1,则存储电容将向bit line充电。因bit line电容远大于存储电容,bit line 电压会冲至略大于1/2VDD。

- 若电容储存值为0,则bit line将向存储电容充电。bit line电容电压将小于1/2VDD。

- sense amplifer将放大其两端奇偶行bit line的电压差别,直到一端是稳定的高电平,而另一端是稳定的L电平。其输出将锁存到行latch,由于整行都被锁存,对该行中的每一个地址的读访问不需要额外的延时。

- 一旦sense amplifier的两端稳定,存储电容将被sense amplifer的输出所刷新。由于bit line较长,sense amplifer电平传输到存储电容需要一定的时间。

- 一旦读取结束,word-line被关闭。sense amplifier被关闭(旁路),所有的bit line重新开始预充电。

写操作原理:

所对应的sense amplifer被强制置为某一个电平,然后由其对存储电容充电或放电。

2.DDR 与 SDRAM区别

DDR SDRAM 全称为 Double Data Rate SDRAM,中文名为“双倍数据流 SDRAM”。DDR SDRAM 在原有的 SDRAM的基础上改进而来。下图是DDR和SDRAM的数据传输对比图

图上可以清楚的看到,DDR SDRAM可在一个时钟周期内传送两次数据,上升沿传一次,下降沿传一次。下面来看DDR的内部结构图的SDRAM有什么不同。

这也是一颗 128Mbit 的内存芯片,标称规格为 32×4bit,右边红框区域就是DDR不同的地方:首先就是内部的L-Bank 规格。SDRAM 中L-Bank 存储单元的容量与芯片位宽相同,但在DDR SDRAM 中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不能再套用讲解 SDRAM时“芯片位宽=存储单元容量”的公式了。也因此,真正的行、列地址数量也与同规格 SDRAM 不一样了。

以本芯片为例,在读取时,L-Bank 在内部时钟信号的触发下一次传送 8bit 的数据给读取锁存器,再分成两路 4bit 数据传给复用器,由后者将它们合并为一路 4bit 数据流,然后由发送器在 DQS 的控制下在外部时钟上升与下降沿分两次传输 4bit 的数据给北桥的内存控制器(在ARM和现在的CPU中,内存控制器是集成在CPU中的,现在的PC机中北桥已无内存控制器)。这样,如果时钟频率为 100MHz,那么在 I/O 端口处,由于是上下沿触发,那么就是传输频率就是 200MHz。

现在大家基本明白 DDR SDRAM 的工作原理了吧,这种内部存储单元容量(也可以称为芯片内部总线位宽)=2×芯片位宽(也可称为芯片 I/O 总线位宽)的设计,就是所谓的两位预取(2-bit Prefetch)。

DDR SDRAM 与 SDRAM 一样,在开机时也要进行 MRS(ModeRegister Set,模式寄存器的设置),不过由于操作功能的增多,DDR SDRAM 在 MRS 之前还多了一 EMRS 阶段(Extended Mode Register Set,扩展模式寄存器设置),这个扩展模式寄存器控制着 DLL 的有效/禁止、输出驱动强度、QFC 有效/无效等。

3. 差分时钟(CK# 与 CK)

图中可知:CLK#与正常 CLK 时钟相位相反,形成差分时钟信号。而数据的传输在 CLK 与 CLK#的交叉点进行,可见**在 CLK 的上升与下降沿(此时正好是 CLK#的上升沿)都有数据被触发,**从而实现双倍数据传输(也就是DDR)。

CK#的作用,并不能理解为第二个触发时钟,而是起到触发时钟校准的作用。由于数据是在 CK 的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求 CK 的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等原因,CK 上下沿间距可能发生变化,此时与其反相的 CK#就起到纠正的作用(CK 上升快下降慢,CK#则是上升慢下降快)。而由于上下沿触发的原因,也使 CL=1.5 和 2.5 成为可能,并容易实现。

![]()

4.行到列寻址延迟 tRCD(RAS-to-CAS Delay)

DDR寻址流程是:先指定Bank地址,再指定行地址,然后指列地址最终的确寻址单元。在实际工作中,Bank地址与相应的行地址是同时发出的,此时这个命令称之为“行激活”(Row Active)。在此之后,将发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以“读/写命令”来表示列寻址。 tRCD 全称是 RAS-to-CAS Delay(RAS至CAS延迟,RAS就是行地址选通脉冲,CAS就是列地址选通脉冲),也就是行寻址到列寻址之间的延迟,是在行有效(行激活)到读/写命令发出的这段时间间隔叫做 tRCD,可以理解为行选通周期,时序图如下:

4. 列选通潜伏时间 tCL(CAS Latency)

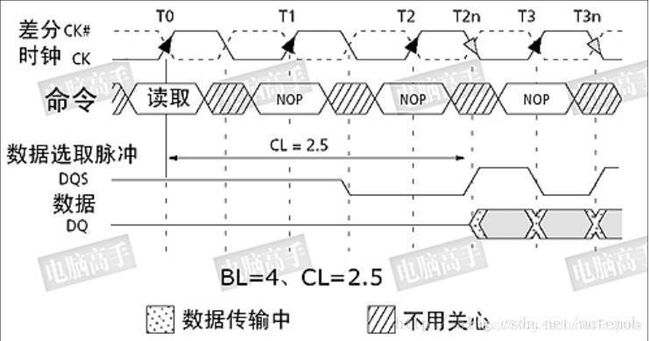

当列地址发出以后就会触发数据传输,但是数据从存储单元到内存芯片 IO 接口上还需要一段时间,这段时间就是非常著名的 CL(CAS Latency),也就是列地址选通潜伏期(可能的选项:1.5/2/2.5/3),以时钟为单位。较低的CAS周期能减少内存的潜伏周期以提高内存的工作效率。因此只要能够稳定运行操作系统,我们应当尽量把CAS参数调低。反过来,如果内存运行不稳定,可以将此参数设大,以提高内存稳定性。(CL 只在读取时出现??)

6. 时钟触发访问时间 tAC(Access Time from CLK)

由于芯片体积的原因,存储单元中的电容容量很小,所以信号要经过放大来保证其有效的识别性,这个放大/驱动工作由S-AMP负责,一个存储体对应一个S- AMP通道。但它要有一个准备时间才能保证信号的发送强度(事前还要进行电压比较以进行逻辑电平的判断),因此从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据即已传向S-AMP,也就是说此时数据已经被触发,经过一定的驱动时间最终传向数据I/O总线进行输出,这段时间我们称之为 tAC(Access Time from CLK,时钟触发后的访问时间)。

7.附加延时 tAL ( Posted CAS Additive Latency )

在 DDR 的发展中,提出了一个前置 CAS 的概念,目的是为了解决 DDR 中的指令冲突,它允许 CAS 信号紧随着 RAS 发送,相当于将 DDR 中的 CAS 前置了。 但是读/写操作并没有因此提前,依旧要保证足够的延迟/潜伏期,为此引入了 AL(Additive Latency),单位也是时钟周期数。

Post CAS就是为了提高DDR2内存的利用效率而设定的,在PostCAS操作中,CAS信号(读写/命令)能够被插到RAS信号后面的一个时钟周期,但实际的CAS命令执行可以在附加延迟(Additive Latency,AL)后面。原来的tRCD(RAS到CAS延迟)被AL所取代,且AL可以在DDR的初始化时进行设置。由于CAS信号放在了RAS信号后面一个时钟周期,因此别的bank激活命令(RAS)和CAS信号就不会产生冲突了。使用AL与不使用AL的时序图如下:

AL使用Post CAS技术,在总线上发出CAS信号(读写/命令)后到这个指令实际被执行的延时。但是对于这个改进有两个地方值得注意的:

1、tRCD依然是存在的,这个是硬件的限制。而Post CAS技术改进的是命令的传输机制。可以这样理解的:Post CAS技术是对CAS信号指令提供一种芯片内部延时的机制,也可以理解为将CAS信号缓存AL时间后执行,这样不妨碍总线上的其他命令的发送。

2、Post CAS技术在单次的突发访问中是没有影响的,只有连续多次的突发访问才有性能的提升,但是对于内存操作一般不可能做单次的突发,就算程序这样做了硬件缓存机制也会做多次的突发。

8.读延时 tRL

tRL :从列地址发出到数据端口上有效的数据输出延时

tRL = tAL + tCL

8.写延时 tWL

从 DDR2 开始还引入了写潜伏期 WL(Write Latency),WL 表示写命令发出以后到第一笔数据写入的潜伏期。WL: WRITE command to first DQS transition写命令与第一个DQS上升沿之间的延迟。tWL = tAL + tCWL

9. 突发访问长度( BL:Burst Length )

目前内存的读写基本都是连续的,因为与CPU交换的数据量以一个Cache Line(即CPU内Cache的存储单位)的容量为准,一般为64字节。而现有的Rank位宽为8字节(64bit),那么就要一次连续传输8次,这就涉及到我们也经常能遇到的突发传输的概念。突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lengths,简称BL)。

在 进行突发传输时,只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。这样,除 了第一笔数据的传输需要若干个周期(主要是之前的延迟,一般的是tRCD+CL)外,其后每个数据只需一个周期的即可获得。发连续读取模式:只要指定起始列地址与突发长度,后续的寻址与数据的读取自动进行,而只要控制好两段突发读取命令的间隔周期(与BL相同)即可做到连续的突发传输。

在 DDR SDRAM 中,突发长度只有 2、4、8 三种选择,没有了随机存取的操作(突发长度为 1)和全页式突发。这是为什么呢?因为 L-Bank一次就存取两倍于芯片 位宽的数据,所以芯片至少也要进行两次传输才可以,否则内部多出来的数据怎么处理?但是,突发长度的定义也与 SDRAM 的不一样了,它不再指所连续寻址的存储单元数量,而是指连续的传输周期数,每次是一个芯片位宽的数据。

10.数据掩码 DM(Data I/O Mask)

如果BL=4,那 么也就是说一次就传送4×64bit的数据。但是,如果其中的第二笔数据是不需要的,怎么办?还都传输吗?为了屏蔽不需要的数据,人们采用了数据掩码 (Data I/O Mask,简称DQM)技术。通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。这里需要强调的是,在读取时,被屏蔽的 数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。DQM由北桥控制,为了精确屏蔽一个P-Bank位宽中的每个字节,每个DIMM有8个DQM 信号线,每个信号针对一个字节。这样,对于4bit位宽芯片,两个芯片共用一个DQM信号线,对于8bit位宽芯片,一个芯片占用一个DQM信号,而对于 16bit位宽芯片,则需要两个DQM引脚。

11.预充电 tRP(Row Precharge command Period)

Prechage:需要precharge的原因,关闭当前行,打开新行时,要求新的bit line充电到VDD/2。在数据读取完之后,为了腾出读出放大器以供同一Bank内其他行的寻址并传输数据,内存芯片将进行预充电的操作来关闭当前工作行。还是以上面那个Bank示意图为例。读出放大器服务单位为行,所以对同一Bank的不同行的操作,需要先关闭现有的工作行,在打开要操作的行。

到可以打开新的工作行之间的间隔就是tRP(Row Precharge command Period,行预充电有效周期),单位也是时钟周期数

WR 值计算: 通过将tWR(ns)除以tCK(ns)并四舍五入到下一个整数,可以计算时钟周期中的WR(自动预充电的写恢复)min:WRmin = Roundup(tWR [ns] / tCK [ns] )。必须将模式寄存器中的WR值编程为等于或大于WRmin。编程的WR值与tRP一起使用以确定tDAL。

12. 数据选取脉冲 tDQS

DQS 是 DDR中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据,用于数据同步。每一颗芯片都有一个 DQS 信号线,它是双向的,在写入时它用来传送由内存控制器发来的 DQS 信号,读取时,则由DDR芯片生成 DQS 向内存控制器发送。

在读取时,DQS 与数据信号 在 CK 与 CK#的交叉点同时生成。实际上,DQS 生成时,芯片内部的预取已经完毕了,由于预取的原因,实际的数据传出可能会提前于 DQS 发生(数据提前于 DQS 传出)。此时 CL 可理解为 列选通(CAS)发出到 DQS 生成的间隔,数据真正出现在数据 I/O 总线上相对于 DQS 触发的时间间隔被称为tAC。

DQS 在写入时,如果以 DQS 的上下沿区分数据周期的危险很大。由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各 I/O 端口的出现时间可能有快有慢,会与 DQS 有一定的间隔,这也就是为什么要有一个 tAC 规定的原因(DDR中的tAC是在DQS触发和数据真正出现在I/O总线上的间隔时间)。而在接收方,一切必须保证同步接收,不能有 tAC 之类的偏差。这样在写入时,芯片不再自己生成 DQS,而以发送方传来的 DQS 为基准,并相应延后一定的时间,在 DQS 的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在 DQS 上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。

13. 写入延迟 tDQSS

在DQS 写入时序图中,可以发现写入延迟已经不是0了,在发出写入命令后,DQS与写入数据要等一段时间才会送达**。这个周期被称为 DQS 相对于写入命令的延迟时间(**tDQSS, WRITE Command to the first corresponding rising edge of DQS)。

为什么要有这样的延迟设计呢?原因也在于同步,毕竟一个时钟周期两次传送,需要很高的控制精度,它必须要等接收方做好充分的准备才行。tDQSS 是 DDR 内存写入操作的一个重要参数,太短的话恐怕接受有误,太长则会造成总线空闲。tDQSS 最短不能小于 0.75 个时钟周期,最长不能超过 1.25 个时钟周期。

正常情况下,tDQSS 是一个时钟周期,但写入时接受方的时钟只用来控制命令信号的同步,而数据的接受则完全依靠 DQS 进行同步,所以 DQS 与时钟不同步也无所谓。不过,tDQSS产生了一个不利影响— — 读后写操作延迟的增加,如果 CL=2.5,还要在 tDQSS 基础上加入半个时钟周期,因为命令都要在 CK 的上升沿发出。下图中,当 CL=2.5 时,读后写的延迟将为 tDQSS+0.5 个时钟周期(图中 BL=2)。

![]()

另外,DDR 内存的数据真正写入由于要经过更多步骤的处理,所以写回时间(tWR)也明显延长,一般在3个时钟周期左右,而在 DDR-Ⅱ规范中更是将 tWR 列为模式寄存器的一项,可见它的重要性。

14.内存的自动自刷新 ASR(Automatic Self-Refresh)

为了保证所保存的数据不丢失,DRAMASR必须定时进行刷新。为了最大的节省电力,DDR3采用了一种新型的自动自刷新设计(ASR,Automatic Self-Refresh)。当开始ASR之后,将通过一个内置于DRAM芯片的温度传感器来控制刷新的频率,因为刷新频率高的话,消电就大,温度也随之升高。而温度传感器则在保证数据不丢失的情况下,尽量减少刷新频率,降低工作温度。不过DDR3的ASR是可选设计,并不见得市场上的DDR3内存都支持这一功能,因此还有一个附加的功能就是自刷新温度范围(SRT,Self-Refresh Temperature)。通过模式寄存器,可以选择两个温度范围,一个是普通的的温度范围(例如0℃至85℃),另一个是扩展温度范围,比如最高到95℃。对于DRAM内部设定的这两种温度范围,DRAM将以恒定的频率和电流进行刷新操作。

15. 局部自刷新 RASR(Partial Array Self-Refresh)

局部自刷新(RASR,Partial Array Self-Refresh)这是DDR3的一个可选项,通过这一功能,DDR3内存芯片可以只刷新部分逻辑Bank,而不是全部刷新,从而最大限度的减少因自刷新产生的电力消耗。这一点与移动型内存(Mobile DRAM)的设计很相似

16.延迟锁定回路(DLL)

DDR SDRAM 对时钟的精确性有着很高的要求,而 DDR SDRAM 有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上 DDR SDRAM 这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况(SDRAM 也有内部时钟,不过因为它的工作/传输频率较低,所以内外同步问题并不突出)。

DDR SDRAM 的 tAC 就是因为内部时钟与外部时钟有偏差而引起的,它很可能造成因数据不同步而产生错误的恶果。实际上,不同步就是一种正/负延迟,如果延迟不可避免,那么若是设定一个延迟值,如一个时钟周期,那么内外时钟的上升与下降沿还是同步的。鉴于外部时钟周期也不会绝对统一,所以需要根据外部时钟动态修正内部时钟的延迟来实现与外部时钟的同步,这就是 DLL 的任务。

DLL 不同于主板上的 PLL,它不涉及频率与电压转换,而是生成一个延迟量给内部时钟。目前 DLL 有两种实现方法,一个是时钟频率测量法(CFM,Clock Frequency Measurement),一个是时钟比较法(CC,Clock Comparator)。

CFM 是测量外部时钟的频率周期,然后以此周期为延迟值控制内部时钟,这样内外时钟正好就相差了一个时钟周期,从而实现同步。DLL 就这样反复测量反复控制延迟值,使内部时钟与外部时钟保持同步。

CC的方法则是比较内外部时钟的长短,如果内部时钟周期短了,就将所少的延迟加到下一个内部时钟周期里,然后再与外部时钟做比较,若是内部时钟周期长了,就将多出的延迟从下一个内部时钟中刨除,如此往复,最终使内外时钟同步。

CFM 式 DLL 工作示意图

![]()

CC 式 DLL 工作示意图

![]()

CFM 与 CC 各有优缺点,CFM 的校正速度快,仅用两个时钟周期,但容易受到噪音干扰,并且如果测量失误,则内部的延迟就永远错下去了。CC 的优点则是更稳定可靠,如果比较失败,延迟受影响的只是一个数据(而且不会太严重),不会涉及到后面的延迟修正,但它的修正时间要比 CFM 长。DLL 功能在 DDR SDRAM 中可以被禁止,但仅限于除错与评估操作,正常工作状态是自动有效的。

17. 写入均衡 Write Leveling

为了提供更好的信号完整性,DDR3的memory controller可以使用write leveling来调整DQS差分对和CK差分对的相对位置,利用DQS差分对路径上的可调整延时来达成该目的。对于DDR的简单运用,比如on-board DDR memory,并且仅有一颗DDR内存的情况下可以考虑不需要做write leveling。 需要写入均衡的情况如下:

#### 1)T型布线:

如下图。该布线方式同步切换噪声(Simultaneous Switching Noise) 较大。

2)fly-by 布线

fly-by 布线 指地址、命令和时钟的布线依次经过每一颗DDR memory芯片(即每一颗芯片共用了这些信号,在Lattice DDR SDRAM controller IP配置时,则ClockWidth要求设置为 1)。而DQ和DQS作了点到点的连接。VTT表示这些信号都接了ODT端接电阻。fly-by 结构相对于T布线,有助于降低同步切换噪声(Simultaneous Switching Noise)。

Write Leveling的功能是调整DRAM颗粒端DQS信号和CLK信号边沿对齐;调节过程描述:DDR控制器不停地调整DQS信号相对于CLK的延迟,DRAM芯片在每个DQS上升沿采样CLK管脚上的时钟信号,如果采样值一直低,则会将所有的DQ[n]保持为低电平来告知DDR控制器,tDQSS(DQS, DQS# rising edge to CK, CK# rising edge,在标准中要求为+/-0.25 tCK。tCK为CLK时钟周期)相位关系还未满足,如果发现在某个DQS上升沿,采样到此时的CLK电平发现了迁越(由之前的低跳变为高),则认为此时DQS和CLK已经满足tDQSS,同时通过DQ[n]向DDR控制器发送一个高,表征一个写均衡成功,同时DDR控制器会锁住这个相位差。这样,在每个DRAM端,看到的CLK和DQS信号都是边沿对齐的。

3)写入均衡的修调过程:

t1:将ODT拉起,使能on die termination;

t2:等待tWLDQSEN时间后(保证DQS管脚上的ODT已设置好),DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=0,则DQ保持为0。

t3:DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=0,则DQ仍然保持为0。

t4:DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=1,则等待一段时间后,DDR memory将dq信号置起。

采取以上策略的原因:对于DDR controller来说,其无法测定clk边沿和dqs边沿的绝对位置,故采用了不断调整dqs delay,在dqs上升沿判断clk从0到1或1到0的一个变化,一旦检测到变化,则写入均衡停止。

DDR3标准的Figure 17 write leveling concept图不太好理解,以下进行说明。

- 从1中的两个信号diff_DQS和DQ,可以看到 diff_DQS的上升沿采到的CK值都是0;

- 将diff_DQS加延时,直到如2 中所示diff_DQS的上升沿采到的CK值都是1,进而DQ输出从0到1,完成写入均衡(write leveling)。

注意:在DDR3的标准文档中,在同一个时序图中经常性看到有多个相同信号名,但波形不同的情况,需要结合上下文分析波形。

4)布线要求:

- 只有使用了fly-by的情况下需使能write leveling

- CPU内部的内存控制器只能对DQS信号做延迟,不能做超前处理,所以CK要大于DQS信号线的长度,否则将不能满足tDQSS

18.ODT有效阻抗 RTT

RTT是ODT的有效阻抗。由MR1寄存器的A9,A6和A2来设定RTT的大小。标准中提到的RZQ电阻为240欧姆,连接在ZQ管脚和VSSQ之间。例如{A9,A6,A2}=001时,RTT=RZQ/4=60欧姆。参见下图(来自DDR3标准) .

![]()

参考电压VDDQ/2, 又称为VTT。其中VDDQ是DQ的供电电压。

在DDR3 标准中定义了两种RTT,即RTT_nom 和RTT_wr,两者分别在MR1和MR2寄存器中设定。如下图。

![]()

在write leveling模式下,仅RTT_nom可用。在写模式下,可以使能RTT_wr来动态改变ODT而不需要重新设置MR寄存器。RTT_nom和RTT_wr间的切换和时序要求参见DDR3标准的5.3 dynamic ODT 一节,以及该节的Table 16 — Latencies and timing parameters relevant for Dynamic ODT。

在DDR3标准中“Controller sends WR command together with ODT asserted”. 如下图,2处为写命令,对应地ODT信号被拉起。5处为读命令,ODT为0,无效。1和4为激活命令,更新bank地址和行地址。3为单bank precharge命令。

![]()

19.其它时序参数解释说明

1)bank预充电 tRP & tRPA

tRP:单个BanK的PRECHARGE命令发出后,需要tRP时间段

tRPA: 所有BanK的PRECHARGE命令发出后,需要tRPA时间段

2)bank激活 tRAS & tRC & tRRD

tRAS 行激活时间:存储区激活命令与发出预充电命令之间所花费的时钟周期数。

**tRC:**同一个Bank之间激活命令的时间间隔被定义为tRC,即连续两次向同一存储体发出的 ACTIVET命令之间的最小时间间隔。tRC = tRAS + tRP

**tRRD:**不同Bank之间的激活命令时间间隔被称为tRRD。

tRFC 刷新指令间隔时间:决定两次刷新时间,那tRFC就注定比tRC时间来的高,所以它们之间是相互配合的关系

3)激活命令时间间隔 tFAW

**tFAW:**在tFAW时间间隔内不能发送超过4个激活(ACTIVATE)命令。

4)读命令之间的时间间隔 tCCD

**tCCD:**CAS#-to-CAS#命令之间的时延。读命令之间的时间间隔。如果要输出数据连续读命令之间的间隔是BL/2 个周期,为什么是BL/2?

因为命令是单速率而数据是双速率,如果突发数据速率是8,那读(写)数据输出只需要4个时钟周期。

5)DQS读同步 tRPRE && tRPST

**tRPRE:**DQS读操作前同步,DQS为低电平,而DQS#为高电平

**tRPST:**DQS读操作后同步,DQS为低电平,而DQS#为高电平

6)杂项

tWTR 内部写到读取命令的延迟: 当写命令之后跟随 读命令时,要满足tWTR的时间间隔要求,从写操作向存储器发送最后一个数据并发出读取后必须插入的延迟。

tWR 写恢复时间: 写数据和发出预充电命令之间花费的时钟周期数,写突发之后一定要跟随一个PRECHARGE命令, 必须使用tWR来确保写绶冲区中的所有数据都可以安全地写入内存内核。

tRDA:读取延迟调整。

四、DDR初始化

1.DDR初始化流程

DDR3内存的初始化过程在JEDEC有详细的介绍,以下是Hynix的文档,内容大同小异,时序图如下:

初始化过程如下:

-

首先上电(RESET#推荐保持在 0.2XVDD;其他的输入没有定义)。RESET#信号需要用稳定电源保持最少200us。在图中可以看出来,CKE需要在RESET#拉高之前被拉低,且最少维持10ns。

-

在RESET#被拉高之后,需要等待500us直到CKE被拉高。在这段时间内,DRAM会开始内部状态的初始化,这个过程是独立于外部时钟完成的。

-

在CKE拉高之前,时钟(CK,CK#)必须开始且稳定至少10ns或5个tCK。图中可以看到一个tIS时间,这个时间是CKE关于时钟的setup时间,因为CKE是一个同步信号。在CKE拉高之前且使用tIS设定自己的同时,NOP和Deselect命令也必须registed。在Reset之后当CKE拉高,CKE就必须持续拉高直到初始化过程结束。图中可以看到CKE持续拉高到tDLLK和tZQinit都截止的时候。

-

在Reset#拉低的时候,DDR3 SDRAM的ODT一直保持高阻态。除此之外,ODT还在RESET#拉高到CKE变高这段时间维持了高阻态。在tIS之前,ODT的输入信号可能在一个未定义的状态。在CKE拉高之后,ODT的输入信号不会变化,一直处于LOW或者HIGH的状态。若是在MR1中设置打开了RTT_NOM,ODT输入信号会处于LOW状态。总的来看,ODT输入信号会维持不动直到初始化过程结束,直到tDLLK和tZQinit截止。

-

在CKE拉高之后,在发送第一个MRS命令到load mode register之前,需要等待tXPR,这个时间是RESET CKE的exit时间。(tXPR公式: tXPR=Max(tXS,5x tCK))

<–!初始化DRR寄存器—>

-

发送MRS命令给MR2(BA0,2=0 and BA1=1)

-

发送MRS命令给MR3(BA2=0 and BA0,1=1)

-

发送MRS命令给MR1 且激活DLL(发送DLL enable命令,需要A0=0,BA0=1且BA1,2=0)

-

发送MRS命令给MR0且 RESET DLL(发送DLL RESET命令,需要A8=1,BA0,1,2=0)

-

发送ZQCL命令开始ZQ校准过程。

-

等待tDLLK和tZQinit完成。

-

DDR3 SDRAM可以开始进行一般操作了。

2.上电复位时序

复位信号RESET#和时钟使能信号CKE信号之间要求满足以下时序:

![]()

对上图中的1, 2, 3和4说明如下:

1)CKE在RESET#有效区间,可以有一段时间不稳定

2)在RESET#释放之前,要求CKE必须在10ns之前稳定为0

3)RESET#释放之后,需要等待500us之后,CKE才可以置为1

4)在电源稳定后,RESET# 需保持至少200us

五、参考链接

参考链接1:DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)

参考链接2:SDRAM的tRCD、CL、tAC的定义

参考链接3:DDR II中的延时参数

参考链接4:DDR3内存的初始化过程

参考链接5:tbzj_2000