1 涉及术语解释

1.1 三模冗余

三模冗余系统简称TMR(Triple Modular Redundancy),是最常用的一种容错设计技术.三个模块同时执行相同的操作,以多数相同的输出作为表决系统的正确输出,通常称为三取二.三个模块中只要不同时出现两个相同的错误,就能掩蔽掉故障模块的错误,保证系统正确的输出.由于三个模块是互相独立的,两个模块同时出现错误是极小概率事件,故可以大大提高系统的可信性。

1.2 Single-Event Upset,SEU

Single-Event Upset (SEU)是指单个空间高能带电粒子击中微电子器件灵敏部位后,由于电离作用产生额外电荷,使器件逻辑状态发生瞬态改变的现象。如果某个重要的程序,逻辑状况发生变化后,会对设备产生较大影响。由于三模冗余技术的简单性以及高可靠性,它是一个被广泛使用的针对于单粒子翻转(Single-Event Upset,SEU)现象的容错技术。

1.3 SRAM 、FLASH FPGA与反熔丝FPGA

从使用的角度进行说明,SRAM FPGA目前是市场主流,工艺简单,逻辑容量大,可重配置。每次断电后,程序消失,上电时需要重新从外部存储器进行加载。

反熔丝FPGA主要用于军工、航天等可靠性要求极高的场景,工艺复杂,逻辑容量小,可靠性极高,只能配置一次。

本文提到的三模冗余存储、烧录、加载控制系统,使用反熔丝FPGA作为主控完成。

1.4 QSPI FLASH

本文提到的处理器主系统使用QSPI接口 FLASH存储软件配置程序,进行写操作时必须先进行擦除,然后才能完成写入,且擦除的最小单位是一个扇区(sector),读出数据则没有大小限制。

本文的FLASH使用QSPI接口,该接口有4条数据线,1条使能线,1条时钟线,属于典型的高速串行同步通讯接口,速率较快。与之对应的有BPI接口,BPI接口属于并行数据接口,数据线与地址线分离,管脚数目庞大,正在逐渐被QSPI等串行接口取代。

2 三模冗余方案

某型号卫星观测相机使用了大容量的SRAM型FPGA作为主控器件,该FPGA程序需要存储在QSPI 接口的FLASH中,本文提到的处理器主系统即使用SRAM FPGA芯片。为了防止存储在QSPI接口FLASH中的bit数据发生SEU,引起SRAM FPGA的错误工作,同时进行在线更新,我们对FLASH内存储的数据、处理器主系统的程序加载进行三模冗余设计。

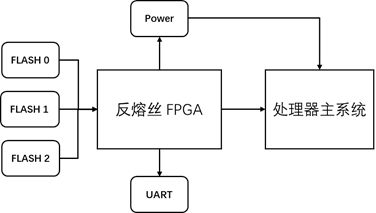

图 2‑1 三模冗余简化设计框图

l FLASH 0/1/2 :三片FLASH分别存储3份SRAM FPGA的软件配置项;

l UART :串口负责对反熔丝FPGA进行调试与状态监测、控制反熔丝FPGA对FLASH 0/1/2 进行程序烧录;

l Power :受反熔丝FPGA的控制,用于控制SRAM FPGA的上电、下电;

l 反熔丝FPGA:作为该系统的高可靠主控设备,负责执行UART收到的控制指令、执行FLASH的擦除、读写、执行SRAM FPGA的启动控制;

l 处理器主系统:是本发明要服务的设备。

系统上电后,反熔丝FPGA开始运行,代码内部的三个FLASH控制器首先通过读取FLASH器件的dummy值对FLASH的读写时序进行调节、校验,校验通过后再接收相同的读地址,并对应发出SPI读操作,FPGA读取三片FLASH存储单元中的数据,三份数据被数据比较模块两两异或,比较其内容的一致性,若存在数据错误,则用正确数据覆盖错误数据,并记录错误BIT信息,最后将统计到的错误数据输出。

在比较的过程中,如果检查到某片FLASH数据有错误,需要对其错误的扇区进行擦除,并写入正确的数据,那么这里就需要首先对正确的数据进行备份,反熔丝FPGA内部的SRAM资源十分有限,无法用作备份,因此使用FLASH 0 20MB地址处的64KB区域进行正确数据的备份。

图 2‑2 三模冗余校验过程

流程图提到的代码边界是指SRAM FPGA配置程序的边界,比如我们FLASH的大小实际是32MB,而SRAM FPGA的配置程序实际是6MB,那么对应的程序边界就是6MB,我们在进行三模冗余时,只需要对应的比较6MB的数据即可,可以大大的节约时间。