这是IC男奋斗史的第12篇原创

关注公众号【IC男奋斗史】,让我们一起撸起袖子加油干!

本文2116字,预计阅读6分钟。

接上文:凤姐如何变冰冰?

本文主要介绍芯片后道封测流程。

3 芯片封装

芯片封装的流程也很复杂,通常也需要经历几十甚至上百道工序,这里我主要给大家介绍下其中的一些关键环节。

封装的第一道核心工序是晶圆切割,切割之前通常会按要求对晶圆背部进行打磨(backgrind),使其达到封装需要的厚度。

然后再把晶圆按照die的大小进行切割,切割过程中会用纯水一边清洗一边降温,切割完成后晶圆上的每一颗die就会独立出来。

最后再根据CP测试输出的Inkless Map把晶圆上CP测试pass的die取出来去做封装。

对于不同的封装形式,接下来的流程都不尽相同。这里我们以FCBGA和QFP为例,给大家做简单叙述。

对于FCBGA封装,接下来我们会把基板、die和金属散热片堆叠在一起,就形成了通常我们看到的FCBGA芯片的样子。基板相当于一个底座,为die提供电气与机械界面。金属散热片主要负责die的散热,同时也和基板一起对内部的die起保护作用。

对于传统的QFP封装,接下来我们会把die放到引脚框架(leadframe)里边,leadframe通常是矩形结构,可以同时放置多个die。

然后再对每一个die进行打线(wire bonding),将die内部的pad引出到leadframe的引脚上,使内部的die到外部的引脚建立电气连接。接下来再给leadframe中每一个放die的位置灌入塑封材料,使die密封在内部。

最后再把leadframe按照每一个die位置切开,并把引脚压弯,这样QFP封装的芯片就成型了。

芯片封装是沟通芯片内部世界与外部电路的桥梁,同时还可以起到安放、固定、密封、保护芯片和增强电热性能的作用,是半导体制造业的核心技术。芯片封装就好比给芯片穿上外套,不同形式的封装代表不同样式的外套,使用环境各不相同,价格也各不相同。

而且随着摩尔定律逐渐接近极限,未来半导体集成度提高的方向很可能会往封装方面发展,2.5D/3D封装技术也是目前半导体行业最前沿最热门的研究领域之一。

了解芯片封装流程对于从事芯片封装相关的岗位来说是很有必要的,尤其是封测厂技术人员,或者芯片研发团队的封装相关岗位如产品工程师、封装设计工程师、封装NPI工程师等,都属于必备技能。

4 FT测试

FT是Final Test的缩写,通常是芯片出货前的最后一道测试。FT测试属于芯片级测试,是通过测试板(Loadboard)和测试插座(Socket)使自动化测试设备(ATE)到封装后的芯片之间建立电气连接。FT测试的目的是筛选出满足设计规格的产品卖给客户。

FT测试需要的硬件设备包括测试板、测试插座、ATE测试机台、Handler以及Change Kit。其中Handler也称为自动化分类机,是用来实现FT测试自动化的设备,Change Kit属于Handler的配套治具。

测试工程师需要基于ATE测试平台开发FT测试程序,内容通常包括电气连接性测试、功能测试和参数测试等。程序会根据测试结果Pass或者Fail进行物理分Bin,也就是说把pass和fail芯片物理上分到不同的容器中。

这里我们也会把不同类型的Fail芯片分到不同的物理容器中,方便对特定类型的fail芯片进行分析或者重测。

FT测试结果也是以良率的形式进行统计,FT良率就是指pass芯片占测试芯片总数的百分比。FT测试是保证芯片质量的最后一道关卡,也是芯片测试阶段最重要的环节。

理想的FT测试程序是100%覆盖率,也就是说所有的测试项目全部放在FT测试阶段。但是这样做的成本是非常高的。

首先,FT测试Fail损失的是封装后的芯片,包含了封装的成本。其次,较高的测试覆盖率需要更多的ATE测试资源,也就意味着FT测试并行度会降低,这样会增加测试成本。两个site并行测试比一个site单独测试肯定要划算。所以,需要将FT测试与CP测试综合考虑才能找到相对优化的测试方案。

例如,有一些对封装不敏感的测试项,我们就放在CP测,FT不测;有一些跟封装关系特别密切的测试项,我们就可以放在FT测,CP不测。总之,芯片测试(CP和FT)是一个整体,需要综合考量,找到较好的测试方案。

5 SLT测试

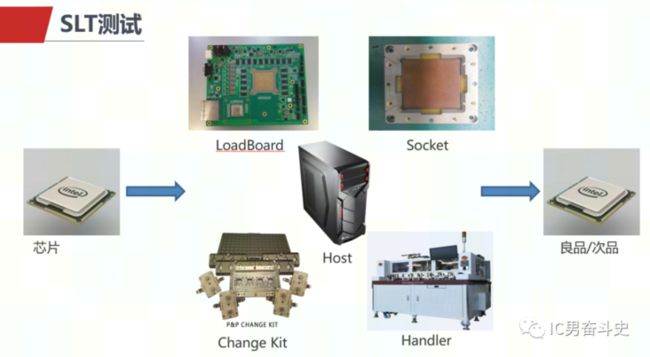

SLT是System Level Test的缩写,SLT测试属于板级或系统级测试,也是通过测试板和测试插座使测试主机到封装后的芯片之间建立电气连接。SLT测试的目的是提高产品板生产良率,减少产品板生产成本。

通常,半导体公司如果直接出售芯片一般不需要做SLT测试,FT测试完成后就可以直接出货给客户。但是有很多半导体企业都是出售搭载芯片的产品板给客户,或者像Intel处理器这样功能相对固定的芯片,需要在FT测试之后再加一道SLT测试。

SLT测试需要的硬件设备包括测试板、测试插座、Handler、Change Kit以及测试主机与连接线等。

SLT测试属于定制化测试,软件部分灵活度比较高,不需要基于自动化测试平台开发,完全由测试工程师自主开发。

SLT测试内容通常包括芯片功能测试、高速接口测试以及DDR内存相关的测试等。与FT测试相同,程序会根据测试结果Pass或者Fail对芯片进行物理分Bin。

SLT测试结果也是以良率的形式进行统计,SLT良率就是指pass芯片占测试芯片总数的百分比。

从目前半导体发展的趋势看,在5G、物联网和人工智能的大力发展与推动下,专用型芯片已经逐渐成为未来的主流形式。相应的,SLT测试在芯片测试领域的受重视程度也越来越高。在不久的将来,SLT测试很可能将会成为芯片测试中最重要的环节。

了解FT测试和SLT测试对于从事半导体封装测试相关的岗位比较重要,尤其是封测厂如日月光、安靠、长电等测试相关的技术人员,或者芯片研发团队的量产相关岗位如产品工程师、测试工程师等,都属于必备的基础知识。

花了这么多时间,终于把芯片生产测试流程给大家讲清楚了。希望我讲的内容能让大家对芯片的生产测试流程有一些了解,知道芯片是怎么来的。如果你正在或者将来从事半导体行业,希望这些内容能够帮助到你。

全文完。

相关文章:

凤姐如何变冰冰?

文末扫码加杰哥微信,免费提供各种半导体行业研报:

END

关注公众号【IC男奋斗史】,让我们一起撸起袖子加油干!![]()

●第三次“世界大战”——芯片保卫战,无烟的战场!

●系列文(下):这是我们的黄金时代

●系列文(上):芯荒荒,汽车芯片路在何方

●芯片工程师太贵,贵你妹啊!