2022英伟达(NVIDA)实习生笔试(ASIC PD岗位)

昨晚刚考完。感觉好难/(ㄒoㄒ)/~~

太久没看Verilog题目了。第一题的4-1MUX 就耗费我宝贵20min。第二题的脚本,完全不会。开头暴击。第三题好点,但是也不确定参数是否都对了。第四题,证明等价性,把组合逻辑转换成逻辑表达式,怕时间来不及,就没化简,匆匆说了功能一样,感觉要完。第五、六题,应该还好。第七题,会的都写上去了,timing report怎么看还是要复习复习。第八题的波形图,画的太匆忙,大体应该是对的。第九题,怎么优化,就记得useful skew了。第十题,没看懂,瞎画的时候,时间到了。

复盘一下:

- Verilog题目要多刷(免得手生,浪费时间)

- 脚本要多练习

- 对于specification一定要学会翻译理解并且计算参数

- 数电的基础知识要牢记

- 要熟悉timing report(report里的每一个东西都要知道是是什么)

- 整理时序优化的方法

【提示:全英文题目。10题,时间2h】

1、Verilog题

写2选1MUX的代码,并且用2选1的MUX,写4选一的MUX代码。并且画出这两个MUX的电路原理图。

2、script

Given 5X5 gird, find one possible shortest path for any unigue point. Please print the all the points one by one in the shortest path. Use C/C++/Per/Python.

For example:

Given 2 point (1,1) and (5,4), one possible path is @(3,1),(3.1) (4,1), (5,1)1(5.2),(5,3)(5,4)

3、

给出几个命令,里面的参数是空缺的。根据给出的条件,把这些参数补充完整。

几个命令大概是:

create clock -period [get ports clk1]

set _clock_uncertainty [get_clocks clk1]

set clock latency -source [get_clocks clk1]

set clock latency [get_clocks clk1]

set_input_delay [get _ports A]

set_output_delay [get_portsB]条件大概是:

- Clock clk has a frequency of 500 Mhz.

- The maximum external clock generator delay to the clock port is 700ps. (HINT: source latency)

- The maximum insertion delay from the clock port to all the register clock pins is 300ps +/- 30ps.

- jitter+margin 50ps

- FF2的 setup time 是???ps

- 从外部的数据输入端,到FF1的数据输入端是0.8ns

4(下面只是一个大概印象的图,不一定正确)

门级网表 netlist a优化成netlist b. 两个网表正在使用形式验证工具证明这两个网表是否逻辑等价

(1) combinaional 和 sequentialogic之间的差异? cassitsy sequential and combinational logic of cell A/B/C in netlist a.

2) 证明netlist a/netist b是否 logical equivalent ,并且说明原因

5、同步FIFO

write clock frequency 1024MHz

read clock frequency 768MHz,

write data bus 和 read data bus 8 bits,

1)计算这个FIFO的 minimum depth

2) assume this asynchronous fifo uses gray coded buses to transfer the write/read pointers, how to constrain the skew of the gray code bus?

6、

1) Please draw the MUX truth table and logic expression. (Control signalisS pin).

2) Please define the clock propagated through DIV2 if we only allow CLK1 propagated

3) If CLK1 and CLK2 are asynchronous, which path does not check timing in general?

a. Path between FF1 and FF2

b. Path between FF3 and FF4

C. Neither a nor b

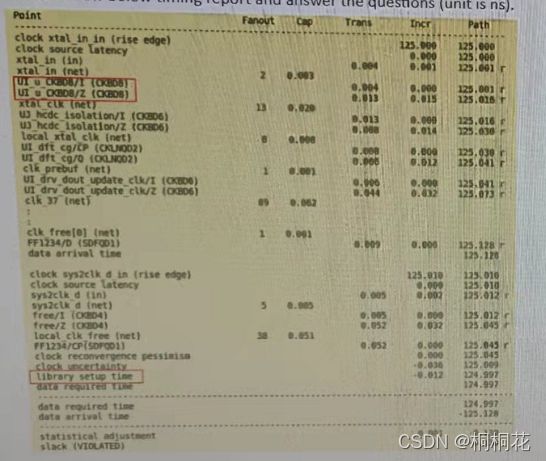

7、观察timing report并回答问题(单位ns)

1) for the cell"Ul_u_CKBD8" from the setup check report,

a. What's the cell delay from I-> Z?

b. Which two input variables are needed to calculate it based on the library timing table? Find the two values from below report?

2) for the "library setup time" from the setup check report,

a. What's the value?

b. Which two input variables are needed to calculate it based on the library timing table? Find the two values from below report?

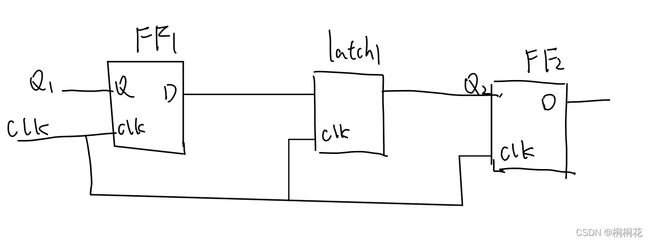

8、

1) 画Q2和Q3的时序波形图?

2)解释在这个电路里, latchL1 怎么用来优化 hold timing

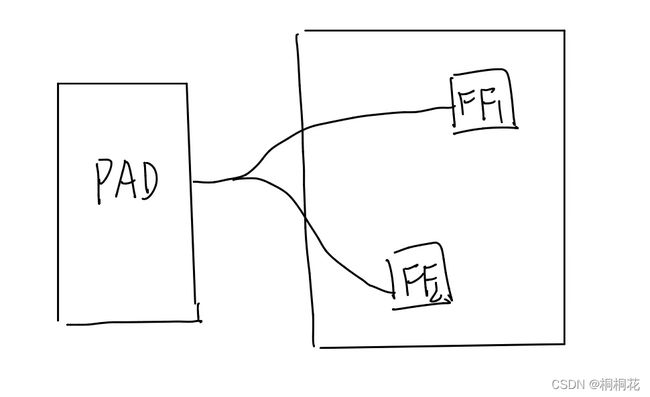

9、(示意图,具体细节记不清了)

(1)IO是什么

PAD的IO 是8位,有8个IO 题数据流是66mhz,问你PAD带宽是多少

(2)从PAD到FF1和FF2之间的时序路径,怎么优化,列出至少两个方法。

10、给出两个波形

画上升沿触发或者下降沿触发的,min pluse 波形(好像是这样)