基于Quartus-II的全加器设计

基于Quartus-II的全加器设计

- 目录

- 一、全加器

-

- 1、概念简述

- 2、真值表

- 二、原理图与VHDL设计初步

-

- 1、新建工程

- 2、新建原理图文件

- 3、将项目设为可调用的元件

- 4、半加器仿真

- 5、设计全加器顶层文件

- 6、设计项目设置为顶层文件并编译仿真

- 7、引脚绑定以及硬件下载测试

- 三、Verilog实现1位全加器

- 四、总结与参考资料

-

- 1、总结

- 2、参考资料

目录

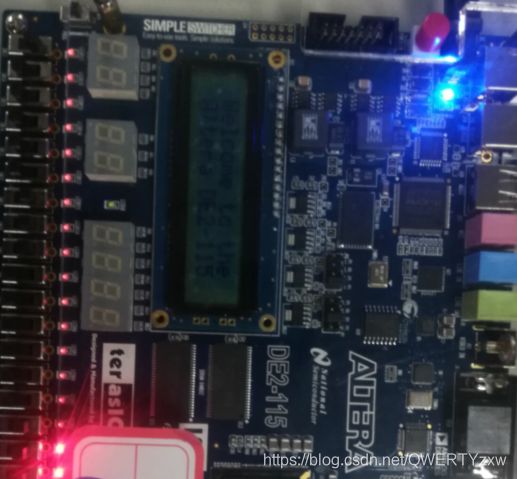

基于Quartus-II软件完成一个1位全加器的设计,分别采用:1)原理图输入 以及 2)Verilog编程 这两种设计方法。软件基于quartusII 13.0版本,开发板基于Intel DE2-115。

一、全加器

1、概念简述

全加器英语名称为full-adder,是用门电路.实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

2、真值表

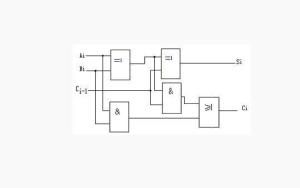

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci

描述

一位全加器的表达式如下:

Si=Ai⊕Bi⊕Ci-1

第二个表达式也可用一个异或门来代替或门对其中两个输入信号进行求和:

硬件描述语言Verilog 对一位全加器的三种建模方法:

有关全加器的更多认识,可以参考

全加器.

二、原理图与VHDL设计初步

通过1位全加器的详细设计,掌握原理图输入以及Verilog的两种设计方法

开发环境:quartus 13.0;开发板Intel DE2-115

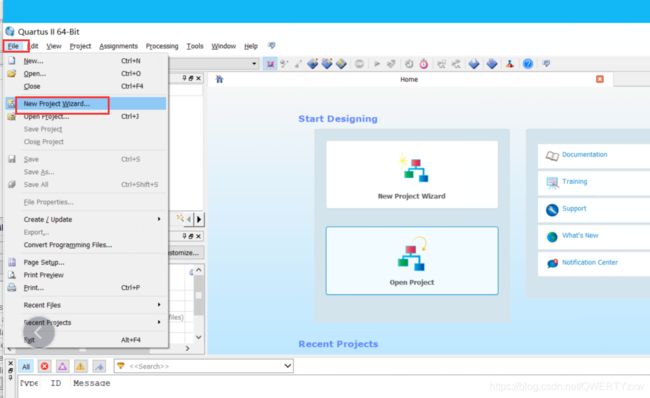

1、新建工程

定义文件位置

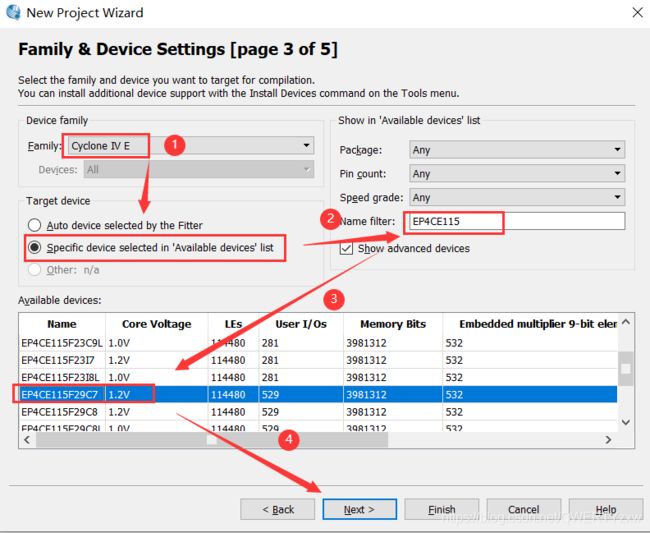

选择目标芯片,cycloneIVE系列的EP4CE11529C7

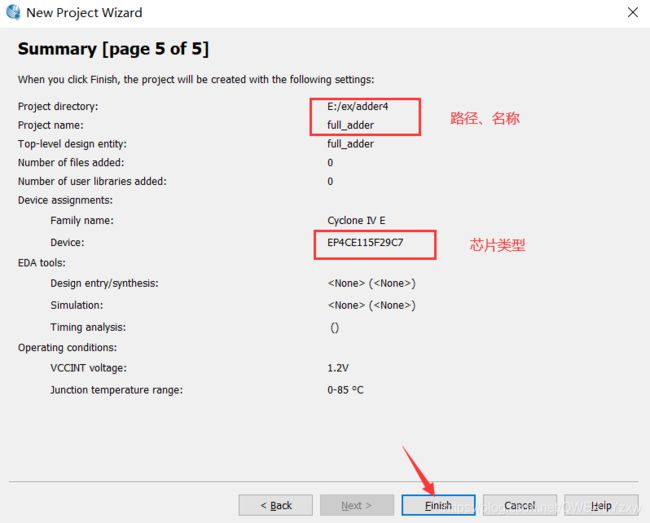

核对工程信息,点击finish

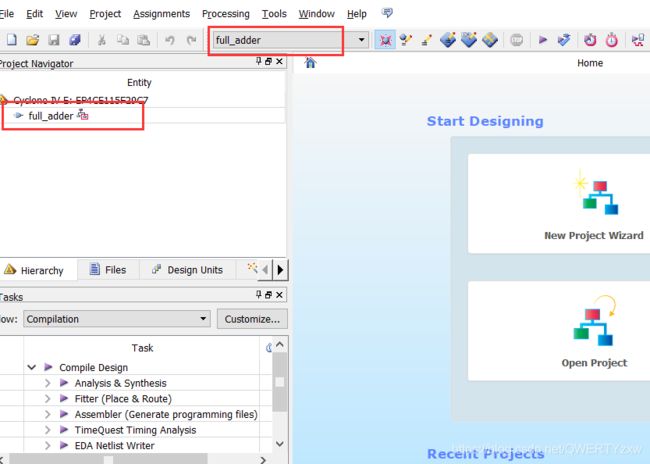

主界面如图

2、新建原理图文件

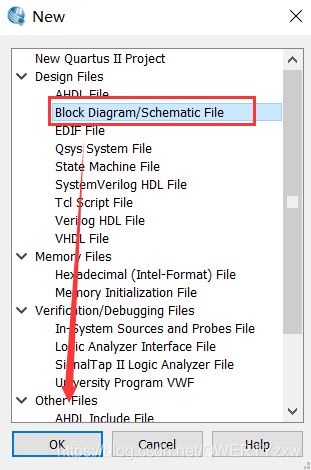

【file】—>【new】—>【design files】—【block …】—>【OK】

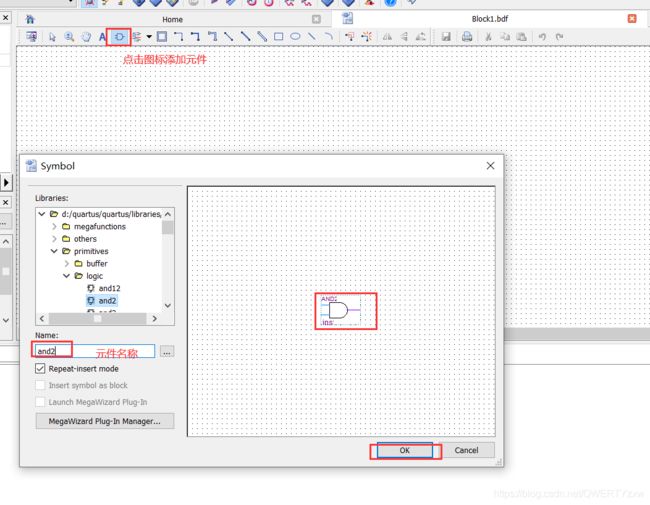

添加元件,完成半加器原理图输入

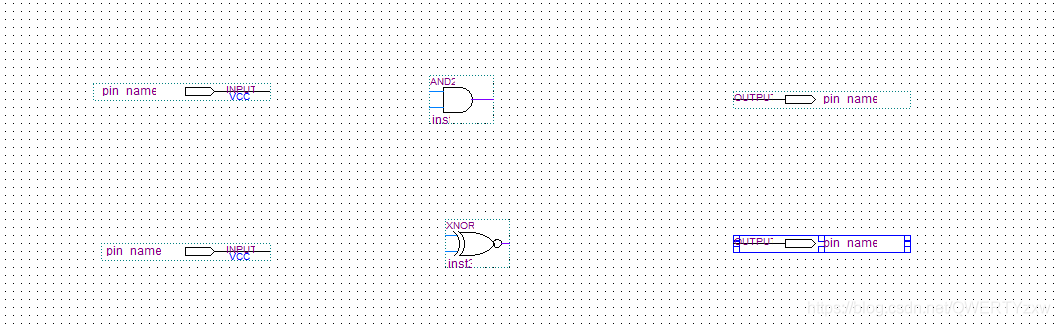

设计半加器,分别调入元件and2,not,xnor和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。然后分别在input和output的PIN NAME上双击使其变黑色,再用键盘分别输入各引脚名:a、b, co和s。

3、将项目设为可调用的元件

为了构成全加器的项层设计,必预将以上设计的半加器half_adder.bdf

设置成可调用的元件。

打开原理图文件,选择菜中File中的Create/Update→Create Symbol Files for

Current File项,即可将当前文件h_adder. bdf变成一个元件符号存盘,以

待在高层次设计中调用。

使用完全相同的方法也可以将VHDL文本文件变成原理图中的一个元件

符号,实现VHDL文本设计与原理图的混合输入设计方法。转换中需要注意以

下两点:

〔1)转换好的元件必须存在当前工程的路径文件夹中;

(2)该方法只能针对被打开的当前文件。

4、半加器仿真

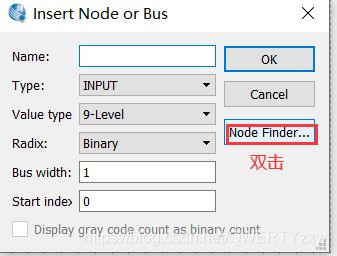

新建波形文件

导入波形文件

按照图示步骤操作

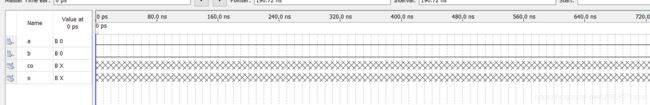

出现如图波形文件

设置波形取值,选取某段需要数值设为“1”

保存

出现报错

解决方法

点击start compilation

再次编译

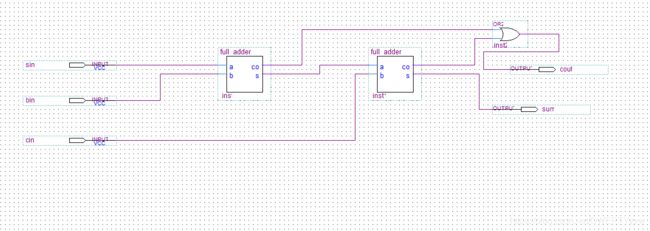

5、设计全加器顶层文件

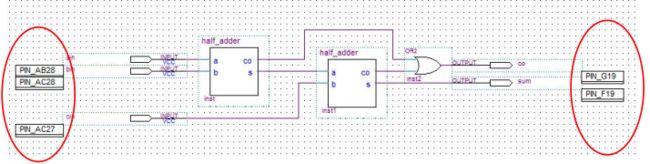

为了建立全加器的项层文件,必须再打开一个原理图编辑窗,即新建一

个原理图文件。方法同前,即再次选择菜单" File”→“new",原理图文件

编辑输入项"Block Diagram/Schematic File"。与调入元件的方法一样,即在新打开的原理图编辑窗双击鼠标,在弹出的“symbol”窗的“name”栏输入底层文件半加器的存储名“half_adder”调出半加器,如图。

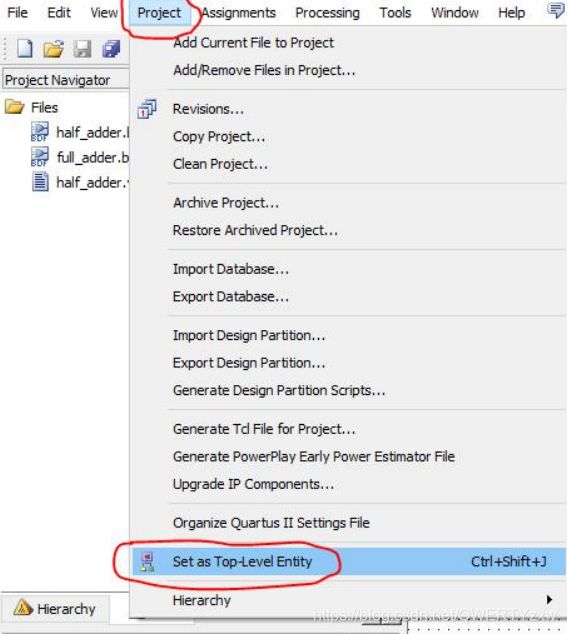

6、设计项目设置为顶层文件并编译仿真

project—>set as top_level entity(Ctrl+shift+J)

编译仿真

7、引脚绑定以及硬件下载测试

选择目标芯片:cycloneIVE系列的EP4CE11529C7 (若在新建工程时就

已经指定目标芯片,则这步可以省略),在菜单中选择,“assignments→device…”

从弹出的“device”对话框中选择目标芯片: cycloneIVE系列的

EP4CE11529C7:(注:”family”选择“ cycloneIVE”,然后下面的芯

片中把状态条拖到最后,选择“EP4CE11529C7”)。

引脚绑定前先要确定具体硬件电路,即目标芯片与外围电路(输入、输出显

示等)的连接情况。

开发板上的18个拨码开关选其中三

个,SW0,SW1,SW2分别接ain、bin、cin(开关向上拨和向下拨分别显示输入

是高还是低电平);LED0,LED1分别接co和sum,灯亮表示输出为“1”,灯灭

表示输出为“0”。

硬件设计好后,还需要查引脚图(引脚图见附录)进行引脚绑定。

菜单中选择“assignments→pin planner”,如图,调出引脚绑定窗口,然后从下拉窗口中选择相应的输入输出端口,再在“location”栏填入对应的 FPGA 引脚即可

选定了引脚之后原理图文件一定要再编译一次,才能真正把引脚绑定上。引脚绑定好并编译过的文件如图:

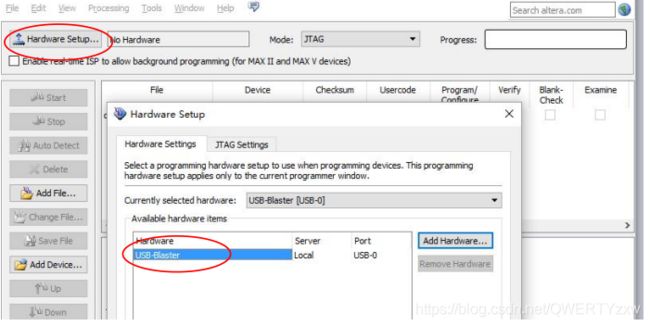

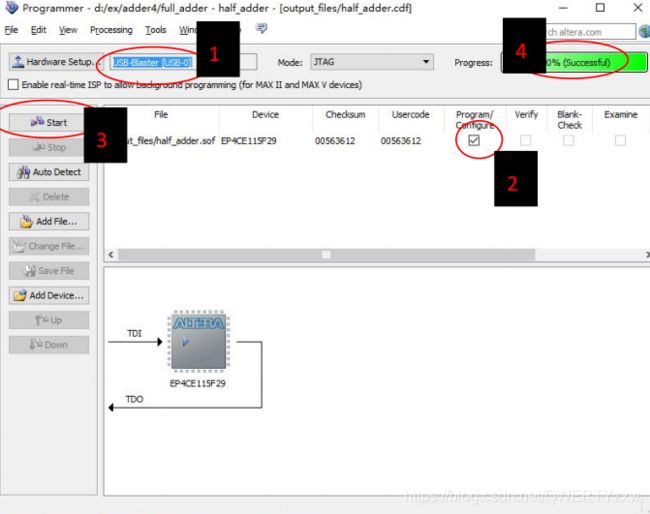

测试

安装好硬件的界面如图。然后在下载的.sof 文件后面的复选框中打勾,再点击”start”,当进度条达到 100%时,即下载成功,可以进行硬件观测。

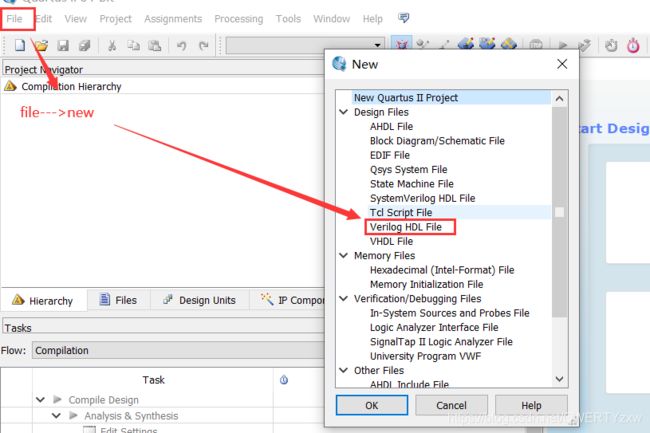

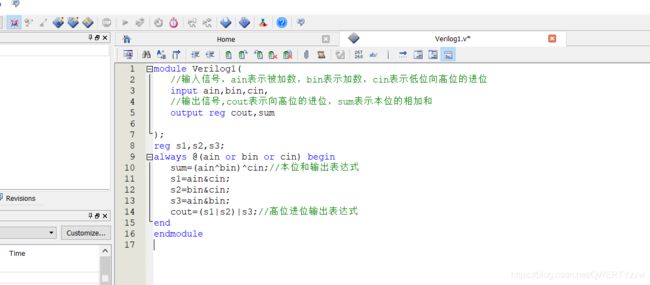

三、Verilog实现1位全加器

module Verilog1(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

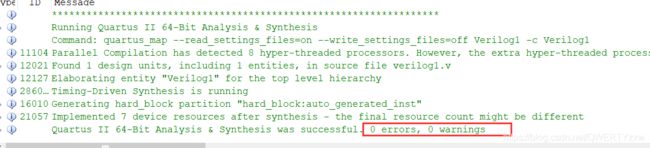

保存

设为顶部文件

编译

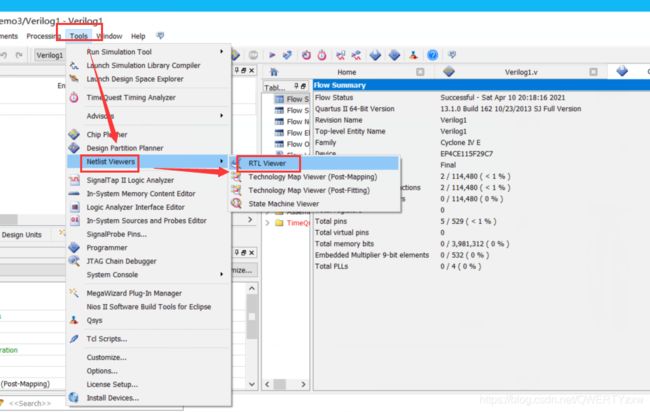

查看电路图按图示操作

电路图

仿真结果(步骤同上)

四、总结与参考资料

1、总结

详细叙述 1 位加法器的设计流程;给出各层次的原理图及其对应的仿真波形图;给出加法器的时序分析情况;最后给出硬件测试流程和结果。

2、参考资料

嵌入式系统应用开发-实验1-FPGA编程入级.