ARM AMBA AHB-LITE协议理解

1.AHB总线的特性

主要包括四点:burst 传输,单时钟沿,非三态实现和支持的数据位宽为8/16/32/64/128一直到1024位,但是受限于cpu的总线位宽,如果是32位,则最多支持32位宽,关于Burst传输的含义从别处看到的,如下:

Burst传输实质就是只发送一次地址,某些总线发送每个数据都要对应发送其地址。但是Burst传输就是提高了传输效率,在一次传输过程中,只发送一次地址。

但burst传输有应用限制,不是所有传输类型都适合burst传输,一般busrt传输应用在下面三种场景:

Flash应用类型

只发送一次地址,之后地址自动累加,直到所有数据发送完成。

Cache应用类型

只发送一次地址,之后地址自动累加,累加到一定值后地址又自动回到初始地址。数据传输在一段地址范围内,循环传输。

FIFO应用类型

只发送一次地址,之后地址不变,所有数据都是传送到此地址。

这也就解释了协议后面的特殊地址是否回卷的burst的意义。

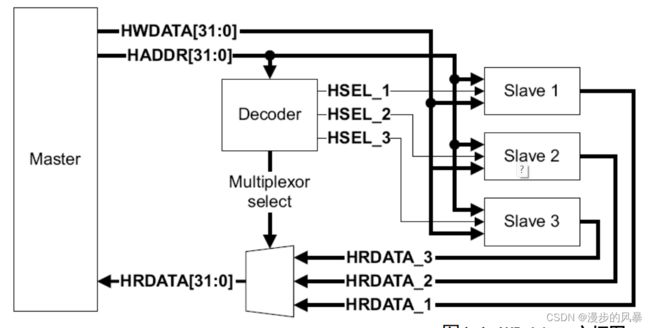

2.AHB总线的基本框架图

图中,decoder为一个译码器,主要用于监控从主设备出来的地址数据和控制信号,给到从设备;multiplexor select为多路选择器,用于将从设备的输出数据反馈给主设备;

AHB一般用于与需要高带宽的存储设备进行通信,如果一般外设寄存器或者IO的通信通过APB桥挂到AHB上。

3.AHB总线的操作

主设备通过驱动地址和控制信号来发起一个传输. 这些信号提供了传输地址、传输方向、传输位宽的信息,并且指示是否是Burst传输的一部分. 传输可以是:

• 单一传输

• 递增Burst传输,在地址边界不回卷

• 回卷Burst传输,在特殊的地址边界回卷

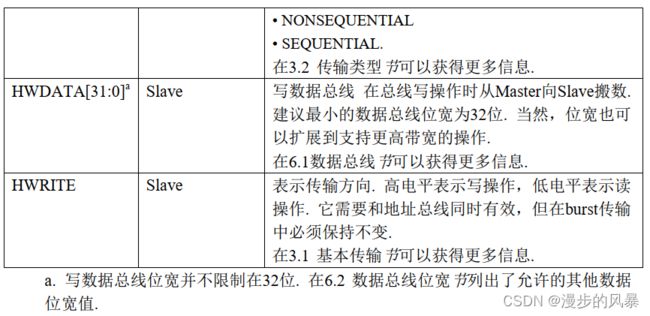

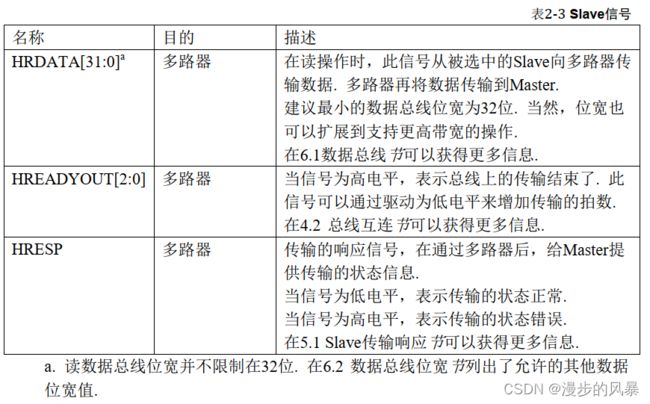

写数据总线从主设备向从设备搬数据,读数据总线从Slave向Master搬数.

每一个传输有如下组成:

Address Phase 地址相位 一个地址和控制周期

Data Phase 数据相位 一个或多个数据周期

Slave无法请求扩展地址相位,因此所有的Slave必须具有在地址相位采集完地址信息

的能力。但是, Slave可以使用HREADY信号请求Master扩展数据相位。 HREADY

信号,为低时,将会在传输过程中插入等待状态,从而可以使Slave有足够的时间提

供数据或采集数据。

Slave通过HRESP信号指示传输成功或者失败。

4.多层AHB总线

多层AHBlite主要是在面对多主的时候进行主访问隔离并能够共享slave,这里对multi-layer interconnect的仲裁有要求,个人认为当多主同时访问slave的时候策略,会影响效率。

5.AHB总线的传输信号

AHB信号包括全局信号、MASTER信号、SLAVE信号、译码器信号和多路器信号,直接从ahb的官方手册中将信号定义截取,如下:

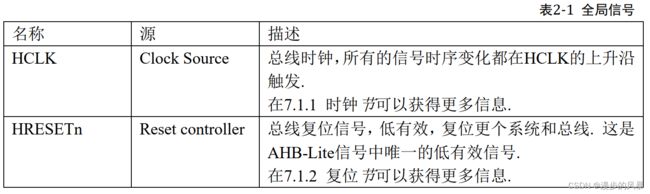

5.1全局信号

5.2MASTER信号

5.4 译码器信号

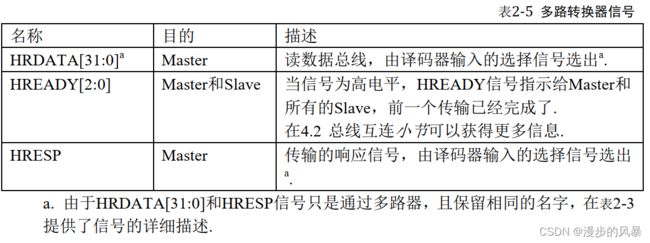

5.5 多路器信号

6.AHB的传输

ahb的传输时许需要的时候可以去查手册,这里阅读之后,总结了一些注意点:

1.如果Master要求锁定访问,则它必须置位HMASTLOCK信号,这个信号指示给所有

Slave当前传输不可被打断,必须在任何其他的传输执行之前执行此传输。

2.如果总线位宽32,则传输size只能配置程8、16和32.

3.HSIZE信号和HBURST信号关联起来,决定了回卷Burst传输的地址边界

4.burst传输包括递增型和回卷型,回卷Burst在跨越地址边界的时候回卷. 地址边界由传输大小和在这个burst的拍数计算得出,Master禁止发起一个跨越1KB地址边界的递增型Burst,burst的传输举例,在官方手册中有详细描述。

7.AHB的总线地址译码

中央地址译码器提供选择信号, HSELx,给总线上每一个Slave. 选择信号是地址总线高位的组合逻辑译码. 鼓励使用简单的地址译码电路而不是复杂译码逻辑,以确保高速操作.Slave必须只能在HREADY为高电平(表示当前传输已经完成)时,采样HSELx,地址和控制信号. 在某种情况下,有可能HSELx在HREADY为低电平时置位为高,但是必须在当前传输完成时改变选中的Slave.

单个Slave可以分配的最小地址空间是1KB. 所有的Master设计为执行的递增传输地址不能跨越1KB地址边界. 这样保证了Burst传输不会跨越地址译码边界.

8.AHB总线的slave传输

在Master开始一个传输之后, Slave控制这个传输的进程. Master不能取消已经开始的传输,当Slave被访问时,必须提供响应,来指示传输的状态. 传输状态由HRESP信号提供.

这意味着Slave可以用以下三种方式完成总线传输:

· 立即完成传输

· 插入一个或多个等待状态,为完成传输提供足够的时间

· 发送错误响应来指示传输失败

这三种Slave传输响应分别对应以下三个状态:

· 传输完成

· 传输挂起

· 错误响应

9.AHB的数据总线

数据总线的位宽会影响系统的性能,当时钟频率固定的时候,可以适当提高总线的位宽来提高传输速率,官方给出了三种情形下的描述:

在宽总线上实现窄位宽的 Slave

在窄总线上实现宽 Slave

在宽总线实现 Master

具体参考官方手册。

10.时钟和复位

每个AHB-Lite组件使用一个单独的时候信号, HCLK. 所有的输入信号都在HCLK的上升沿采样. 所有的输出信号的改变都必须在HCLK的上升沿后发生.

复位信号, HRESETn,是AHB-Lite系统中仅有的低有效信号,它是总线所有元素

的初始复位. 复位 异步复位,在HCLK上升沿同步撤销.在复位期间,所有的Master确保地址和控制信号都处于有效的电平值,并且HTRANS[1:0]类型指示为IDLE.

在复位期间,所有的Slave必须确保HREADY为高电平.