MCS-51单片机内部结构——CPU结构 单片机原理学习笔记(二)

CPU结构

8051内部CPU是一个字长为二进制8位的中央处理单元,也就是说它对数据的处理是按字节为单位进行的。与微型计算机CPU类似,8051内部CPU也是由算术逻辑部件(ALU)、控制器(定时控制部件等)和专用寄存器组三部分电路构成。

1.算术逻辑部件

8051的算术逻辑部件ALU是一个性能极强的运算器,既可以进行加、减、乘、除四则运算,还可以进行与、或、非、异或等逻辑运算,还具有数据传送、移位、判断和程序转移等功能。

8051算术逻辑部件ALU由一个加法器、两个8位暂存器(TMP1和TMP2)和一个性能卓越的布尔处理器组成。虽然TMP1和TMP2对用户并不开放,但可用来为加法器和布尔处理器暂存两个8位二进制操作数。

2.定时器控制部件

定时器控制部件起着控制器的作用,由定时控制逻辑、指令寄存器和振荡器(OSC)等电路组成。

指令寄存器IR用于存放从程序存储器EPROM/ROM中取出的指令(即操作)码,定时控制逻辑用于对指令寄存器中的操作码进行译码,并在OSC的配合下产生执行该指令的时序脉冲,以完成相应指令的执行。

3.专用寄存器组

专用寄存器组主要用来指示当前要执行指令的内存地址,存放操作数和指示指令执行后的状态。它是任何一台计算机都不可缺少的组成部件。专用寄存器组主要包括程序计数器PC、累加器A、程序状态字PSW、堆栈指示器SP、数据指针DPTR和通用寄存器B等。

(1)程序计数器PC

程序计数器PC是一个二进制16位的程序地址寄存器,专门用来存放下一条将要执行指令的内存地址,能自动加1。

8051程序计数器PC由16个触发器构成,故他的编码范围为0000H~FFFFH,共64K。也就是说,8051对程序存储器的寻址范围为64KB。

(2)累加器A

累加器A又记做ACC,是一个具有特殊功能用途的二进制8位寄存器,专门用来存放操作数或运算结果。在CPU执行某种运算前,两个操作数中的一个通常应放在累加器A中,运算完后累加器A中便可以得到运算结果。

(3)通用寄存器B

通用寄存器B是专门为乘法和除法设置的寄存器,也是一个二进制8位寄存器,由8个触发器组成。该寄存器在乘法或除法前,用来存放乘数或除数,在乘法或除法后用于存放乘积的高8位或除数的余数。

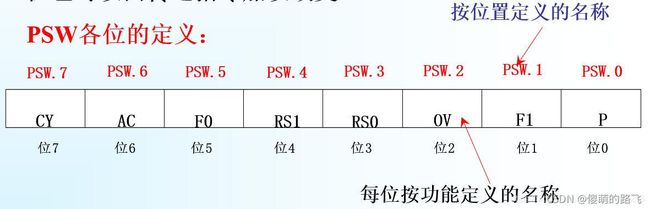

(4)程序状态字PSW

PSW是一个8位标志寄存器,用来存放指令执行后的有关状态。PSW中的各位状态通常是在指令执行过程中自动形成的,但也可以由用户根据需要采用传送指令加以改变。

PSW.7为最高位,PSW.0为最低位。

① 进位标志位Cy:用于表示加减运算过程中最高位A7(累加器最高位)有无进位或借位。在加法运算时,若累加器A中最高位A7有进位,则Cy=1;否则,Cy=0。在减法运算时,若A7有了借位,则Cy=1;否则Cy=0。此外,CPU在进行移位操作时也会影响这个标志位。

②辅助进位标志位AC:用于表示加减运算时低4位(A3)有无向高4位(即A4)进位或借位。若AC=0,表示加减过程中A3没有向A4进位或借位;若AC=1,表示加减过程中A3向A4有了进位或借位。

③用户标志位F0:F0标志位的状态通常不是机器在执行指令过程中自动形成的,而是由用户根据程序执行需要传送指令确定。一经设定便由用户程序自动检测,以决定用户程序流向。

④寄存器选择位RS1和RS0:8051共有8个工作寄存器,分别命名为R0~R7,工作寄存器R0~R7常常被用户用来进行程序设计,但它在RAM中的实际物理地址是可以根据需要选定的。RS1和RS0就是为了这个目的提供给用户使用,用户通过RS1和RS0的状态可以方便的决定R0~R7的实际物理地址。

⑤溢出标志位OV:可以指示运算过程中是否发生了溢出,在机器指令过程中自动形成。若在机器在执行运算指令过程中,累加器A中运算结果超过了8位能表示的范围,即-128~+127,则OV标志自动置1;否则OV=0。

⑥奇偶校验位P:PSW.1为无定义位,用户也不可使用。PSW.0为奇偶标志位P,用于指令运算结果中1的个数的奇偶性,若P=1,则累加器A中1的个数为奇数;若P=0,则累加器A中1的个数为偶数。

(5)堆栈指针SP

堆栈指针是一个8位寄存器,能自动加1或减1,专门用来存放堆栈的栈顶地址。堆栈是一种能按“先进后出”或“后进先出”规律存数据的RAM区域。这个区域可大可小,常称为堆栈区。8051片内RAM共有128B,地址范围为00H~FFH,故这个区域中任何一个子域都可以用作堆栈区,即作为堆栈来使用。

(6)数据指针DPTR

数据指针DPTR是一个16位寄存器,由两个8位寄存器DPH和DPL拼成。DPH为DPTR的高8位,DPL为DPTR的低8位。DPTR可以用来存放片内ROM的地址,也可以用来存放片外RAM和片外ROM地址,主要用于访问片外RAM。