SV中基于覆盖率驱动验证技术(CDV)和生成-查看覆盖率报告

目录

基于覆盖率驱动的验证技术(CDV):

代码覆盖率

断言覆盖率

定义功能覆盖率模型

covergroup解释

功能覆盖率的采样事件

定义覆盖点:bins

定义覆盖点:条件覆盖

定义覆盖点:状态跳转覆盖

定义覆盖点:交叉覆盖

生成覆盖率报告和查看覆盖率报告:

微信公众号

基于覆盖率驱动的验证技术(CDV):

覆盖率是对RTL设计功能进行验证后达到的覆盖百分比

(1)检查过程需满足完整性,就是cover到文档中所有功能;

(2)满足正确性;

代码覆盖率

衡量测试案例验证-覆盖了哪些设计规则在RTL中实现了,而不能衡量验证计划;

1、行(Line Coverage):RTL中的代码行;

2、有限状态机(FSM Coverage):RTL代码中的有限状态机的状态和状态之间的转换;

3、路径(Path Coverage):RTL代码中的路径分支(if-else语句);

4、信号翻转(Toggle Coverage):RTL代码中的一个信号从0跳变到1,以及1跳变到0;

5、表达式(Expression coverage):RTL代码中的条件表达式,例如if(a&b&c);

断言覆盖率

Assertion Coverage断言覆盖率:

1、断言是一种声明性的代码,一般插到RTL中,用于检查RTL代码中的信号之间的关系,也就是做时序检查;

定义功能覆盖率模型

covergroup解释

作用:

(1)封装覆盖率模型的规格,是用户定义的一种;结构类型

(2)每个covergroup包含以下内容:一个时钟事件,用于同步采样覆盖点;一组覆盖点;

(3)跟class类似,完成定义后,可以通过构造函数new()生成covergroup的实例;

(4)covergroup可以定义在module,program,interface,class中;

功能覆盖率的采样事件

带有event触发的covergroup,当验证平台触发trans_ready事件时,采样CovPort;

event trans_ready;covergroup CovPort @(trans_ready);coverpoint ifc.cb.port;endgroup

这里的trans_ready可以换成ck.sample()、@(posedge clk)、@(port)

定义覆盖点:bins

定义bins时

(1)用户限制覆盖率统计时需要的数值;

(2)SystemVerilog不再自动创建bins,并且忽略非用户定义的bins值;

(3)只有用户定义的bins的值才可以用于计算机功能覆盖率;

covergroup CovKind;coverpoint tr.kind {bins zero = {0};bins lo = {[1:3],5};bins hi[] = {[8:$]};bins misc=default;}endgroup

定义覆盖点:条件覆盖

(1)使用关键字 iff为覆盖点添加条件

当reset=1时,不收集覆盖率

covergroup CoverPort;covergroup port iff(!bus_if.reset);endgroup

(2)使用start和stop函数

在reset序列期间,停止收集覆盖率

initial beginCovPort ck=new;#1ns bus_if.reset=1;ck.stop();#100ns bus_if.reset=0;ck.start();...end

定义覆盖点:状态跳转覆盖

(1)用户定义覆盖点的状态跳转,并收集相关的信息

covergroup CoverPort;coverpoint port{bins t1=(0=>1),(0=>2),(0=>3);bins t2=(1,2=>3,4)}endgroup

(2)使用?等通配符表示状态和状态跳转

bit [2:0] port;covergroup CoverPort {wildcard bins even={3'b??0};wildcard bins odd={3'b??1};}endgroup

定义覆盖点:交叉覆盖

在覆盖率组中,可以定义两个或多个覆盖点或者变量之间的交叉覆盖率

class Transaction;rand bit [3:0] kind;rand bit [2:0] port;endclasscovergroup CovPortkind: coverpoint tr.kind; // 0~15port: coverpoint tr.port; // 0~7cross kind,port;endgroup

也就是有16 x 8 个仓(bin)

生成覆盖率报告和查看覆盖率报告:

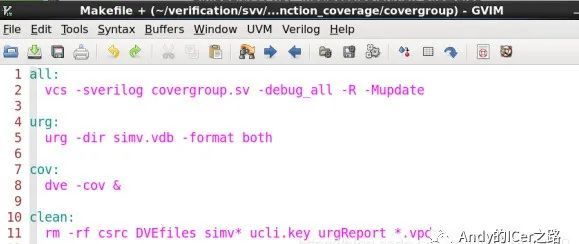

vcs -sverilog covergroup.sv -debug_all -R -Mupdate(1)使用-Mupdate进行增量编译,再次编译时只编译改变的文件,提高速率;

(2)vcs仿真的2个步骤:

代码编译:如 vcs cpu.v

仿真运行:如 simv

或者通过-R选项将2个步骤合成一步:

编译运行:如vcs -R cpu.v,

-R :run after compilation,编译后继续执行runsim.vdb就是覆盖率文件

两种方法打开sim.vdb查看覆盖率:

(1)dve -cov&,然后打开覆盖率文件就可以查看

(2)urg -dir ./*.vdb -format both -report coverage,这个就是生成html和text两种格式覆盖率报告,放在coverage文件夹里,然后进入coverage文件夹,firefox dashboard.html和gvim dashboard.txt两种方式都可以打开覆盖率报告。

Makefile

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验,文章主要在公众号上发,csdn会尽量同步更新,有兴趣的朋友可以关注一下!

![]()