Xilinx ISE系列教程(2):LED点灯工程、仿真、bit下载和mcs固化

文章目录

-

-

- 1. 创建工程目录

- 2. 新建ISE工程

- 3. 新建verilog源文件

- 4. 新建testbench仿真文件

- 5. ISim功能仿真

- 6. 管脚分配和时钟约束

- 7. bit文件生成和下载

- 8. mcs文件生成和下载

-

上一篇文章,我们介绍了ISE 14.7的下载、安装和注册,在之后的文章,我们会以Xilinx Spartan-6系列FPGA XC6SLX16为例,不涉及FPGA开发知识,仅仅是工具的使用,介绍Xilinx ISE开发环境的使用教程和使用技巧。

本篇文章介绍如何使用ISE创建一个点灯工程,完成工程创建、设计输入、功能仿真、综合、管脚分配和程序下载固化,这也是FPGA的典型开发流程。

1. 创建工程目录

为了便于后续的工程文件管理,我们先创建led_demo文件夹,这也是我们的工程顶级目录,在此文件夹下再创建如下6个文件夹:

rtl:用于存放verilog rtl文件

tb:用于存放testbench文件

flash:用于存放生成的bit和mcs文件

ucf:用于存放管脚约束文件

modelsim:用于存放modelsim工程,如果使用自带的isim仿真器,此目录可省略

doc:用于存放文档,比如芯片的数据手册,官方的应用文档等

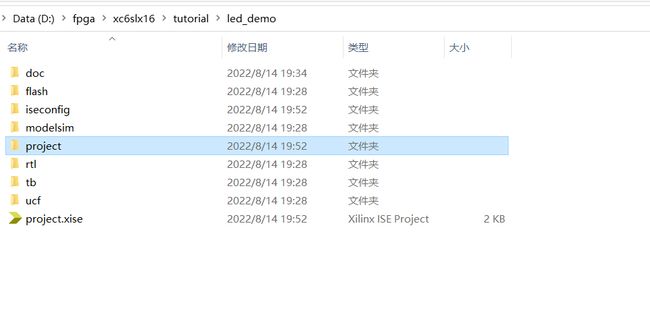

创建完成后,如下图所示:

2. 新建ISE工程

工程文件夹创建完成后,下面我们来创建ise工程。

启动ISE 14.7,点击New Project启动工程创建向导。

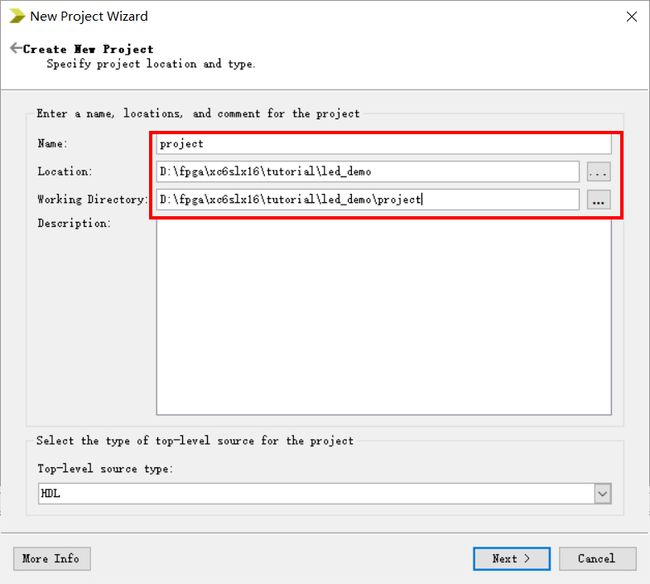

指定工程的存放路径,如下图所示,这样创建出的工程结构比较简洁。

选择FPGA器件型号、封装和速度等级:

创建完成后的工程目录结构:

3. 新建verilog源文件

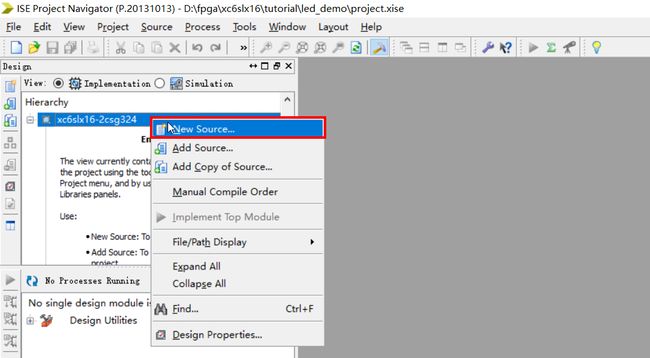

在FPGA器件名称上右键,选择New Source:

选择Verilog Module,并指定文件名称和存放路径。

输入如下LED点灯代码,功能为:外部50M时钟分频为1Hz,LED 500ms亮,500ms灭。

/***************************************************************

* Copyright(C), 2010-2022, WeChat: mcu149

* ModuleName : top_hdl.v

* Date : 2022年8月14日

* Time : 19:59:06

* Author : mcu149

* Function : led blink module

* Version : v1.0

* Version | Modify

* ----------------------------------

* v1.0 .....

***************************************************************/

module top_hdl(

//Inputs

input gclk,

input greset,

//Outputs

output led

);

//1.localparam

localparam LED_PERIOD = 50_000_000;

localparam LED_ON = 1'b1;

localparam LED_OFF = ~LED_ON;

//2.parameter

//3.reg

reg [31:0] cnt;

//4.wire

wire rst_n = !greset;

//5.assign

assign led = (cnt < LED_PERIOD/2) ? LED_OFF : LED_ON; //500ms 0 + 500 ms 1

//6.always

always @ (posedge gclk) begin

if(!rst_n) begin

cnt <= 'd0;

end

else begin

if(cnt == LED_PERIOD)

cnt <= 'd0;

else

cnt <= cnt + 1;

end

end

//7.instance

endmodule

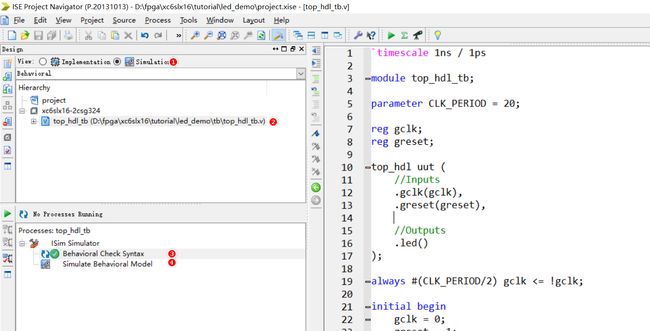

4. 新建testbench仿真文件

和源文件同样的添加方式,选择Verilog Test Fixture,文件名命名为top_hdl_tb,存放路径选择我们最初创建的tb文件夹。

选择要仿真的verilog文件:

输入如下激励代码:

`timescale 1ns / 1ps

module top_hdl_tb;

parameter CLK_PERIOD = 20;

reg gclk;

reg greset;

top_hdl uut (

//Inputs

.gclk(gclk),

.greset(greset),

//Outputs

.led()

);

always #(CLK_PERIOD/2) gclk <= !gclk;

initial begin

gclk = 0;

greset = 1;

#100;

@(posedge gclk);

greset = 0;

end

endmodule

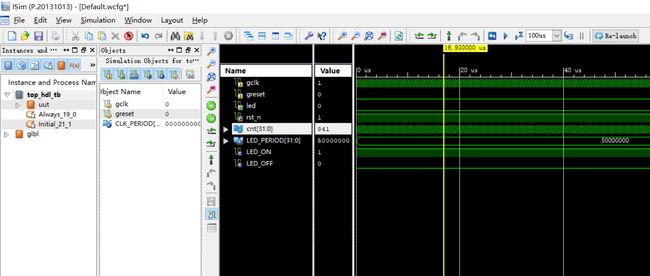

5. ISim功能仿真

切换到Simulation选项卡,检查testbench文件的语法,如果无误,点击Simaulate Behavioral Model。

会启动ISE自带的ISim仿真工具进行功能仿真。

ISim的界面和Modelsim非常类似,如果你使用过Modelsim,那么ISim你也可以直接上手使用。

不同的是,ISim并不支持以模拟的方式显示计数器的变化。

我们代码中设计的LED周期是1s,为了缩短仿真的时间,我们改为250个时钟周期:

改完之后,保存,在ISim界面点击Re-Launch图标,这样仿真文件就更新了。

重新执行复位,并启动仿真,可以看到仿真结果和我们的设计是一样的。

仿真完成后,别忘了把LED周期再改回1s。

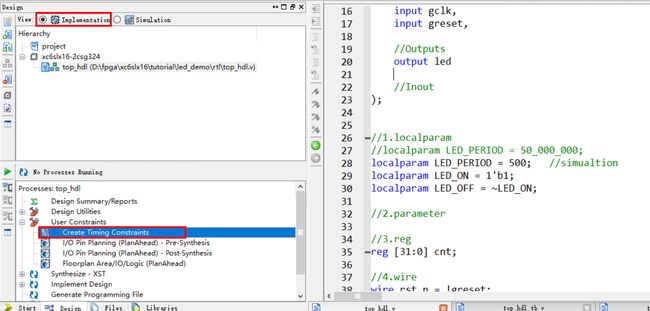

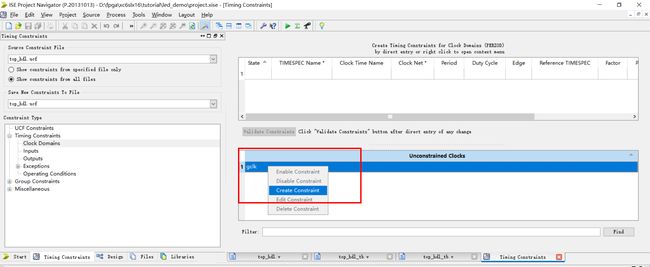

6. 管脚分配和时钟约束

功能仿真正常后,我们来进行管脚分配和时钟约束。

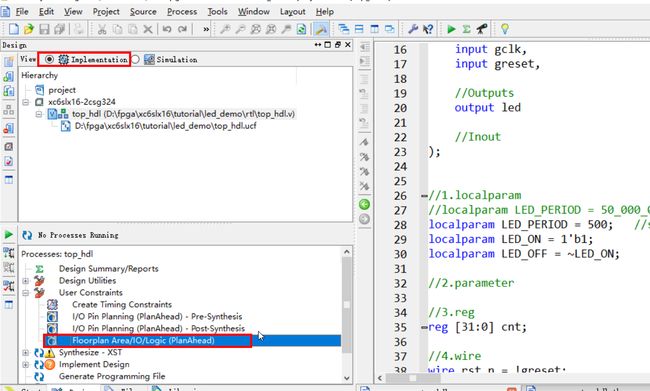

切换到Implementation选项卡,选中顶层设计,点击User Constraints->Create Timing Constraints,创建时钟约束

耐心等待综合完成,在弹出的界面选择要约束的时钟Create Constraint。

指定时钟周期20ns和占空比50%。

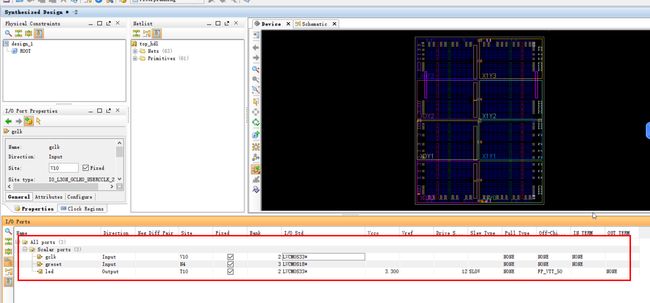

选择Floorplan Area/IO/Logic进行图形化管脚分配。

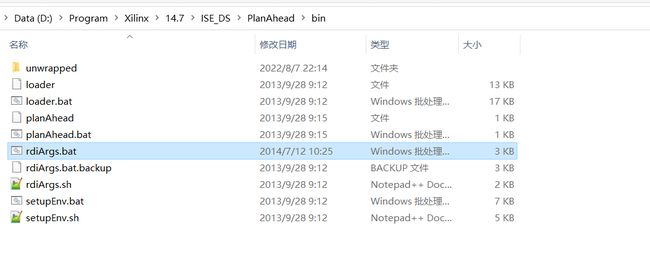

ISE在Windows 8/10环境下使用图形化管脚分配工具PlanAhead时,会出现闪退情况,需要替换安装目录下的\Xilinx\14.7\ISE_DS\PlanAhead\bin\rdiArgs.bat文件。

rdiArgs.bat文件的下载地址:

https://download.csdn.net/download/whik1194/86400515

如果无法下载,可以在评论区留言。

替换完成后

根据实际硬件电路的管脚和电平标准进行分配。

也可以使用文本编辑器直接编辑top_hdl.ucf文件,文件内容如下:

#Created by Constraints Editor (xc6slx16-csg324-2) - 2022/08/14

NET "gclk" TNM_NET = "gclk";

TIMESPEC TS_gclk = PERIOD "gclk" 20 ns HIGH 50 %;

NET "greset" LOC = N4;

NET "greset" IOSTANDARD = LVCMOS18;

NET "led" LOC = T10;

NET "led" IOSTANDARD = LVCMOS33;

NET "gclk" LOC = V10;

NET "gclk" IOSTANDARD = LVCMOS33;

7. bit文件生成和下载

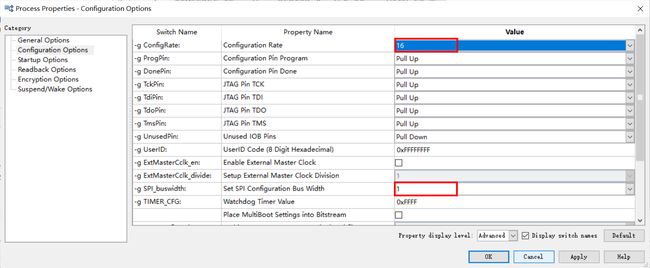

管脚分配和时钟约束完成之后,就可以生成最终的程序文件了,右键Generate Programming File,选择Process Properties进行配置。如果FPGA使用的是SPI x 1的Flash则无需配置,直接生成bit文件即可。

bit流生成配置选项很多,支持生成bit/bin/ascii格式的bin文件,是否压缩,配置速度,配置管脚的上下拉,用户ID,数据加载速度,SPI总线宽度,是否支持Readback,程序加密等等。

我们主要关注以下几个配置选项:ConfigRate和SPI_buswidth。

ConfigRate:指的是FPGA上电后,从外部SPI Flash读数据的时钟速度,涉及到程序上电后的执行速度,不要超过所使用的SPI Flash的最大读速度

SPI_buswidth:指的是外部SPI Flash配置电路的数据线宽度,一般是1位数据线,也有是QSPI 4位数据线,根据实际配置电路来选择。

我的板子使用的是ST M25P80芯片,1位数据线,最高读取速度为20MHz,

SPI Flash的最高读取速度为20MHz。

设置完成之后,双击Generate Programming File生成bit流文件。

如果语法无误,时序满足,就会在project目录下生成top_hdl.bit文件。

点击Configure Target Device打开烧录工具。

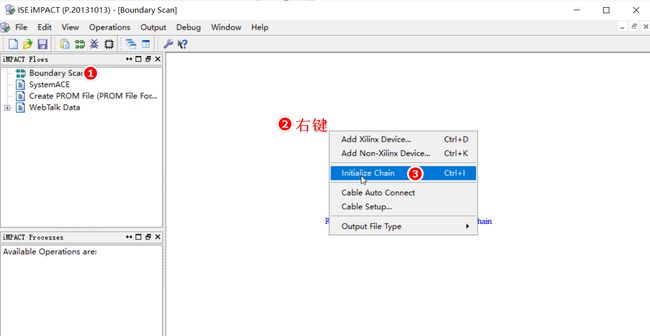

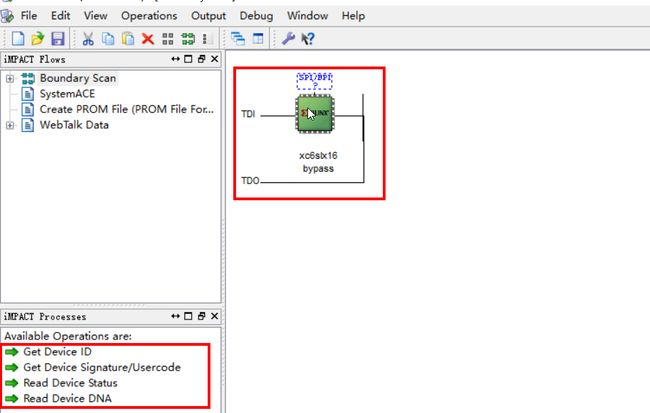

在打开的iMPACT工具中,点击Boundary Scan边界扫描,在右侧的空白区右键点击Initialize Chain连接到FPGA芯片。

双击FPGA芯片,指定bit文件,加载完成后右键执行烧写。

这样,FPGA程序就会下载到内部的RAM中。

8. mcs文件生成和下载

bit文件下载之后,可以看到LED按照我们设计的1s周期闪烁起来了,但是此时如果断电,重新上电程序就丢失了。

我们还需要把程序固化到外部的SPI Flash,这样每次掉电重启后,FPGA先从外部的SPI Flash中读取程序,再加载到内部RAM中进行运行。程序固化不能直接使用bit文件,需要根据不同的SPI Flash型号和大小重新生成一个mcs格式的文件。

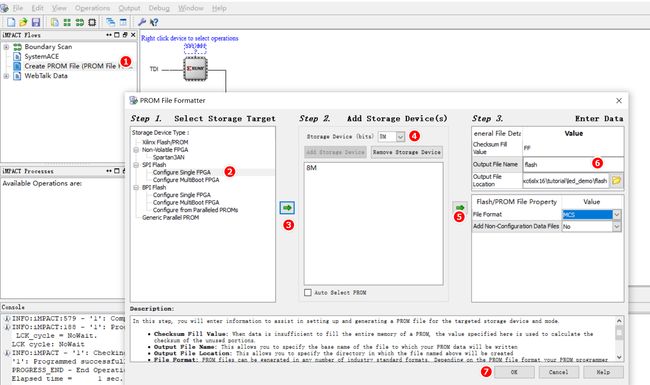

点击Create PROM File,选择SPI Flash的大小,并指定mcs文件的存储路径和文件名。

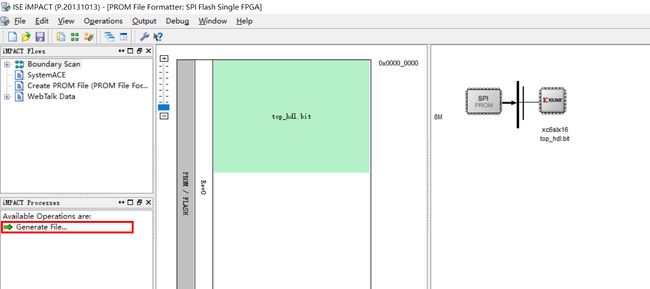

选择完成之后,加载生成的bit文件,点击左侧Generate File,生成mcs文件。

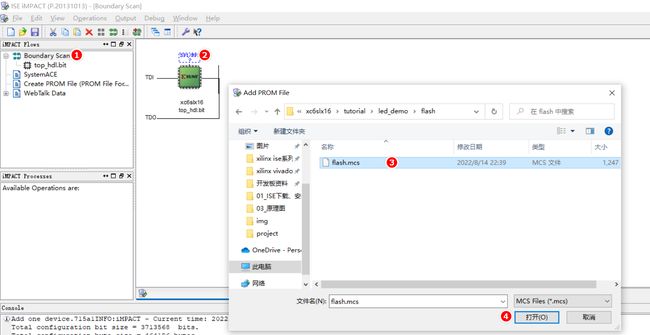

生成成功后,我们回到边界扫描界面,选择外部SPI Flash,并加载mcs文件。

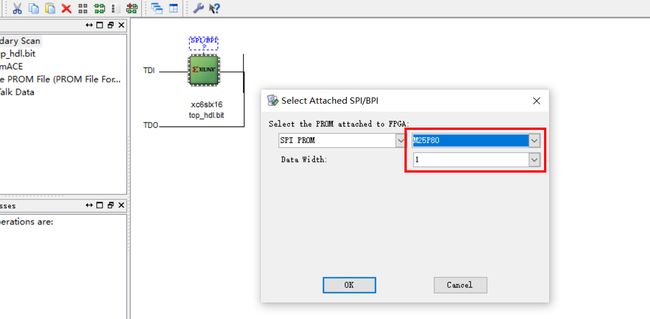

选择SPI Flash的型号和数据线宽度,需要和生成bit时指定的数据宽度保持一致。

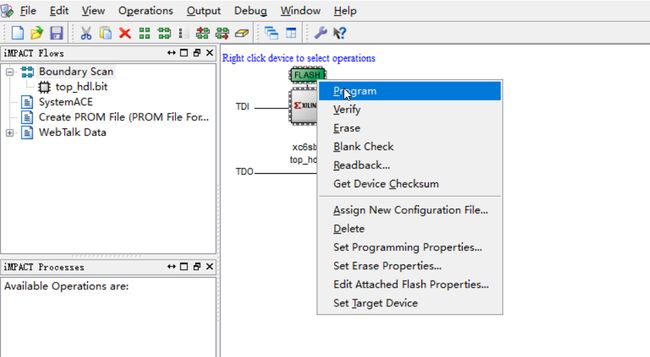

在外部SPI Flash上右键执行编程。

由于是使用JTAG通过FPGA对外部SPI Flash进行编程,这个过程会比下载bit文件慢很多,耐心等待下载完成。

'1': Erasing Device.

'1': Using Sector Erase.

'1': Programming Flash.

'1': Reading device contents...

done.

'1': Verification completed.

'1':Programming in x1 mode.

'1': Programmed successfully.

INFO:iMPACT - '1': Flash was programmed successfully.

LCK_cycle = NoWait.

LCK cycle: NoWait

INFO:iMPACT - '1': Checking done pin....done.

'1': Programmed successfully.

PROGRESS_END - End Operation.

Elapsed time = 19 sec.

下载完成后,每次掉电重启程序就可以正常运行了。

关于bit文件和mcs文件格式的描述,可以查看历史分享的博文:

- Xilinx Bit文件格式详解

- HEX(Xilinx MCS)文件格式详解

简单理解可以认为bit文件是bin文件加了文件头,hex文件是bin文件加了地址和校验信息。

在flash文件夹,新建copyBit.bat批处理文件,内容如下:

copy ..\project\top_hdl.bit .\flash.bit

这样每次,只需要双击这个文件,就可以自动把工程目录下的top_hdl.bit文件复制到flash文件夹下了。

还可以结合iMPACT执行脚本的功能,来实现一键bit文件下载,一键bit转mcs,一键mcs下载。

可以参考:

- 使用ISE iMPACT实现一键bit转mcs、bit文件下载、mcs文件下载