嵌入式分享合集41

一、STM32外部中断

本文用STM32CubeIDE软件实现STM32外部中断实例。 whaosoft aiot http://143ai.com

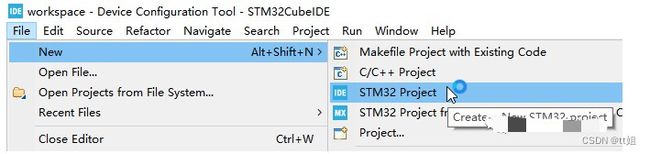

新建工程

“File”-“New”-“STM32 Project”。

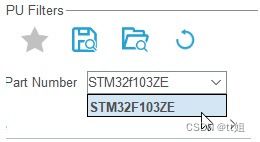

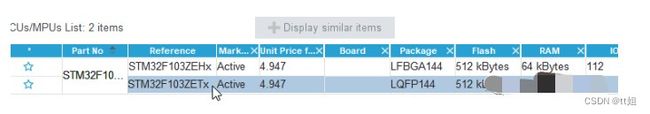

输入芯片型号STM32F103ZE。

选择相应封装,下一步。

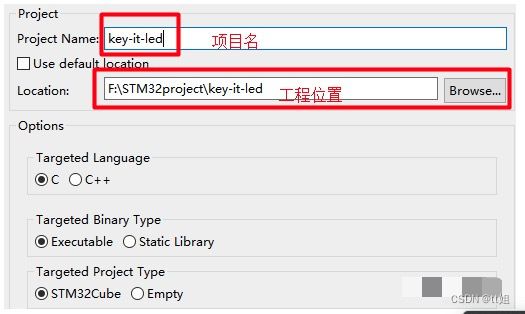

填写项目名,选择工程位置,下一步。

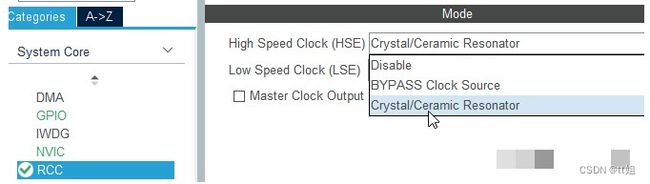

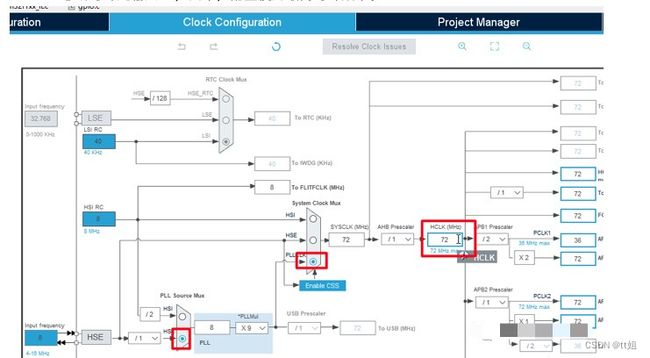

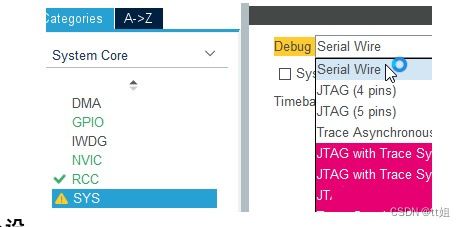

配置时钟、调试模式

选择高速外部时钟。

HCLK总线时钟处输入72,回车,配置使用最高时钟频率。

调试模式选择串行,方便下载程序。

配置管脚外设

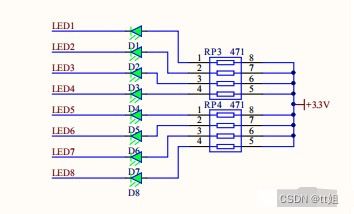

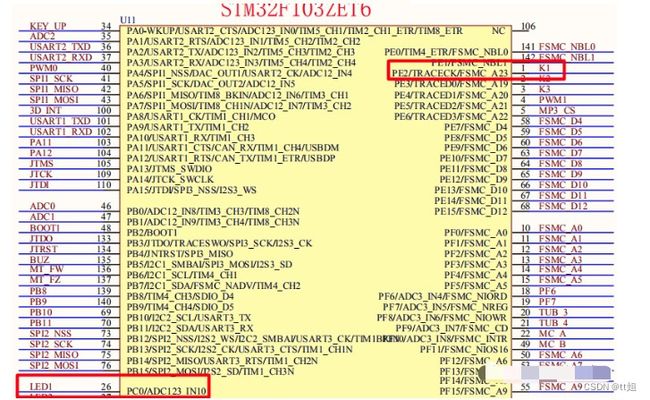

本实例中用到了LED1与KEY_LEFT,找到相应电路图。

![]()

可见LED1对应PC0管脚,低电平点亮。按键K1对应PE2管脚,低电平有效。

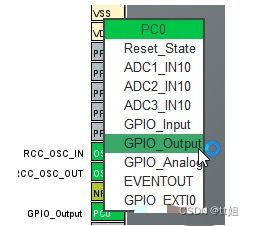

PC0配置为GPIO_Output,GPIO输出模式

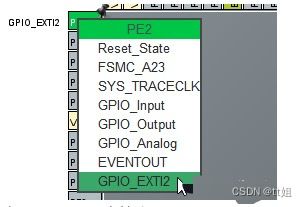

PE2配置为GPIO_EXTI2,GPIO中断线2。

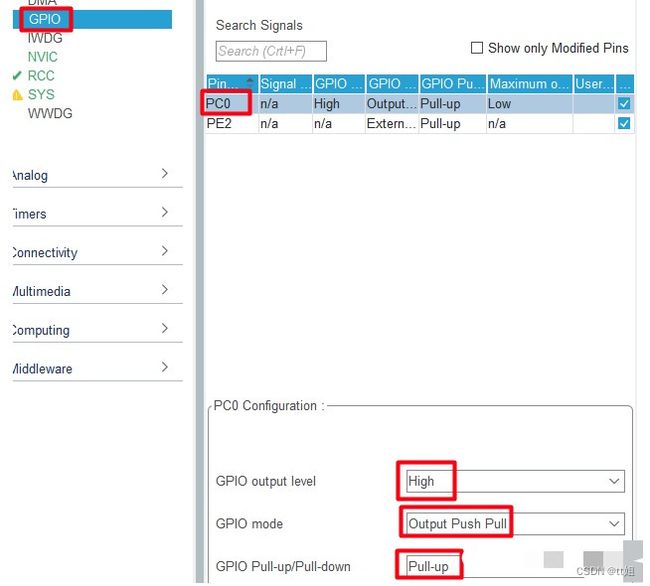

对GPIO进行配置,可以看到PC0、PE2两个管脚。

PC0管脚的配置:

-

GPIO输出电平,“High”,复位后高电平,LED1熄灭状态。

-

GPIO模式,“Output Push Pull”,推挽输出。

-

GPIO上拉下拉,“Pull-up”,上拉,默认高电平,避免管脚电平状态不稳定

-

PE2管脚的配置,GPIO模式这里有6个选项,分别是:

-

上升沿触发的外部中断

-

下降沿触发的外部中断

-

上升/下降沿触发的外部中断

-

上升沿触发的事件中断

-

下降沿触发的事件中断

-

上升/下降沿触发的事件中断

“外部中断”与“事件中断”的区别:

-

“事件中断”可以由硬件自动完成这个事件产生的结果,比如引起DMA操作、AD转换等,响应速度更快。

-

而本例中需要中断服务函数才能完成中断后产生的结果,是“外部中断”

由电路图可知,KEY1按键按下时为低电平,过程中会产生一个下降沿,所以选择“下降沿外部中断”这一项。

按键低电平有效,选择上拉,给管脚一个稳定的电平状态,不按下时为默认的高电平。

![]()

配置NVIC嵌套向量中断控制器

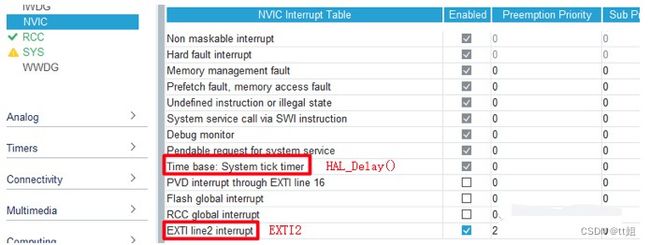

NVIC就是用来控制中断响应的,如下图列出了各个中断。可以分别配置其使能状态、抢占优先级与响应优先级。

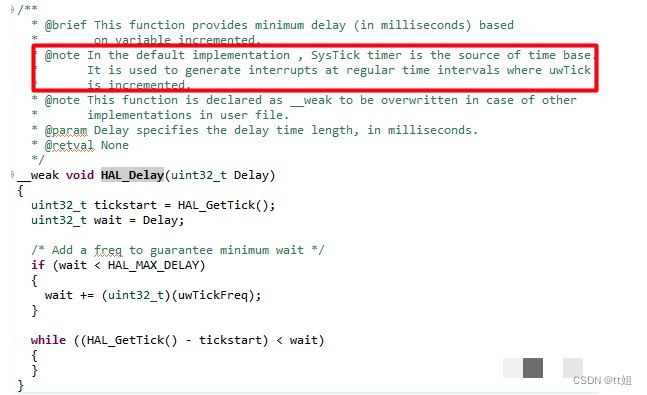

因为PE2配置为GPIO_EXTI2中断,它出现在了列表中。同时出现的还有SysTick,它是HAL_Delay的时基来源,如下图note处所说的,每隔一个固定时间产生一次中断。

因为下文中断服务函数代码中用到了HAL_Delay延时函数,把SysTick与EXTI2的抢占优先级分别设置为0与2。在这里,数值越大优先级越小。

配置中断服务函数

进行上述配置之后,点击生成代码。

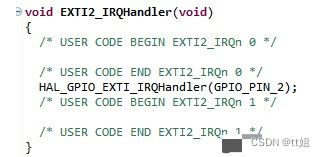

本实例中的中断类型是“外部中断”,通过中断服务函数来实现。

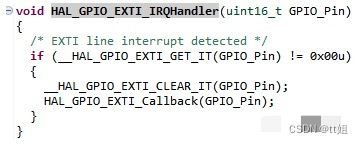

打开stm32f1xx_it.c文件,找到中断服务函数,它调用了GPIO中断服务函数。

F3找到这个函数的定义,在清除中断标志位后,进入了Callback回调函数。

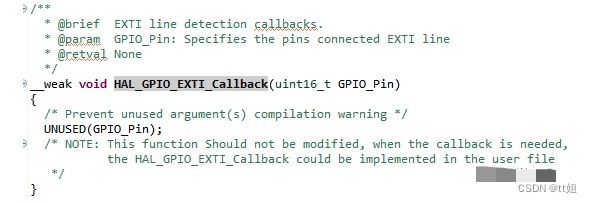

这个Callback函数也是一个弱化函数,,可以重写,如下图的__weak标识。

回到stm32f1xx_it.c文件,在末尾user code处写上中断发生时要实现的结果。

二、推挽、开漏、OC、OD

与推挽输出相对的是开漏输出,而开漏输出分为OC、OD两种,下文分别详细介绍。

推挽输出

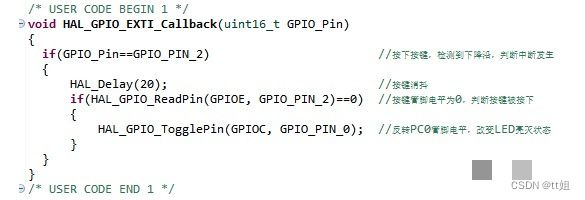

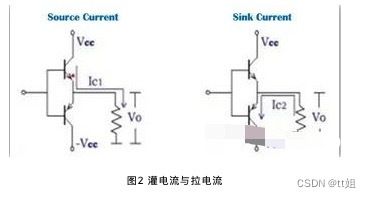

推挽输出(Push-Pull Output)是由两个MOS或者三极管受到互补控制信号的控制,两个管子始终处在一个导通另一个截止的状态,如图1所示:

推挽输出的最大特点是可以真正的输出高电平和低电平,而且在两种电平下都具有驱动能力。

补充说明:

所谓的驱动能力,就是指输出电流的能力。对于驱动大负载(即负载内阻越小,负载越大)时,例如IO输出为5V,驱动的负载内阻为10ohm,于是根据欧姆定律可以正常情况下负载上的电流为0.5A(推算出功率为2.5W)。显然一般的IO不可能有这么大的驱动能力,也就是没有办法输出这么大的电流。于是造成的结果就是输出电压会被拉下来,达不到标称的5V。当然如果只是数字信号的传递,下一级的输入阻抗理论上最好是高阻,也就是只需要传电压,基本没有电流,也就没有功率,于是就不需要很大的驱动能力。

对于推挽输出,输出高、低电平时电流的流向如图2所示。所以相比于后面介绍的开漏输出,输出高电平时的驱动能力强很多。

缺点

但推挽输出的一个缺点是,如果当两个推挽输出结构相连在一起,一个输出高电平,即上面的MOS导通,下面的MOS闭合时;同时另一个输出低电平,即上面的MOS闭合,下面的MOS导通时。电流会从第一个引脚的VCC通过上端MOS再经过第二个引脚的下端MOS直接流向GND。整个通路上电阻很小,会发生短路,进而可能造成端口的损害。这也是为什么推挽输出不能实现" 线与"的原因。

开漏输出

常说的与推挽输出相对的就是开漏输出(Open Drain Output),对于开漏输出和推挽输出的区别最普遍的说法就是开漏输出无法真正输出高电平,即高电平时没有驱动能力,需要借助外部上拉电阻完成对外驱动。

下面就从内部结构和原理上说明为什么开漏输出输出高电平时没有驱动能力,以及进一步比较与推挽输出的区别。

首先需要介绍一些开漏输出(OD)和开集输出(OC)。这两种输出的原理和特性基本是类似的,区别如下:

-

开漏使用MOS管,其中的"漏"指的就是MOS管的漏极

-

开集使用三极管,其中的"集"指的就是三极管的集电极

这两者其实都是和推挽输出相对应的输出模式,由于使用MOS管的情况较多,很多时候就用"开漏输出"这个词代替了开漏输出和开集输出。

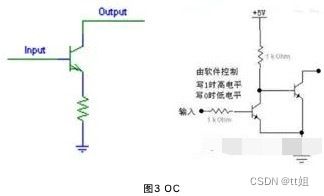

OC

介绍就先从开集输出开始,其原理电路结构如图3所示。

图3左边电路是开集(OC)输出最基本的电路,当输入为高电平时,NPN三极管导通,Output被拉到GND,输出为低电平;当输入为低电平时,NPN三极管闭合,Output相当于开路(输出高阻)。高电平时输出高阻(高阻、三态以及floating说的都是一个意思),此时对外没有任何的驱动能力。这就是开漏和开集输出最大的特点,如何利用该特点完成各种功能稍后介绍。这个电路虽然完成了开集输出的功能,但是会出现input为高,输出为低;input为低,输出为高的情况。

图3右边的电路中多使用了一个三极管完成了"反相"。当输入为高电平时,第一个三极管导通,此时第二个三极管的输入端会被拉到GND,于是第二个三极管闭合,输出高阻;当输入为低电平时,第一个三极管闭合,此时第二个三极管的输入端会被上拉电阻拉到高电平,于是第二个三极管导通,输出被拉到GND。这样,这个电路的输入与输出是同相的了。

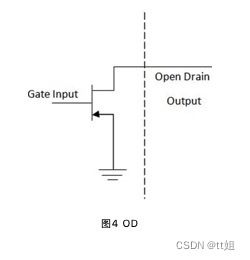

OD

接下来介绍开漏输出的电路,如图4所示。原理与开集输出基本相同,只是将三极管换成了MOS而已。

特点及应用

接着说说开漏、开集输出的特点以及应用,由于两者相似,后文中若无特殊说明,则用开漏表示开漏和开集两种输出电路。

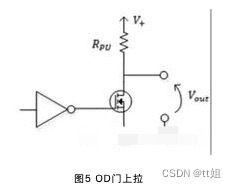

开漏输出最主要的特性就是高电平没有驱动能力,需要借助外部上拉电阻才能真正输出高电平,其电路如图5所示。

当MOS管闭合时,开漏输出电路输出高电平,且连接着负载时,电流流向是从外部电源,流经上拉电阻RPU,流进负载,最后进入GND。

-

开漏输出的这一特性一个明显的优势就是可以很方便的调节输出的电平,因为输出电平完全由上拉电阻连接的电源电平决定。所以在需要进行电平转换的地方,非常适合使用开漏输出。

-

开漏输出的这一特性另一个好处在于可以实现"线与"功能,所谓的"线与"指的是多个信号线直接连接在一起,只有当所有信号全部为高电平时,合在一起的总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平。而推挽输出就不行,如果高电平和低电平连在一起,会出现电流倒灌,损坏器件。

推挽、开漏对比

关于推挽输出、开漏输出在STM32中的应用。理清楚了推挽、开漏之后,可以更好的理解GPIO工作原理。

三、STM32中的上/下拉电阻

STM32中的GPIO

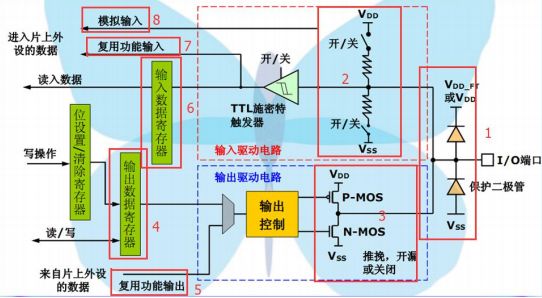

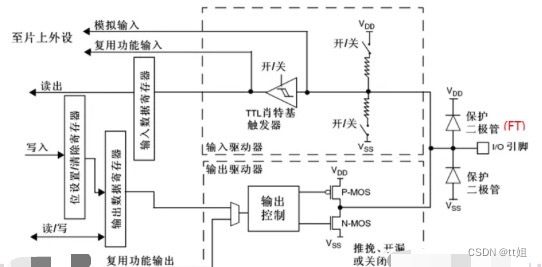

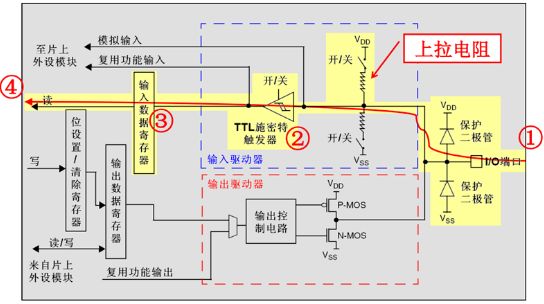

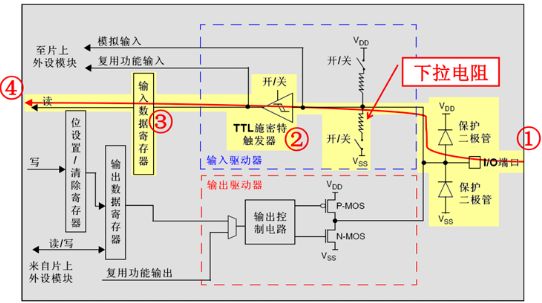

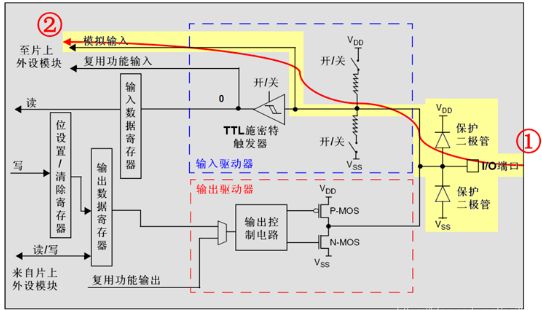

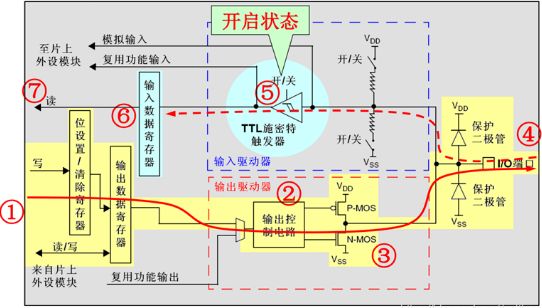

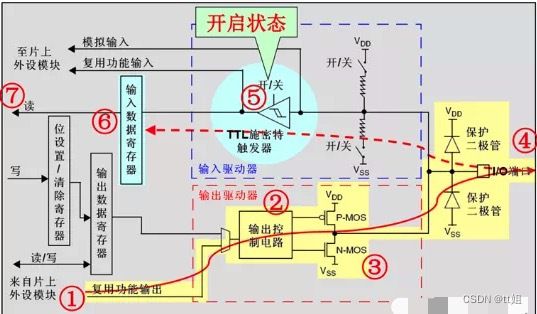

以STM32中的GPIO为例,如上图是GPIO的结构图。

从上图中标号2处可以看到,上拉和下拉电阻上都有一个开关,通过配置上下拉电阻开关,可以控制引脚的默认电平,这里有三种状态:

-

开启上拉时,引脚默认电压为高电平

-

开启下拉时,引脚默认电压为低电平

-

上拉和下拉不开启时,这种状态我们称为浮空模式

STM32上下拉及浮空模式的配置是通过GPIOx_CRL和GPIOx_CRH寄存器控制的,可以通过《STM32F1xx 中文参考手册》查阅。

开启上拉电阻或下拉电阻的作用

STM32内部的上拉其实是一个弱上拉,也就是说通过此上拉电阻输出的电流很小,如果想要输出一个大电流。那么就需要外接上拉电阻了,其实就是增加导线的输出电流。

下拉电阻情况相反,让STM32的CPU引脚输出低电平,结果由于后续电路影响输出的低电平达不到GND。所以接个下拉电阻,其实就是为了降低导线的输出电流。

另外当上下拉电阻都不开启,此时是浮空模式,引脚的电压是不确定的,此模式下的管脚电压会时不时改变。

所以为了防止引脚悬空,产生积累电荷、静电荷,造成电路不稳定。一般情况下,我们都会给引脚设置成上拉或者下拉模式,使它有一个确定的默认电平状态。

以上拉电阻举例,在STM32刚上电的时候,芯片引脚电平是不确定的。特别引脚是接按键的时候,必须给他个确定的电平。下拉电阻的作用就是,强制让电平保持在低电平。

上下拉电阻阻值的大小

根据拉电阻的阻值大小,可以分为强拉或弱拉(weak pull-up/down)。拉电阻阻值越小则表示电平能力越强,为强拉,可以抵抗外部噪声的能力也越强,相应的功耗也越大。

举个例子:

按键的上拉电阻可以选择3.3k、4.7k、5.1k、10k等,但是电阻越小,电流越大,功耗也越大。10k的上拉电阻带来的电流,是大多数芯片所能识别到的引脚电流,如果电阻太大,电流太小,引脚识别不了,所以10k是个折中的方案。这里的电流,简单来说是根据公式VDD/R拉电阻计算出来的。

四、GPIO工作原理详解

GPIO是通用输入/输出端口的简称,是STM32可控制的引脚。GPIO的引脚与外部硬件设备连接,可实现与外部通讯、控制外部硬件或者采集外部硬件数据的功能。

STM32F103ZET6芯片为144脚芯片,包括7个通用目的的输入/输出口(GPIO)组,分别为GPIOA、GPIOB、GPIOC、GPIOD、GPIOE、GPIOF、GPIOG,同时每组GPIO口组有16个GPIO口。通常简略称为PAx、PBx、PCx、PDx、PEx、PFx、PGx,其中x为0-15。

STM32的大部分引脚除了当GPIO使用之外,还可以复用为外设功能引脚(比如串口),这部分在【STM32】STM32端口复用和重映射(AFIO辅助功能时钟) 中有详细的介绍。

GPIO基本结构

每个GPIO内部都有这样的一个电路结构,这个结构在本文下面会具体介绍。

电路图分析

保护二极管:IO引脚上下两边两个二极管用于防止引脚外部过高、过低的电压输入。当引脚电压高于VDD时,上方的二极管导通;当引脚电压低于VSS时,下方的二极管导通,防止不正常电压引入芯片导致芯片烧毁。但是尽管如此,还是不能直接外接大功率器件,须加大功率及隔离电路驱动,防止烧坏芯片或者外接器件无法正常工作。

P-MOS管和N-MOS管:由P-MOS管和N-MOS管组成的单元电路使得GPIO具有“推挽输出”和“开漏输出”的模式。这里的电路会在下面很详细地分析到。

TTL肖特基触发器:信号经过触发器后,模拟信号转化为0和1的数字信号。但是,当GPIO引脚作为ADC采集电压的输入通道时,用其“模拟输入”功能,此时信号不再经过触发器进行TTL电平转换。ADC外设要采集到的原始的模拟信号。

这里需要注意的是,在查看《STM32中文参考手册V10》中的GPIO的表格时,会看到有“FT”一列,这代表着这个GPIO口时兼容3.3V和5V的;如果没有标注“FT”,就代表着不兼容5V。

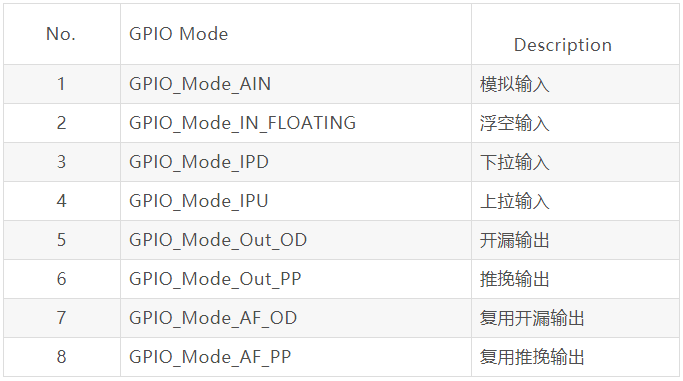

STM32的GPIO工作方式

GPIO支持4种输入模式(浮空输入、上拉输入、下拉输入、模拟输入)和4种输出模式(开漏输出、开漏复用输出、推挽输出、推挽复用输出)。同时,GPIO还支持三种最大翻转速度(2MHz、10MHz、50MHz)。每个I/O口可以自由编程,但I/O口寄存器必须按32位字被访问。

GPIO的八种工作方式

-

-

浮空输入模式(浮空输入模式下,I/O端口的电平信号直接进入输入数据寄存器。也就是说,I/O的电平状态是不确定的,完全由外部输入决定;如果在该引脚悬空(在无信号输入)的情况下,读取该端口的电平是不确定的。)

-

-

-

上拉输入模式(上拉输入模式下,I/O端口的电平信号直接进入输入数据寄存器。但是在I/O端口悬空(在无信号输入)的情况下,输入端的电平可以保持在高电平;并且在I/O端口输入为低电平的时候,输入端的电平也还是低电平。)

-

-

-

下拉输入模式(下拉输入模式下,I/O端口的电平信号直接进入输入数据寄存器。但是在I/O端口悬空(在无信号输入)的情况下,输入端的电平可以保持在低电平;并且在I/O端口输入为高电平的时候,输入端的电平也还是高电平。)

-

-

-

模拟输入模式(模拟输入模式下,I/O端口的模拟信号(电压信号,而非电平信号)直接模拟输入到片上外设模块,比如ADC模块等等。)

-

-

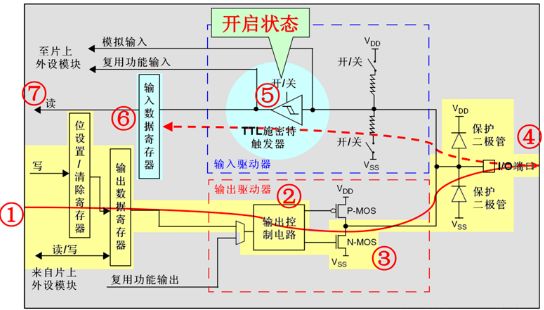

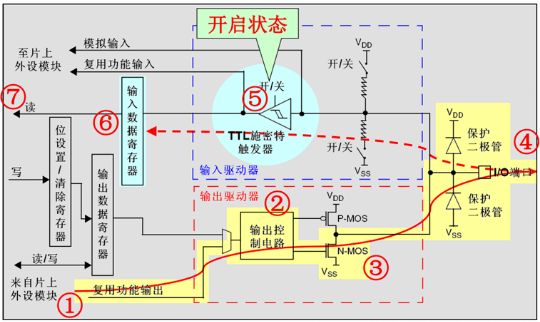

开漏输出模式(开漏输出模式下,通过设置位设置/清除寄存器或者输出数据寄存器的值,途经N-MOS管,最终输出到I/O端口。这里要注意N-MOS管,当设置输出的值为高电平的时候,N-MOS管处于关闭状态,此时I/O端口的电平就不会由输出的高低电平决定,而是由I/O端口外部的上拉或者下拉决定;当设置输出的值为低电平的时候,N-MOS管处于开启状态,此时I/O端口的电平就是低电平。同时,I/O端口的电平也可以通过输入电路进行读取;注意,I/O端口的电平不一定是输出的电平。)

-

开漏复用输出模式(开漏复用输出模式,与开漏输出模式很是类似。只是输出的高低电平的来源,不是让CPU直接写输出数据寄存器,取而代之利用片上外设模块的复用功能输出来决定的。)

-

推挽输出模式(推挽输出模式下,通过设置位设置/清除寄存器或者输出数据寄存器的值,途经P-MOS管和N-MOS管,最终输出到I/O端口。这里要注意P-MOS管和N-MOS管,当设置输出的值为高电平的时候,P-MOS管处于开启状态,N-MOS管处于关闭状态,此时I/O端口的电平就由P-MOS管决定:高电平;当设置输出的值为低电平的时候,P-MOS管处于关闭状态,N-MOS管处于开启状态,此时I/O端口的电平就由N-MOS管决定:低电平。同时,I/O端口的电平也可以通过输入电路进行读取;注意,此时I/O端口的电平一定是输出的电平。)

什么是推挽结构和推挽电路?

推挽结构一般是指两个参数相同的三极管或MOS管分别受两互补信号的控制,总是在一个三极管或MOS管导通的时候另一个截止。高低电平由输出电平决定。

推挽电路是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务。电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小、效率高。输出既可以向负载灌电流,也可以从负载抽取电流。推拉式输出级既提高电路的负载能力,又提高开关速度。

开漏输出和推挽输出的区别?

开漏输出:只可以输出强低电平,高电平得靠外部电阻拉高。输出端相当于三极管的集电极。适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内);

推挽输出:可以输出强高、低电平,连接数字器件。

关于推挽输出和开漏输出,最后用一幅最简单的图形来概括:

该图中左边的便是推挽输出模式,其中比较器输出高电平时下面的PNP三极管截止,而上面NPN三极管导通,输出电平VS+;当比较器输出低电平时则恰恰相反,PNP三极管导通,输出和地相连,为低电平。右边的则可以理解为开漏输出形式,需要接上拉。

STM32中的I/O模式

五、微分、积分电路的本质以及电容

很多朋友觉得PID是遥不可及,很神秘,很高大上的一种控制,对其控制原理也很模糊,只知晓概念性的层面,知其然不知其所以然,那么本期从另类视角来探究微分、积分电路的本质,意在帮助理解PID的控制原理。

PID:P表示比例控制;I表示积分控制;D表示微分控制。

在认清微分、积分电路之前,我们都知道电容的特性:电容的电流超前电压相位90°,很多教材都这么描述,让人很费解,其本质又是什么呢?

❤要彻底掌握微分、积分电路或PID控制思路,首先得了解电容。

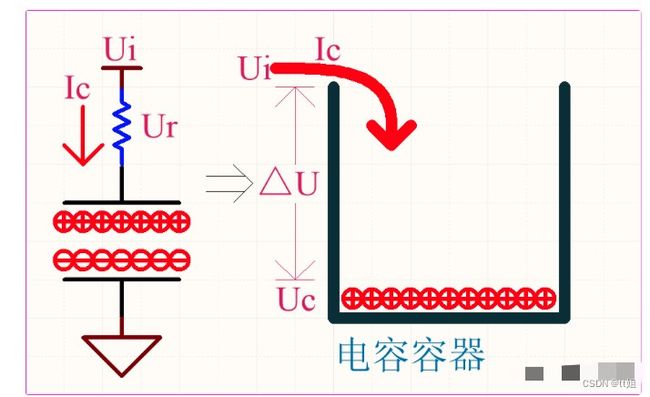

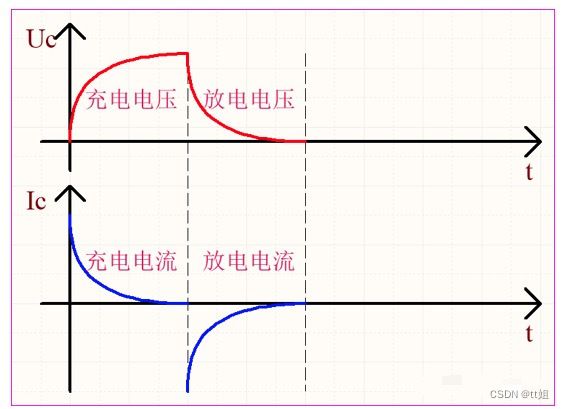

❤电容就是装载电荷的容器,从微观角度看,当电荷流入容器时,随着时间的变化极间电场逐渐增大;以图1为例:

①充电开始时Uc=0V,压差△U=Ur=Ui,此刻容器内无电荷,也就无电场排斥流入的电荷;所以电流Ic最大,表现为容抗最小,近似短路;

②当Uc上升,压差△U开始减小,该过程形成电场,容器开始排斥流入的电荷;电流Ic逐渐减小,表现为容抗逐渐增大;

③当Uc=Ui,压差△U=Ur=0V,此刻容器内电场最强,以最大排斥力阻止流入的电荷;电流Ic=0,表现为容抗最大,近似开路。

图1:电容容器充电模型

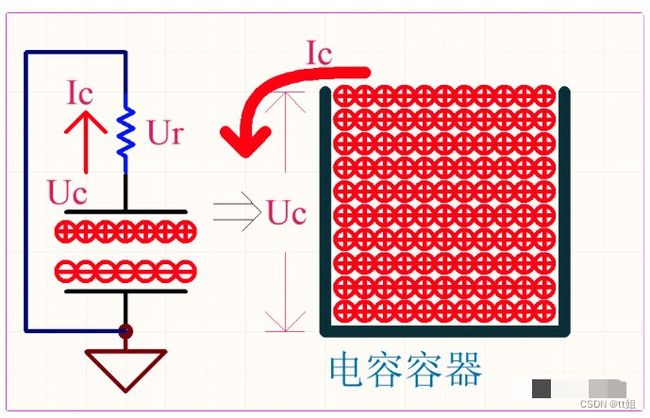

❤当电荷流出容器时,随着时间的变化极间电场逐渐减小;该放电过程的电容可看成是一个内阻为0的电压源,以图2为例(移除电源并接地):

①放电开始时Uc=Ui,此刻容器内充满电荷,因此电场最强,而电阻不变,则放电电流Ic最大(方向与充电相反),电阻两端的电压Ur=Uc,则Ur=Ui;

②当Uc下降,该过程电场减弱,放电电流Ic逐渐减小,Ur=Uc也逐渐减小;

③放电耗尽Uc=0V,此刻容器内无电荷,因此无电场,Ur=0V。

图2:电容容器放电模型

❤电容就好比水桶一样,流入的水流无论是大还是小,水位的变化一定是从最低位开始连续上升的;而电容内的电荷也是逐渐从0开始积累起来的,积累过程与自然常数e有关系,这里就不深入讨论了。

图3就是电容充放电的电压-电流曲线。

图3:电容充放电,电压-电流曲线

❤联系前面的分析,可总结为:

①电容电压不能突变,电流可突变(教材的定义是电容的电流与电压的变化率成正比);

②充电过程中的电容可等效成一个可变电阻,放电过程中的电容可等效成一个电压源;

③电容电流反映的是单位时间内流动的电荷量,电容电压(或电场)反映的是电荷量的多少。通俗的理解就是流动的电荷才会导致电荷量多少的变化(与①相吻合);用数学语言描述则是电容的电流超前电压相位90°;

④电容充放电速度与电容和电阻大小有关。

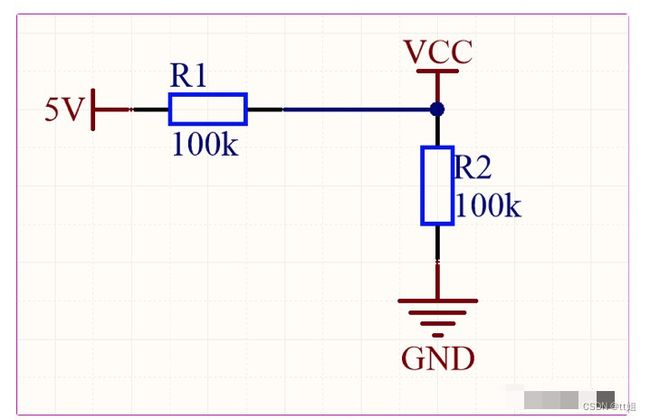

对电容充分了解之后,首先我们先来认识最简单的分压电路,如图4根据欧姆定律VCC=2.5V,该纯阻性的分压电路就是比例运算电路的雏形。

图4:分压电路

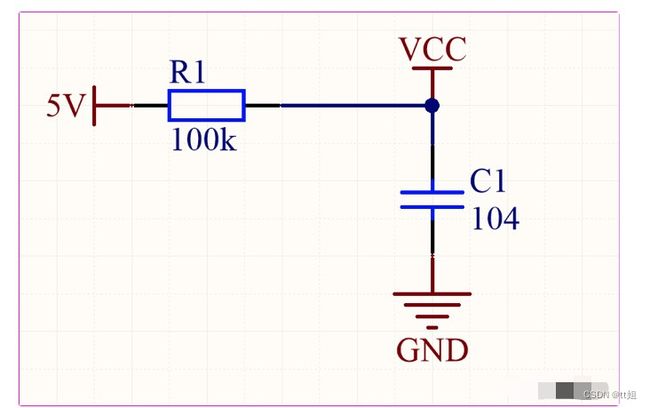

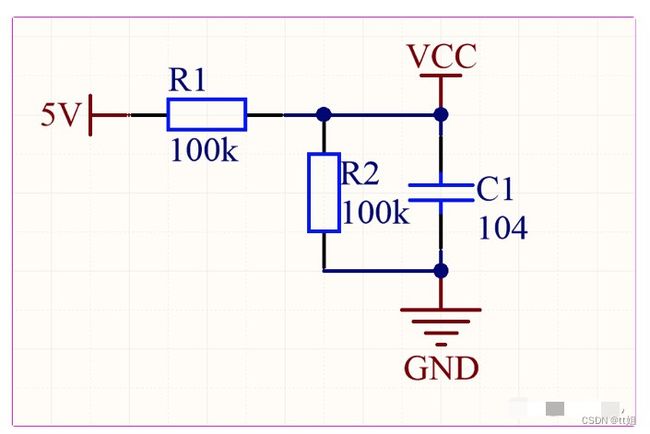

❤如图5,我们把R2换成104(0.1μF)电容,C1电容充满电后近似开路,VCC=5V;该电路就是积分运算电路的雏形。那么把5V改成信号源就构成了低通滤波电路。

图5:积分电路

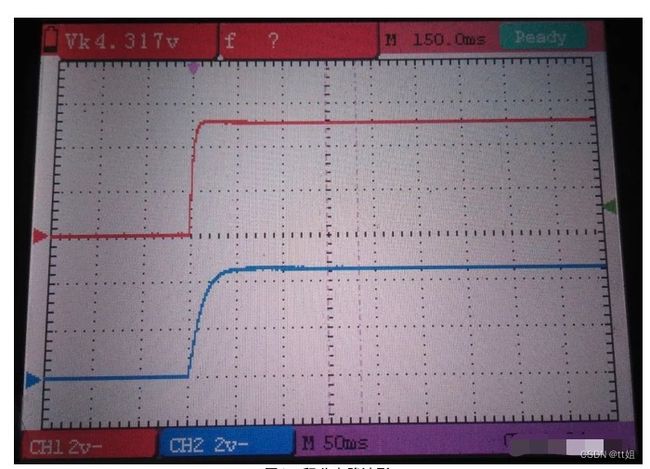

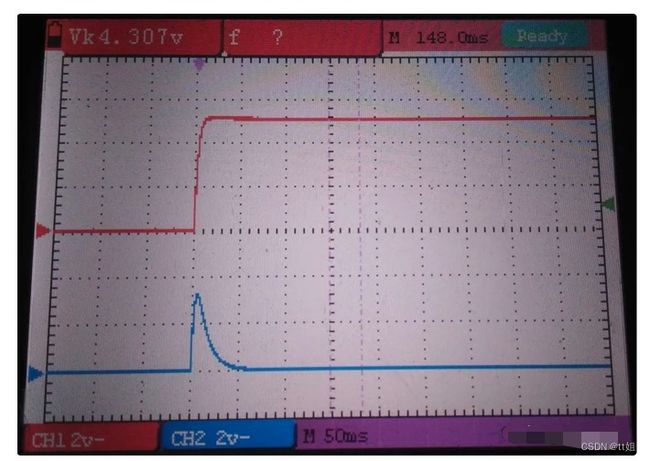

❤如图6为上图的充电波形,红色表示5V的波形,蓝色表示VCC的波形,因为电容充电时的容抗由小变大直至开路,所以分压VCC也由小变大直至为5V。而且电容充电需要一定的时间,导致VCC的波形要缓一些,该5V是开关电源上电软启动时的输出波形。

图6:积分电路波形

❤把图4图5组合就得到图7的电路,这就是我们经常使用的PI电路(比例积分),在参考电压或分压电路里很常见,加电容的目的就是增加延时性,稳定VCC的电压不受5V波动而波动,VCC=2.5V。

图7,:PI电路

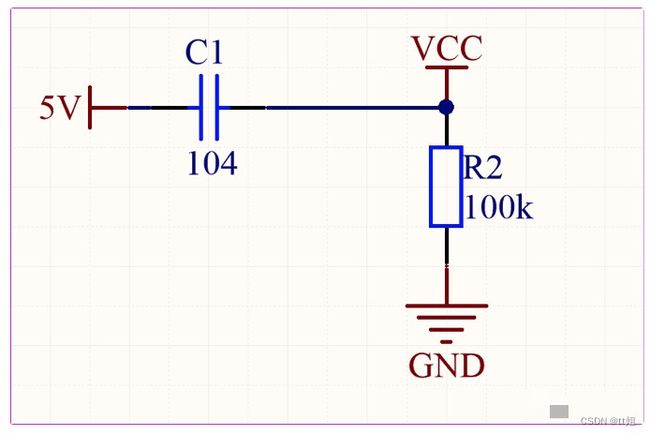

❤把图5中电容和电阻的位置交换一下得到如图8的电路,C1电容充满电后近似开路,VCC=0V;该电路就是微分运算电路的雏形。那么把5V改成信号源就构成了高通滤波电路。

图8:微分电路

❤如图9为上图的充电波形,红色表示5V的波形,蓝色表示VCC的波形,因为电容充电时的容抗由小变大直至开路,所以分压VCC由大变小直至为0V。也就是红色波形从0开始跳变一瞬间,VCC已经是最大值,所以微分有超前预判的性质(反映的是输入信号的变化率)。

图9:微分电路波形

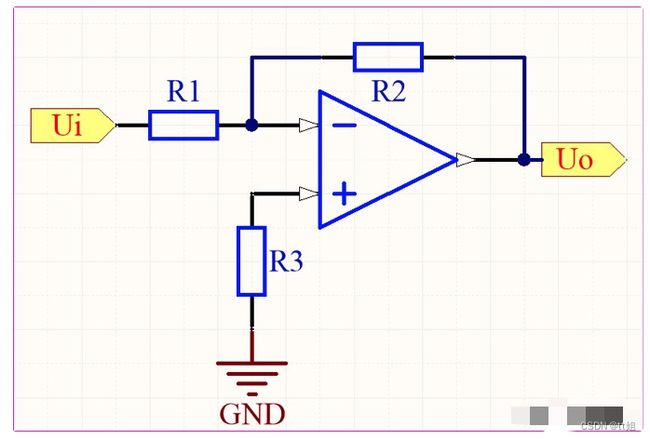

如图10为(反相)比例运算电路,关于运放的视频。

图10:比例运算电路

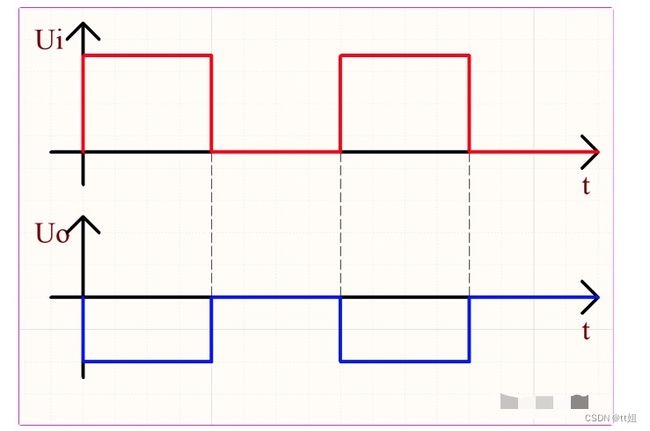

如图11,Uo与Ui成线性关系。

图11:比例运算电路波形

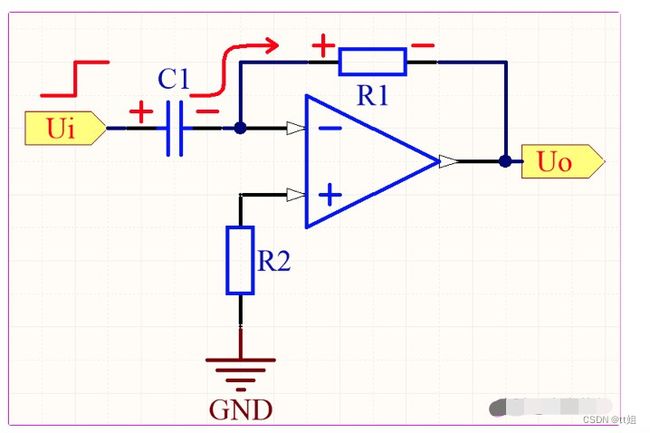

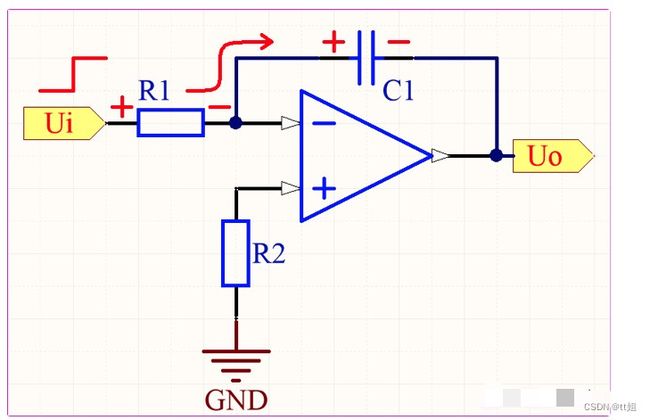

❤如图12、图13为微分运算电路的充放电过程:

充电过程的电容C1可等效成一个可变电阻,C1开始充电时的容抗为0,电压不可突变则电压为0,运放-输入端得到的分压为正最大峰值,于是Uo为运放的负最大峰值,随着电容充满电,U0逐渐变为0。

图12:微分运算电路-充电

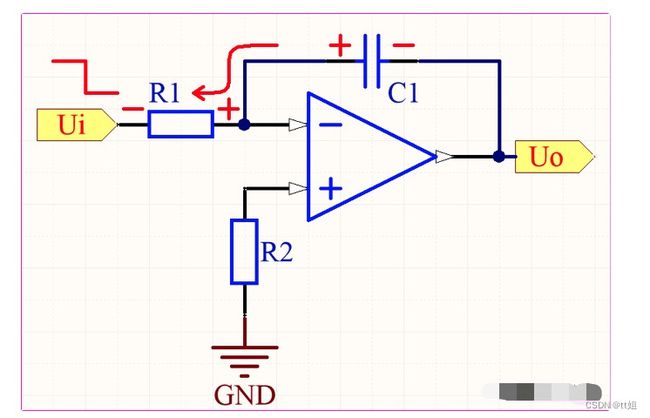

放电过程的电容C1可等效成一个电压源,且电压不可突变,此时电流反向为最大值,R1电压瞬间反向也为最大值,运放-输入端得到的分压则为负最大峰值,于是Uo为运放的正最大峰值,随着电容放完电,U0逐渐变为0。

图13:微分运算电路-放电

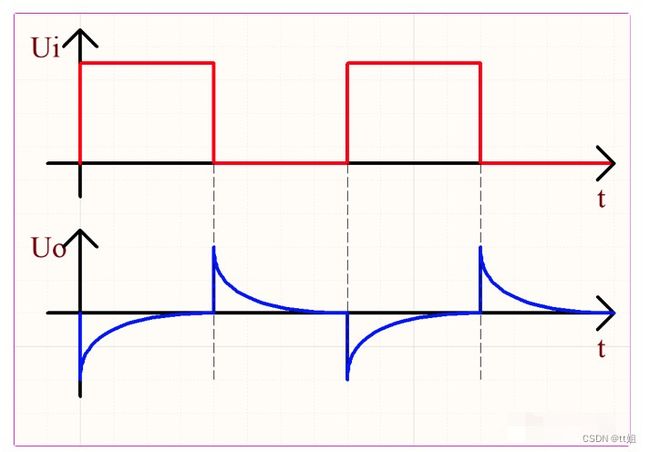

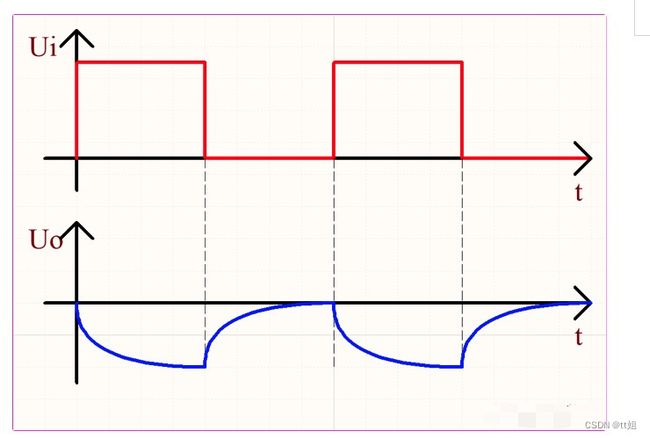

❤如图14为微分运算电路的输入输出波形,联系前面的分析结果,则Uo反映的是Ui的变化率,这样就达到了预判超前的效果。

图14:微分运算电路波形

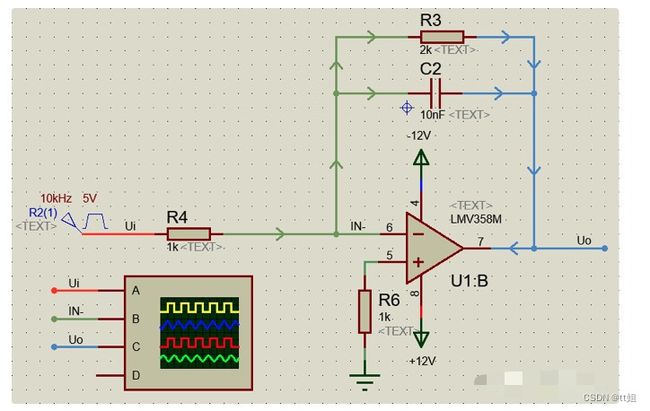

❤如图15为微分运算仿真电路,为了防止运放出现饱和,必须限制输入电流,实际使用时需要在电容C1输入端串联一个小电阻R2。串联电阻后的电路已经不是理想微分运算电路了,但是只要输入信号周期大于2倍RC常数,可以近似为微分运算电路。

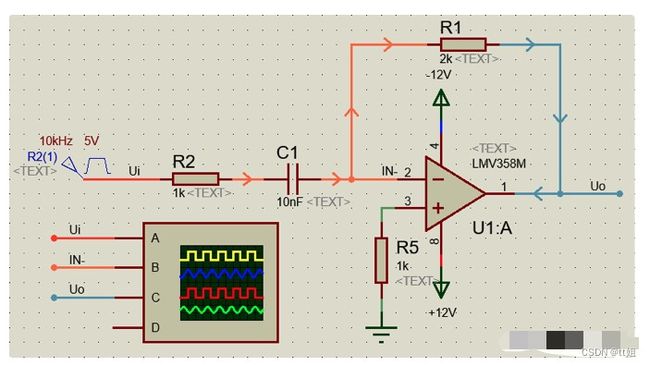

图15:微分运算仿真电路

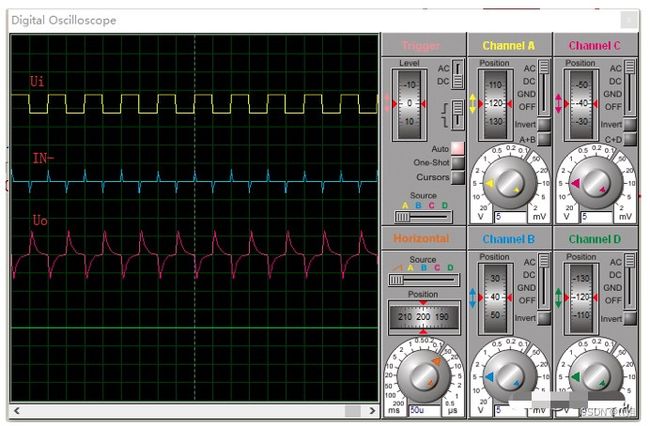

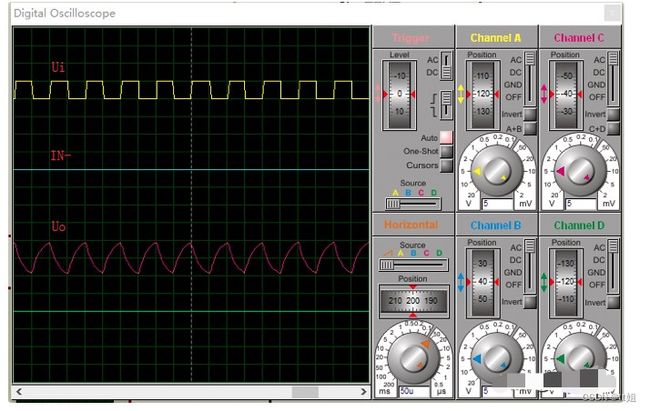

❤如图16为微分运算仿真电路波形,其中IN-为运放-输入端的波形。

图16:微分运算仿真电路波形

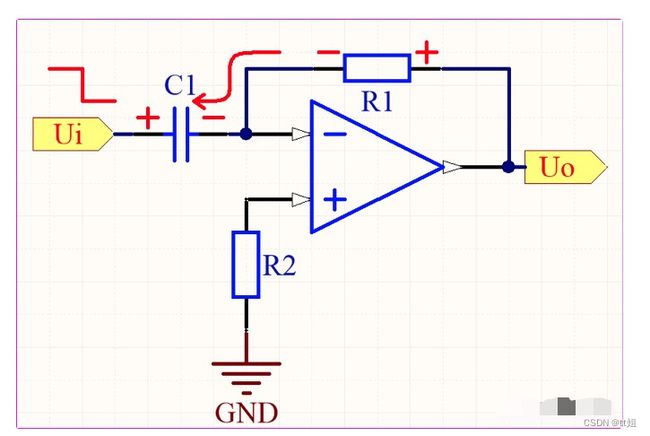

❤如图17、图18为积分运算电路的充放电过程:

充电过程的电容C1可等效成一个可变电阻,C1开始充电时的容抗为0,电压不可突变则电压为0,运放-输入端得到的分压为0,于是Uo为0,随着电容充满电,运放-输入端得到的分压为正最大值,U0为运放的负最大峰值。

图15:积分运算电路-充电

放电过程的电容C1可等效成一个电压源,且电压不可突变,运放-输入端得到的分压也不可突变,随着电容放完电,于是Uo由负最大峰值逐渐变为0。

图16:积分运算电路-放电

❤如图17为积分运算电路的输入输出波形,联系前面的分析结果,则Uo反映的是Ui的积累过程,这样就达到了延迟稳定的效果。

图17:积分运算电路波形

❤如图18为积分运算仿真电路,为了防止运放出现饱和,实际使用时需要在电容C2两端并联一个电阻R3。并联电阻后的电路已经不是理想积分运算电路了,但是只要输入信号周期大于2倍RC常数,可以近似为积分运算电路。

图18:积分运算仿真电路

❤如图19为积分运算仿真电路波形,其中IN-为运放-输入端的波形。

图19:积分运算仿真电路波形

❤要点:

①微分、积分运算电路利用了电容充放电时其电压不可突变的特性达到调节输出的目的,对变化的输入信号有意义;

②微分D控制有超前预判的特性,积分I控制有延迟稳定的特性,在PID调节速度上,微分D控制>比例P控制>积分I控制。