《计算机体系结构:量化研究方法》读书笔记

Lecture 1: Quantitative Approach

1.计算机体系结构与计算机组成原理有什么区别?

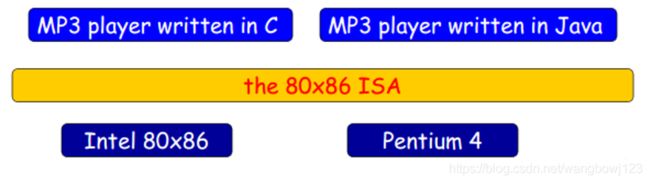

计算机的实现包括两个方面:组成和硬件。组成一词包含了计算机设计的高阶内容,例如存储器系统,存储器互连,设计内部处理器 CPU (中央处理器——算术、逻辑、分支和数据传送功能都在内部实现)。有时也用微体系结构一词来代替“组成”。例如AMD Operon和Intel Core I7是两个指令集体系结构相同但组成不同的处理器。这两种处理器都实现X86指令集,但它们的流水线和缓存组成有很大的不同。硬件指的是一个计算机的具体实现,包括计算机的详尽逻辑设计和封装技术。

真正的体系结构涵盖了计算机设计的所有三个方面:指令集体系结构、组成或微体系结构、硬件。计算机架构师设计的计算机必须满足功能需求,并达到价格、功耗、性能和可用性指标。

2.现如今的芯片设计趋势或者现状是怎样的?

功率是现如今使用晶体管的主要限制,通过降低电压可以大幅度降低动态功率和能耗,二十年来,电压已经从最初的5V降低到1V以下,然而如果不能降低电压或提高每个芯片的功率,那可能就要减缓时钟频率的增长速度,这也是从2003年以来的主要趋势。

3.怎样设计出低成本的集成电路?

虽然集成电路的成本以指数形式下降,但基本的硅制造工艺没有变化:仍需要对晶圆进行测试,切割成晶片进行封装。对于计算机设计人员来讲,由于制造工艺决定了晶圆的成本、晶圆成品率和单位面积上的缺陷数,设计人员唯一可控的就是晶片面积。

4.如何对计算机的性能进行评估?

使用量化的研究方法,从计算机的响应时间、执行时间、吞吐量来进行综合评估。

主要通过基准测试来对计算机进行性能的测试与度量,包括:桌面基准测试、服务器基准测试。要注意SPEC基准测试集,是一个使用相当广泛的测试集。

5.如何理解程序局部性?

局部性原理指的是程序常常重复使用它们最近使用过的数据和指令。有一条广泛使用的经验规律:一个程序90%的执行时间花费在仅10%的代码中。充分利用时间局部性和空间局部性可以优化程序的执行时间。

处理器中指令的提取与译码器的使用可能比乘法器要繁琐的多,所以应该优先对其进行优化。

6.设计多核芯片的意义何在?

2005年以来,之所以转向一芯多核,并不是因为取得了什么重大突破,显著简化了并行编程方式。而是因为ILP(指令级并行)壁垒和功率壁垒的存在存在而别无选择。在一个芯片中设计多个处理器并不能保证功率较低。而的确有可能设计一种消耗更高功率的多核芯片。其潜力仅仅在于能够用几个低时钟频率的高效核心代替高时钟频率的低效核心,从而有可能提高整体效率。因此多核处理器并不是万能的。

First Microprocessor Intel 4004, 1971

7.Amdahl 定理有何作用?

利用Amdahl 定理可以计算出通过改进计算机某一部分而能获得的性能增益。

Lecture 2: Instruction Set Principles

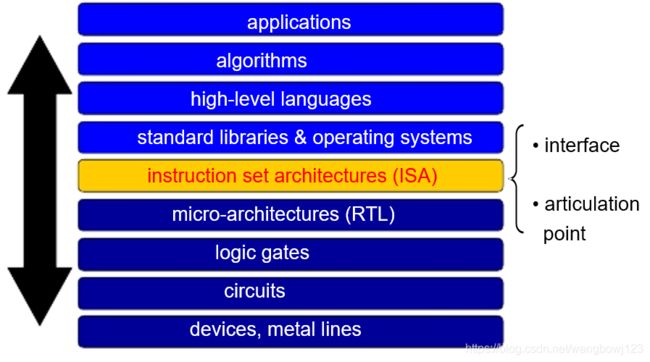

指令集架构(Instruction Set Architecture, ISA)-汇编语言程序员或编译器编写者可见

ISA包括:

- 1.编程寄存器

- 2.操作数访问

- 2.操作数的类型和大小

- 4.指令集

- 5.寻址模式

- 6.指令编码

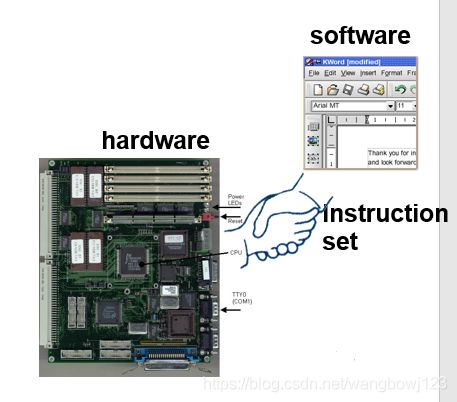

ISA 是硬件与软件之间的连接点。任何在内存里执行的程序都将通过 ISA 进行解耦从而能在底层架构上执行。

算术运算指令的执行主要分为以下几种:

- Stack type:操作数隐含在栈顶指针

- R-R type:操作数都在寄存器中

- R-AC type:一个操作数隐含在 AC 计数器中

- R-M type:需要访存操作去取操作数

Lecture 3: Memory Hierarchy Design

动机:

时间局部性(temporal locality)

被引用过一次的存储器位置在未来会被多次引用(通常在循环中)。

空间局部性(spatial locality)

如果一个存储器的位置被引用,那么将来他附近的位置也会被引用。

正是由于局部性原理的存在和“在给定实现技术和功率预算的情况下,硬件越小,速度可以越快”的准则,存储器体系结构便运营而生。

有学生可能会问,为什么需要多层次的存储结构,使用一个理论上无限大的存储器去完成一些工作不就可以了么?这样表面上是可以的,但是我们没有办法立刻马上从这样一个十分庞大的存储器中得到我们想要的机器字。我们不得不去构建分层的结构存储器,每一层的容量都要大于前一层,但访问速度也要慢一些。

当前的一大趋势:存储器性能和处理器性能之间的差距越来越大。

优化缓存性能的高级方法:

1.使用小而简单的第一级缓存,用来缩短命中时间、降低功率。

大容量L1缓存会给时钟频率带来影响,所以近来L1缓存大小的涨幅很小。近些年来,L1缓存中使用了较高的相联度,容易知道,直接映射的命中时间略快于两路组相联,而近些年来处理器在访问缓存时至少需要两个时钟周期,因此命中时间较长不会带来太大影响。

2.采用路预测以缩短命中时间。

路预测指的是在缓存中另外保存了一些位,用于预测下一次缓存访问组中的路和块。实验表明,对I-缓存的准确度要优于对D-缓存的准确度(这也符合常理)。

3.实现缓存访问的流水化、以提高缓存带宽

这个方法没有看懂

4.采用无阻塞缓存,以提高带宽

允许“缺失时仍然命中”甚至“多次缺失仍然命中”。

5.采用多组缓存以提高缓存带宽

6.关键字优先和提前重启动以降低缺失代价

7.合并写缓冲区以降低缺失代价

将缺失数据地址与写缓冲区中的有效项目进行对比,如果匹配,则将新数据与这个项目合并在一起,称为写合并。

8.采用编译器优化来降低缺失率

这种方法应用的较为广泛,尤其是在循环优化之中。

着重讲一下循环分块:

分块技术的目的是在缓存中载入的数据被替换之前,在最大限度上利用它。

for (int i = 0; i < N; ++i)

for (int j = 0; j < N; ++j)

{

r = 0;

for (int k = 0; k < N; ++k)

r = r + y[i][k] * z[k][j];

x[i][j] = r;

}

循环分块技术可以简单的看作是将两层循环变为四重循环,表面上增加了时间复杂度,实则是提高了缓存的命中率,分块后的代码如下:

for (int jj = 0; i < N; jj = jj + B)

for (int kk = 0; j < N; kk = kk + B)

for (int i = 0; i < N; i = i + 1)

for (int j = 0; j < min(jj + B, N); j = j + 1)

{

r = 0;

for (int k = 0; k < min(kk + B, N); k = k + 1)

r = r + y[i][k] * z[k][j];

x[i][j] = x[i][j] + r;

}

B 被称作分块因子,这样的循环优化技术在深度学习硬件加速器中的应用十分广泛,很多新型的架构都是基于这样的技术设计的。

如何最直观的理解分块原理?

可以从原始代码中看出来,对数组 z 的访问步长较大,对数组 x 的访问并不那么频繁且按列访问,在内部的两层循环中可以达到 NN 次,如果缓存大小较大,能够装下所有的x、y、z三个 NN 数组,那么并不存在什么问题,但是如果缓存较小,显然缺失率会较大。

解决方法就是对数组的访问步长进行限制,改为计算一个大小为 B*B 的子矩阵。