HDLbits exercises 11(COUNTERS全部题)

目录

1\ FOUR-BIT BINARY COUNTER

2\ DECADE COUNTER

3\ DECADE COUNTER AGAIN

4\ SLOW DECADE COUNTER

5\ COUNTER 1-12

6\ COUNTER 1000

7\ 4-DIGIT DECIMAL COUNTER

8\ 12-HOUR CLOCK(有难度,可适当放弃!!!)

1\ FOUR-BIT BINARY COUNTER

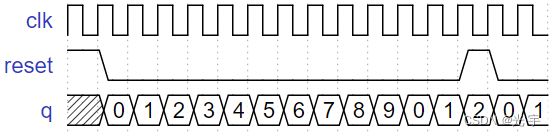

Build a 4-bit binary counter that counts from 0 through 15, inclusive, with a period of 16. The reset input is synchronous(同步的), and should reset the counter to 0.

ERRO:

module top_module (

input clk,

input reset, // Synchronous active-high reset

output reg [3:0] q);

assign q=4'b0000;

always @(posedge clk)

begin

if(reset)

q<=4'b0;

else

q<=q+1'b1;

end

endmodule

HINT:

当本题如“ERRO”所示编写时,会报以下错误:

Can't resolve multiple constant drivers for net "q[3]" at top_module.v(5) File: /home/h/work/hdlbits.7861578/top_module.v Line: 5

这个错误的原因就在于:在不同的always逻辑块中,对同一个reg变量进行了赋值,在多个alwasy逻辑块同时并行工作的时候,会出现冲突。

其解决方法就是将外面的assign语句删掉。

CORRECT:

module top_module (

input clk,

input reset, // Synchronous active-high reset

output reg [3:0] q);

always @(posedge clk)

begin

if(reset)

q<=4'b0; //q<=0;

else

q<=q+1'b1; //q<=q+1;

end

endmodule

2\ DECADE COUNTER

Build a decade counter that counts from 0 through 9, inclusive, with a period of 10. The reset input is synchronous, and should reset the counter to 0.

CORRECT:

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always @(posedge clk)

begin

if(reset) // if(reset || q==9)

q<=4'd0;

else if(q==4'd9)

q<=4'd0;

else

q<=q+1'd1;

end

endmodule

3\ DECADE COUNTER AGAIN

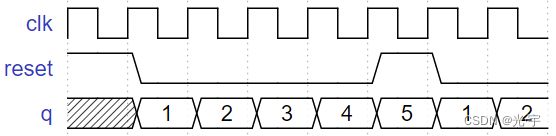

Make a decade counter that counts 1 through 10, inclusive. The reset input is synchronous, and should reset the counter to 1.

CORRECT:

module top_module (

input clk,

input reset,

output [3:0] q);

always@(posedge clk)

begin

if(reset || q==10)

q<=1;

else

q<=q+1;

end

endmodule

4\ SLOW DECADE COUNTER

Build a decade counter that counts from 0 through 9, inclusive, with a period of 10. The reset input is synchronous, and should reset the counter to 0.

We want to be able to pause the counter rather than always incrementing every clock cycle, so the slowena input indicates when the counter should increment(增长).

CORRECT:

module top_module (

input clk,

input slowena,

input reset,

output [3:0] q);

always@(posedge clk)

begin

if(reset)

q<=0;

else if(slowena)

if(q==9)

q<=0;

else

q<=q+1;

end

endmodule

HINT:

谁控制累加就把判断9写谁里面。

5\ COUNTER 1-12

Design a 1-12 counter with the following inputs and outputs:

- Reset Synchronous active-high reset that forces the counter to 1

- Enable Set high for the counter to run

- Clk Positive edge-triggered clock input

- Q[3:0] The output of the counter

- c_enable, c_load, c_d[3:0] Control signals going to the provided 4-bit counter, so correct operation can be verified.

You have the following components available:

- the 4-bit binary counter (count4) below, which has Enable and synchronous parallel-load inputs (load has higher priority than enable). The count4 module is provided to you. Instantiate it in your circuit.

- logic gates

module count4( input clk, input enable, input load, input [3:0] d, output reg [3:0] Q );

The c_enable, c_load, and c_d outputs are the signals that go to the internal counter's enable, load, and d inputs, respectively. Their purpose is to allow these signals to be checked for correctness.

HINT:

c_enable应与计时器的使能信号一致;

c_load信号判断是否需要复位,复位有两种情况:reset=1和记到12了;

c_d是输入的置位,应设为1,因为计数从1到12.

CORRECT:

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

);

assign c_enable = enable;

assign c_load = reset | ((Q == 4'd12) && (enable == 1'b1));

assign c_d = c_load ? 4'd1 : 4'd0;

count4 the_counter (clk, c_enable, c_load, c_d , Q);

endmodule

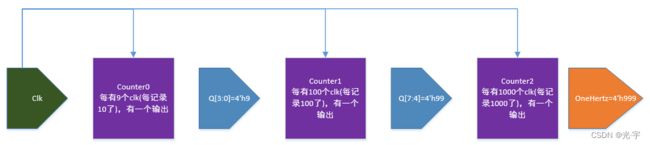

6\ COUNTER 1000

From a 1000 Hz clock, derive a 1 Hz signal, called OneHertz, that could be used to drive an Enable signal for a set of hour/minute/second counters to create a digital wall clock. Since we want the clock to count once per second, the OneHertz signal must be asserted for exactly one cycle each second. Build the frequency divider using modulo-10 (BCD) counters and as few other gates as possible. Also output the enable signals from each of the BCD counters you use (c_enable[0] for the fastest counter, c_enable[2] for the slowest).

(从一个1000hz的时钟,派生一个1hz的信号,称为OneHertz,它可以用于驱动一组小时/分钟/秒计数器的Enable信号,以创建一个数字挂钟。因为我们希望时钟每秒计算一次,所以OneHertz信号必须每秒精确地断言一个周期。使用模10 (BCD)计数器和尽可能少的其他门来构建分频器。还要从您使用的每个BCD计数器输出启用信号(c_enable[0]用于最快的计数器,c_enable[2]用于最慢的计数器)。)

The following BCD counter is provided for you. Enable must be high for the counter to run. Reset is synchronous and set high to force the counter to zero. All counters in your circuit must directly use the same 1000 Hz signal.

(以下BCD计数器为您提供。Enable值必须高,计数器才能运行。复位是同步的,设置高可以强制计数器归零。电路中的所有计数器必须直接使用相同的1000hz信号。)

module bcdcount ( input clk, input reset, input enable, output reg [3:0] Q );

HINT:

CORRECT:

module top_module (

input clk,

input reset,

output OneHertz,

output [2:0] c_enable

);

wire [11:0] Q;

assign c_enable[0]=1'b1;

assign c_enable[1]=(Q[3:0] == 4'h9);

assign c_enable[2]=(Q[7:0] == 8'h99);

assign OneHertz = (Q[11:0] == 12'h999);

bcdcount counter0 (clk, reset, c_enable[0],Q[3:0]);

bcdcount counter1 (clk, reset, c_enable[1],Q[7:4]);

bcdcount counter2 (clk, reset, c_enable[2],Q[11:8]);

endmodule

7\ 4-DIGIT DECIMAL COUNTER

Build a 4-digit BCD (binary-coded decimal) counter. Each decimal digit is encoded using 4 bits: q[3:0] is the ones digit, q[7:4] is the tens digit, etc. For digits [3:1], also output an enable signal indicating when each of the upper three digits should be incremented.

You may want to instantiate or modify some one-digit decade counters.

(建立一个4位BCD(二进制编码的十进制)计数器。每个十进制数字都使用4位进行编码:q[3:0]是个位,q[7:4]是十位,等等。对于数字[3:1],也输出一个使能信号,指示何时上三位数字都应该增加。您可能想实例化或修改一些十位数计数器。)

CORRECT:

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

assign ena[1]=(q[3:0]==4'h9);

assign ena[2]=(q[7:0]==8'h99);

assign ena[3]=(q[11:0]==12'h999);

BCDcounter insta0(clk,reset,1'h1,q[3:0]);

BCDcounter insta1(clk,reset,ena[1],q[7:4]);

BCDcounter insta2(clk,reset,ena[2],q[11:8]);

BCDcounter insta3(clk,reset,ena[3],q[15:12]);

endmodule

module BCDcounter(

input clk,

input reset,

input ena,

output [3:0] count

);

always@(posedge clk)

begin

if(reset)

count<=0;

else if(ena)

count<=(count==9)? 0 : count+1;

else

count<=count;

end

endmodule

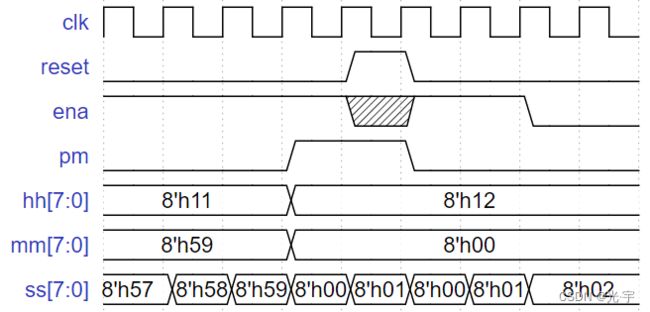

8\ 12-HOUR CLOCK(有难度,可适当放弃!!!)

Create a set of counters suitable for use as a 12-hour clock (with am/pm indicator). Your counters are clocked by a fast-running clk, with a pulse on ena whenever your clock should increment (i.e., once per second).

reset resets the clock to 12:00 AM. pm is 0 for AM and 1 for PM. hh, mm, and ss are two BCD (Binary-Coded Decimal) digits each for hours (01-12), minutes (00-59), and seconds (00-59). Reset has higher priority than enable, and can occur even when not enabled.

(创建一组适合作为12小时时钟使用的计数器(带上午/下午指示)。你的计数器由一个快速运行的时钟计时,当你的时钟应该增加时(例如,每秒一次),ena就会有一个脉冲。

reset:将时钟重置到上午12点。pm对AM是0,对pm是1。hh、mm、ss为BCD (Binary-Coded Decimal)两位,分别代表小时(01-12)、分钟(00-59)、秒(00-59)。Reset的优先级高于enable,甚至在未启用时也会发生。)

The following timing diagram shows the rollover behaviour from 11:59:59 AM to 12:00:00 PM and the synchronous reset and enable behaviour.

(下面的计时图显示了从11:59:59 AM到12:00:00 PM的翻转行为以及同步重置和启用行为。)

HINT:

其中,“11:59:59 PM”提前到“12:00:00 AM”,“12:59:59 PM”提前到“01:00:00 PM”。没有00:00:00。

CORRECT:

module top_module(

input clk,

input reset,

input ena,

output pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

wire [6:1] enable;

wire [7:0] hh_r;

assign enable[1]=ena && (ss[3:0]==4'h9);

assign enable[2]=enable[1] && (ss[7:4]==4'h5);

assign enable[3]=enable[2] && (mm[3:0]==4'h9);

assign enable[4]=enable[3] && (mm[7:4]==4'h5);

assign enable[5]=enable[4] && (hh_r[3:0]==4'hb);//11

assign enable[6]=enable[5] && (hh_r[7:4]==4'h1);

BCDcounter #(.start(4'h0),.End(4'h9)) second9(clk,reset,ena,ss[3:0]);

BCDcounter #(.start(4'h0),.End(4'h5)) second5(clk,reset,enable[1],ss[7:4]);

BCDcounter #(.start(4'h0),.End(4'h9)) minute9(clk,reset,enable[2],mm[3:0]);

BCDcounter #(.start(4'h0),.End(4'h5)) minute5(clk,reset,enable[3],mm[7:4]);

BCDcounter #(.start(4'h0),.End(4'hb)) hourb(clk,reset,enable[4],hh_r[3:0]);

BCDcounter #(.start(4'h0),.End(4'h1)) hour1(clk,reset,enable[5],hh_r[7:4]);

assign pm=(hh_r[7:4]==4'h1);

assign hh=(hh_r[3:0]==4'h0)?8'h12:((hh_r[3:0]>4'h9)?{4'h1,hh_r[3:0]-4'ha}:{4'h0,hh_r[3:0]});

endmodule

module BCDcounter(

input clk,

input reset,

input ena,

output reg [3:0] count

);

parameter start=4'h0,End=4'h9;

always@(posedge clk)

begin

if(reset)

count<=start;

else if(ena)

count<=(count==End)? start : count+1;

else

count<=count;

end

endmodule