Autosar MCAL MCU配置时钟-基于cfg

文章目录

- 前言

- MCU时钟配置

-

- cfg配置外部晶振

- CCU

- 时钟源的选择

-

- OSC(Oscillator Circuit)

-

- OSC的模式:

-

- 外部输入时钟模式:

- 外部晶体/陶瓷谐振模式

- Back up时钟源

- Clock generation时钟生成

-

- 输入时钟

- cfg中配置使用PLL

- PLL模式

-

- cfg中配置模式:

- Normal Mode

- Prescaler Mode

- Freerunning Mode

- PLL模式配置

-

- 配置为自由运行模式:

- 配置为Prescaler Mode

- 配置为Normal Mode

- cfg配置fpll频率:

- 配置分频参数N,P,K1-3

-

- cfg配置分频参数N,P,K1-3

- 实际计算例子:

- Frequency Modulation频率调制

-

- cfg中配置允许PLL调制:

- cfg中配置调制幅度%:

- Clock Distribution时钟分配

-

- Clock Divider Limitations

- 配置外设时钟分频参数

-

- cfg中配置分频参数

- cfg中配置频率,校验用

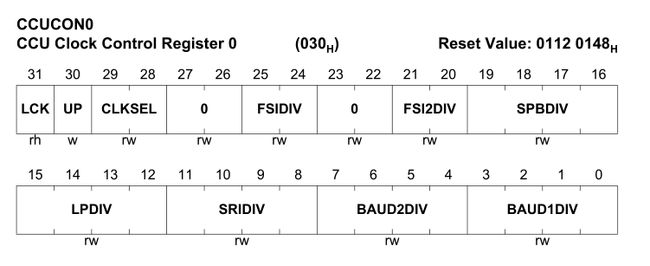

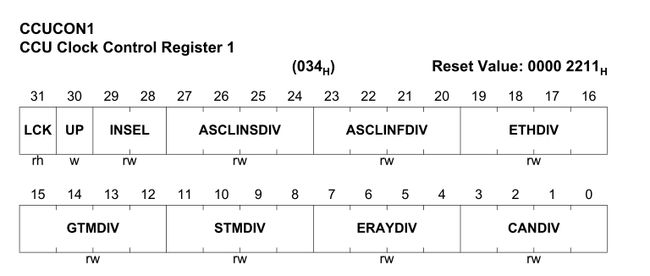

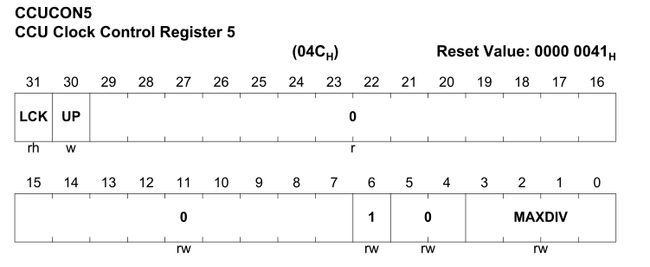

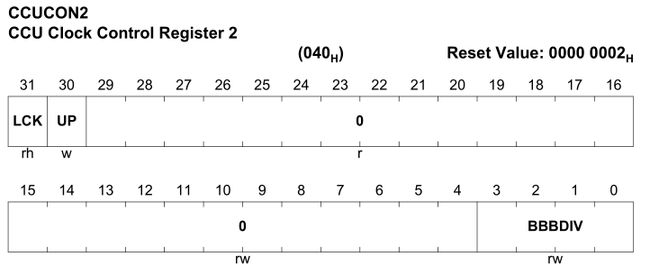

- 对应分频参数寄存器

- 分频实例

- 总结

前言

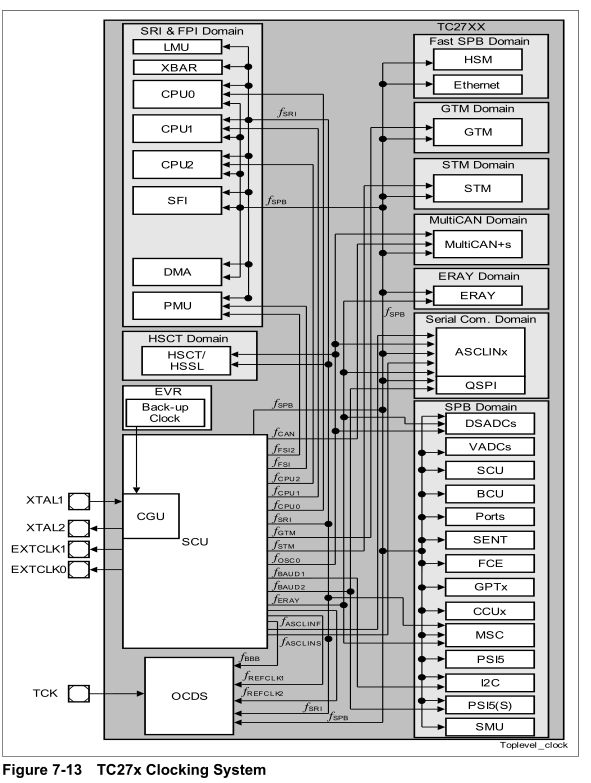

在Autosar OS中的Counter计数是由STM模块而来,需要在Counter中指定每个tick的时间,但这个时间是根据STM时钟来的,t=1/fstm,并不是指定的时间就是真的运行时间,例如指定的Seconds per tick时间为0.00000001,但STM频率为50000000HZ(50MHz),实际执行的时间会是0.00000002,导致os所有认为的时间都会慢一倍。基于该问题,本文详细介绍Autosar MCAL的MCU时钟相关配置,应用的芯片为TC27x系列。

MCU时钟配置

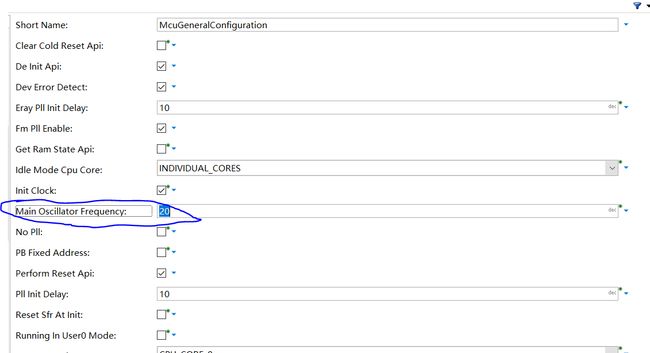

cfg配置外部晶振

一般都是用的外部晶振作为输入时钟源的方案。

问题:如何配置是从外部晶振来的Fosc?

CCU

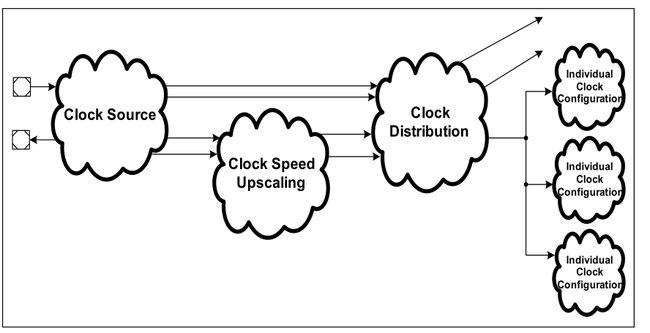

Clocking and Clock Control Unit 时钟和时钟控制单元

构建模块包括:•基本时钟生成(时钟源)•时钟速度提升•时钟分布•单个时钟配置

时钟源的选择

OSC(Oscillator Circuit)

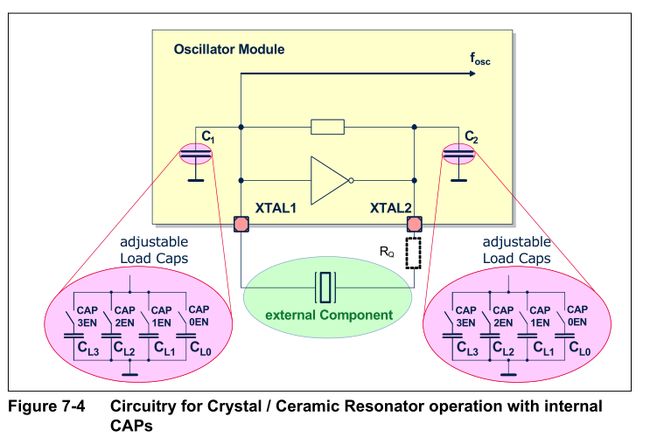

该晶振电路为皮尔斯晶振,设计用于外部晶体/陶瓷谐振器或外部稳定时钟源,由一个反向放大器XTAL1作为输入,XTAL2作为输出,集成反馈电阻

OSC的模式:

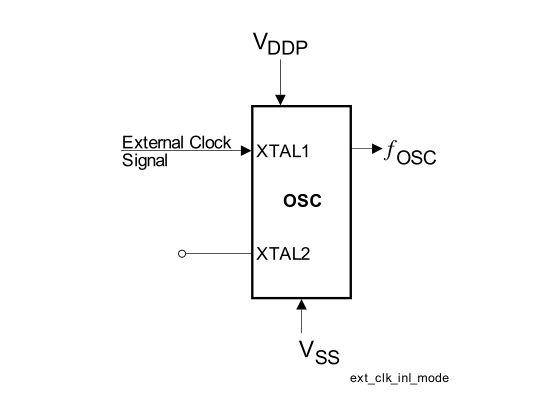

外部输入时钟模式:

1.External Input Clock Mode

使用外部时钟信号时,必须连接到XTAL1。XTAL2保持打开状态(未连接),这种模式下需要输入一个稳定的外部时钟源(固定频率的方波)

Figure 7-2 TC27x Direct Clock Input

当直接提供时钟信号时,不使用外部晶体/陶瓷谐振器(external crystal/ceramic resonator)并绕过晶振,如果在正常模式下使用,输入频率需要等于或大于锁相环VCO的输入频率(该值列在数据表中)。

CC和SR的含义:

CC:这些参数表示控制器特性,这是TC270 / TC275 / TC277的一个显著特征,必须在系统设计中考虑

SR:这些参数表示设计TC270 / TC275 / TC277的微控制器系统必须提供的系统要求。

外部晶体/陶瓷谐振模式

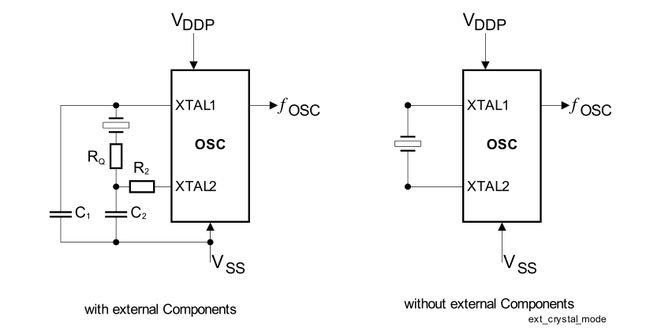

2.External Crystal / Ceramic Resonator Mode

下图显示了两种工作模式的推荐外部电路,外部晶体/陶瓷谐振器模式,包括和不包括外部组件。

包括外部组件:及电阻电容都是外部的。一般采用这种方式

不包括外部组件:电阻电容是内部的,需要进行配置(相关的寄存器)

芯片内部电路:

Back up时钟源

Back up Clock作为备用时钟源。该时钟源提供稳定可靠的时钟源,可作为系统的时钟源。它提供的精度低于外部晶体或陶瓷谐振器。备份时钟无法启用或禁用或以其他方式进行控制.可以配置寄存器CCUCON0.CLKSEL = 00B 选择Back up Clock作为** clock distribution的时钟源** ,配置寄存器CCUCON1.INSEL = 00B选择Back up Clock作为PLL / PLL_ERAY的时钟源。

该时钟由EVR Pre-regulator产生,频率为100MHZ,datasheet中描述如下:

Clock generation时钟生成

输入时钟

外部时钟通过OSC振荡后直接输出fosc0,还可以通过配置寄存器CCUCON1.INSEL = 01B选择fosc0作为fosc的输出。

内部时钟直接输出fback,还可以通过配置寄存器CCUCON1.INSEL = 00B来选择fback作为fosc的输出

cfg中配置使用PLL

![]()

cfg中没有找到在哪里配置使用内部backup时钟,可能默认都是用外部时钟fosc0,MCU的代码中也是默认CCUCON1.INSEL为1.

这里的配置项可以为CCUCON0.CLCSEL使用fpll作为外设时钟分配的时钟源。

PLL模式

通过配置PLL参数实现输入时钟的超频

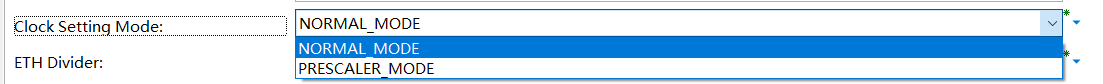

PLL有三种模式可以选择,配置软件中只有两种选择

cfg中配置模式:

Normal Mode

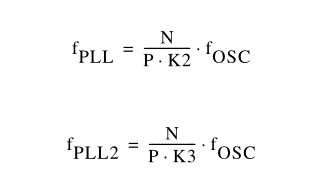

Bypassing K1 divider for Main PLL.屏蔽了K1分频。Normal模式下fpll和fpll2的计算公式如下:

Prescaler Mode

预分频器模式:Bypassing P, N, K2, K3 dividers for Main PLL,计算PLL频率公式如下:

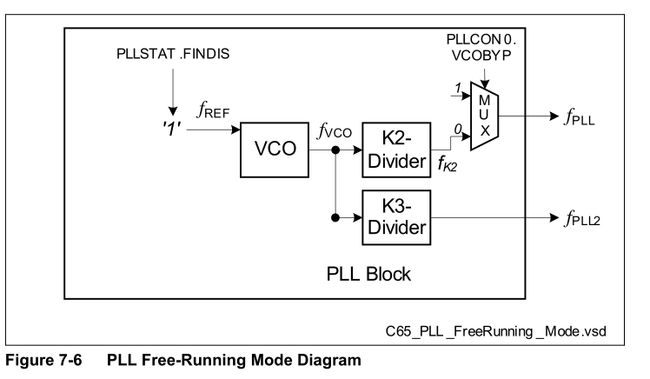

Freerunning Mode

自由运行模式:

在自由运行模式下,压控振荡器(VCO)fPLLBASE的基频输出仅被因子K2或K3分压。

PLL模式配置

配置为自由运行模式:

通过以下设置选择自由运行模式:

•PLLCON0.VCOBYP=0

•PLLCON0.SETFINDIS=1

当PLLSTAT.FINDIS = 1 and PLLSTAT.VCOBYST = 0时,进入自由运行模式

自由运行模式下的操作不需要fOSC的输入时钟频率。 Data Sheet中列出了自由运行模式fPLLBASE的频率。

配置为Prescaler Mode

通过以下设置选择预分频器模式:

•PLLCON0.VCOBYP=1

当以下要求有效时,进入预分频器模式:

•PLLSTAT。VCOBYST=1

预分频器模式下的需要fOSC的输入时钟频率。

配置为Normal Mode

通过以下设置选择正常模式

•PLLCON0.VCOBYP=0

•PLLCON0.CLRFINDIS=1

当以下要求全部有效时,进入正常模式:

•PLLSTAT.FINDIS=0

•PLLSTAT.VCOBYST=0

•PLLSTAT.VCOLOCK=1

•OSCCON.PLLLV=1

•OSCCON.PLLHV=1

正常模式下的操作要求输入时钟频率为fOSC

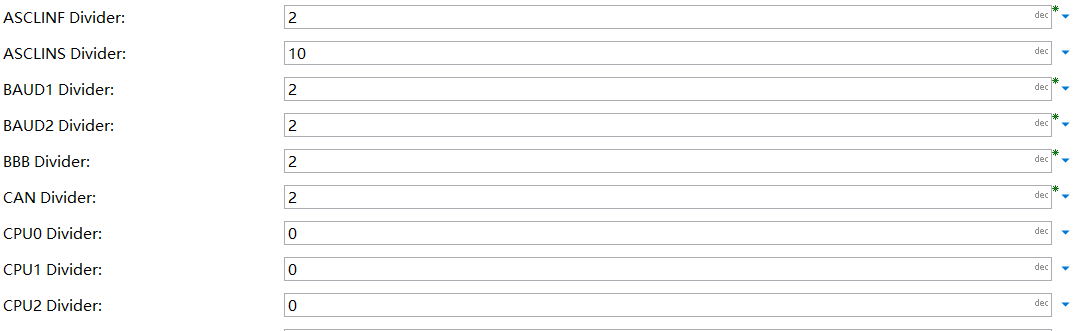

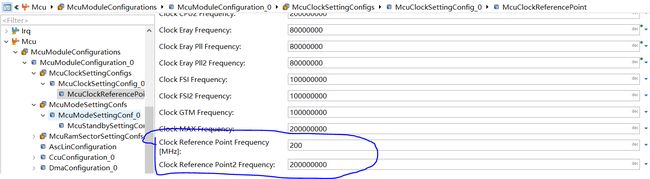

cfg配置fpll频率:

该频率是通过计算出来的,这里配置应该是为了校验

Fpll =( (Fosc * (McuNDivider + 1)) / ((McuK2Divider+1)(McuPDivider+1)))

Fpll2 =( (Fosc * (McuNDivider + 1)) / ((McuK3Divider+1)(McuPDivider+1)))

对应公式:

The McuClockReferencePointFrequency for NORMAL_MODE should be in range:

20 - 200 MHz for TC26x/TC27x

20 - 300 MHz for TC29x

tc27x-datasheet中描述如下:

配置分频参数N,P,K1-3

对于PLL来说,需要配置PLLCON0和PLLCOCN1寄存器,具体参见芯片手册。需要注意的是,实际值为配置值+1

对于PLLERAY来说,也是类似的。

cfg配置分频参数N,P,K1-3

实际计算例子:

配置为外部晶振输入20MHZ,PLL为Noraml mode,K1为1+1=2(Normal mode下K1无作用),K2为2+1=3,K3为2+1=3,N为59+1=60,P为1+1=2.

则: fpll = 20 * 60/(2 * 3)=200M ,fpll2=20 * 60/(2 * 3)=200M.与上面的频率配置一致

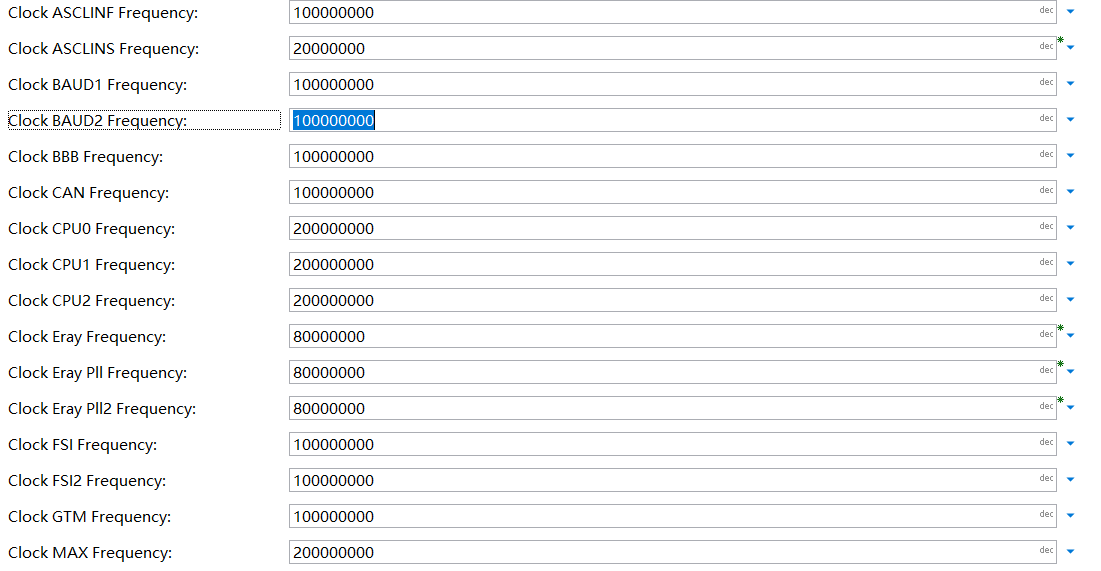

Frequency Modulation频率调制

如果PLL在正常模式下工作,则输出频率fPLL还可以通过低频调制进行修改。fVCO是随机调制的

通过位PLLCON0.MODEN启用调制。调制本身随配置的调制幅度的范围随机地改变VCO频率。通过PLLCON2.MODCFG[9:0]选择调制幅度

cfg中配置允许PLL调制:

cfg中配置调制幅度%:

![]()

计算公式:

MODCFG[9:0]=(64* McuFMPllModAmp/100*McuMainOscillatorFrequency/McuPllPDivider *McuPllNDivider/3.6)

datasheet中fMV为3.6MHZ

![]()

MODCFG最大为32,MA = (3.6/(2 * fosc * N/P)) * MODCFG[9:0]

32 * McuFMPllModAmp/100 = (3.6/(2 * McuMainOscillatorFrequency*N/P))*MODCFG[9:0]

M O D C F G [ 9 : 0 ] = 32 ∗ M A ∗ 2 ∗ f o s c ∗ N 100 ∗ P ∗ 3.6 MODCFG[9:0]=\frac{32*MA*2*fosc*N}{100*P*3.6} MODCFG[9:0]=100∗P∗3.632∗MA∗2∗fosc∗N

与cfg中公式对应。McuFMPllModAmp单位为%

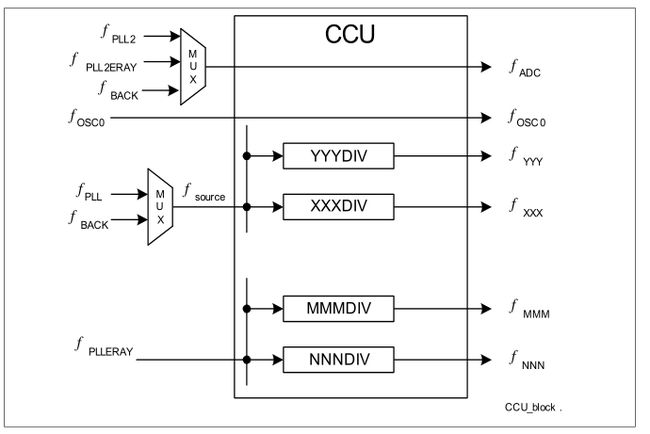

Clock Distribution时钟分配

时钟分配通过时钟控制单元(CCU)完成。CCU接收由两个PLL(fPLL/PLL2和fPLL_ERAY/PLL_ERAY2)、备用时钟fBack和fOSC0创建的时钟。这些时钟直接转发或经过分频,以提供子时钟域

对于大多数时钟,提供线性分频器以使时钟频率适应应用要求。该除法器由位字段XXXDIV控制

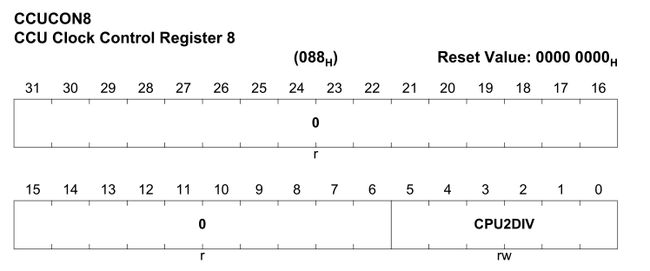

对于CPU时钟,实现了更复杂的分频器。这允许更好地控制单个CPU的时钟频率变化。该机制允许频率变化适应由应用定义的特定电流限制

这里还有一个用于调试块的固定参考时钟REFCLK1/2,它将主时钟fPLL/fPLLERAY除以24。这允许OCDS独立于选定的SRI和SPB时钟速度生成时间戳。

fMAX被定义为系统内部使用的从fSOURCE导出的任何时钟的最高频率。

以下是不同时钟的简要概述:

•系统总线

——fSRI定义了SRI总线的操作性能,因此定义了所有连接的主设备和从设备之间的数据交换率

——fSPB定义了SPB总线的操作绩效,因此定义所有连接的主机和从设备与中断系统之间的数据交换率

•CPU Controls

–fCPU0定义CPU0的执行速度

–fCPU1定义CPU1的执行速度

•PMU controls

–fFSI2定义了读取操作的PFlash的执行速度

–fFSI定义了所有其他闪存操作的执行速度

•外设时钟

-fSTM,STM模块的时钟

-fGTM,GTM模块的时钟

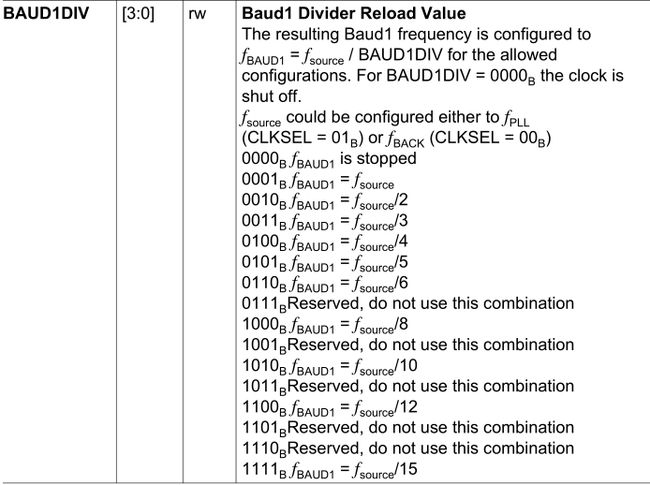

-fBAUD1定义了独立于系统其余部分的“慢速”通信接口的基本频率。这允许IIC以恒定波特率(频率)工作。

–fBAUD2定义了独立于系统其余部分的“快速”通信接口的基本频率。这允许QSPI和PSI5以恒定波特率(频率)运行。

–fCAN定义了独立于系统其余部分的多CAN的基本频率(表7-2中列出的限制除外)。这允许MultiCAN在恒定波特率(频率)下运行。

–fASCLINF/ASCLIN定义了独立于系统其他部分的ASCLIN的基本频率(表7-2中列出的限制除外)。这允许ASCLIN以恒定波特率(频率)运行。

•调试系统

——由于调试应不干扰应用系统,因此可使用专用调试资源的单独时钟fBBB。这允许在更改其他时钟配置期间进行调试(跟踪生成)。请注意,fBBB需要快于或等于fSPB才能进行调试

整个系统基于单个时钟(fSOURCE),以实现同步系统的性能优势。因此,在配置时钟控制选项时必须考虑某些限制

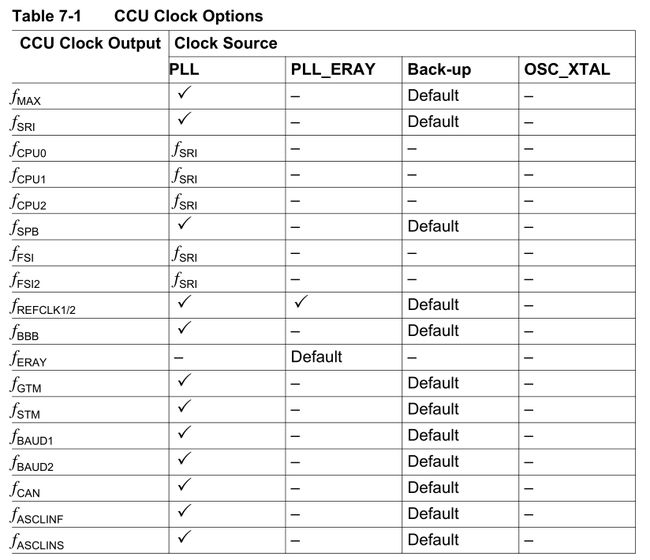

Clock Divider Limitations

对于控制不同子时钟域/模块的时钟分频器,允许值是有限的,必须遵守以下比率。比率定义如下:时钟A=fAAA;时钟B=fBBB.允许的比率为1:n,其中n具有定义的值范围。在该定义中,时钟A总是快于或等于时钟B,其中fAAA[MHz]=n*fBBB[MHz]

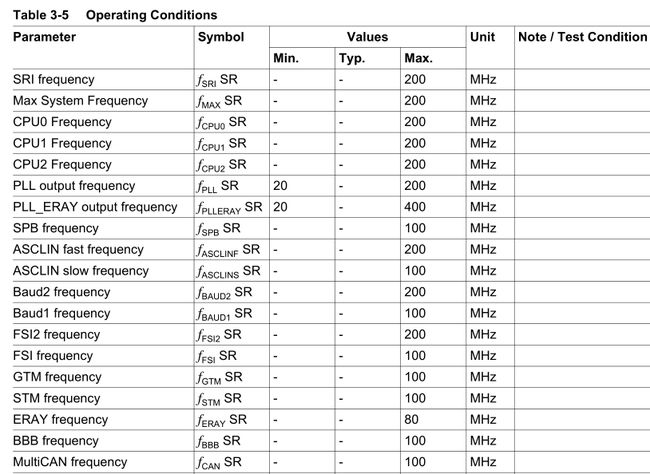

data sheet中规定的最大频率

1)不允许将寄存器CCUCON0、CCUCON1和CCUCON2配置为导致违反允许比率的值,

2) fGTM可以更快、更慢或等于fSPB

3) fSPB可以更快、更慢或等于fSTM

4) fBBB必须更快,或等于fSPB

5)fBAUD1可以更快、更慢或等于fSPB

6)fBAUD2可以更快、更慢或等于fSPB

7)fCAN可以更快、更慢或等于fSPB

8)fASCLINF可以更快、更慢或等于fSPB

9)fASCLINS可以更快、更慢或等于fSPB

配置外设时钟分频参数

cfg中配置分频参数

cfg中配置频率,校验用

对应分频参数寄存器

McuBAUD1Divider :It is the BAUD1 divider value used for generation of clock FBaud1. FBaud1 = (Fsource / McuBAUD1Divider).

有效值为: 0,1,2,3,4,5,6,8,10,12,15.

Fcpu0 = (Fsri * (64 - McuCPU0Divider))/64 .

具体分频值的计算公式可以参考芯片手册或者cfg中的描述信息。

分频实例

以STM为例,配置频率为100M,设置的分频值为2.且使用PLL的时钟(配置为200M),则fSTM=fpll/2=200M/2=100M,校验通过

总结

以上就是MCU关于时钟相关的配置,主要还是参考芯片用户手册和datasheet.在Autosar的MCU配置中,时钟主要与McuClockReferencePoint相关,McuGeneralConfiguration配置中也有部分内容与时钟相关。其他BSW模块都会用到McuClockReferencePoint作为时钟的引入。

参考资料:

Infineon-TC27x_D-step-UM-v02_02-EN.pdf

Infineon-TC27xDC-DataSheet-v01_00-EN.pdf

AURIX™公开课第8讲上-时钟系统

若你觉得本文对你有帮助,欢迎点赞,关注,收藏,转发~~~

你的鼓励是对小弟的最大支持~~~

建了一个WX公众h,《汽车电子学习笔记》感兴趣可以关注一下~~~文章都会同步更新~