计算机组成原理总复习——题目练习

选择题

ppt3.1

1.在CPU寄存器中, ( B )对用户是透明的。

A.程序计数器 B.指令寄存器 C.状态寄存器 D.通用寄存器

解析: 汇编程序员可以通过指定待执行指令的地址来设置PC(程序计数器)的值,状态寄存器、通用寄存器只有为汇编程序员可见,才能实现编程。而IR、MAR、MDR是CPU的内部工作寄存器,对程序员均不可见,所以它们被称为“透明”寄存器。

2.程序计数器PC用来存放指令地址,其位数与(D)相同。

A. IR B. PSW C. MDR D. MAR

3.指令寄存器的位数取决于(C),通用寄存器取决于(B),而程序计数器取决于(A)。

A. 存储器的容量 B. 机器字长 C. 指令字长 D.存储字长

4.采用同步控制的目的是 ( C )。

A. 提高执行速度 B.满足不同的设备对时间安排的需要

C.简化控制时序 D.满足不同的操作对时间安排的需要

- 异步控制常用于 ( A )。

A. CPU访问外围设备 B.微程序控制器

C. 微型机的CPU D.组合逻辑控制器

ppt3.2

1.下列数中最小的数为( A )。

A.(101001)2 B.(52)8 C.(2B)16 D.(44)10

2.( D )表示法主要用于表示浮点数中的阶码。

A. 原码 B. 补码 C. 反码 D. 移码

3.在小型或微型计算机里,普遍采用的字符编码是( D )。

A.BCD码 B.16进制 C.格雷码 D.ASCⅡ码

4.根据国标规定,每个汉字在计算机内占用( B )存储。

A.一个字节 B.二个字节 C.三个字节 D.四个字节

5.设X= —0.1011,则[X]补为( C )。

A.1.1011 B.1.0100 C.1.0101 D.1.1001

6.字长16位,用定点小数补码表示时,一个字能表示的数据范围是( D )。

A.0~(1-2-15) B.-(1-2-15)~(1-2-15)C.-1~+1 D.-1~(1-2-15)

7.某10位字长的浮点数,其中阶码为4位(包括1位阶符),用移码表示;尾数为6位(包括1位数符),若二进制数X=2011×(-1),则在用补码表示尾数,其规格化表示的机器数分别是( A )。

A. 1100,1.10000 B. 1001,1.10000

C. 1011,1.00000 D. 1100,1.00000

8.计算机中表示地址时使用( A )。

A.无符号数 B.原码 C.反码 D.补码

9. 以下四种类型指令中,执行时间最长的是( C )。

A. RR型 B. RS型 C. SS型 D. RX型

10. 设变址寄存器为X,形式地址为D,()表示寄存器X的内容,寻址方式的有效地址为(A )。

A.EA=(X)+D B.EA=(X)+(D) C.EA=((X)+D) D.EA=((X)+(D))

11.指令地址字段中,直接指出操作数本身的寻址,称为( B )。

A.隐含寻址 B.立即寻址

C.寄存器寻址 D.直接寻址

12.目前的计算机,从原理上讲( C )。

A. 指令以二进制形式存放,数据以十进制形式存放

B. 指令以十进制形式存放,数据以二进制形式存放

C. 指令和数据都以二进制形式存放

D. 指令和数据都以十进制形式存放

13.指令系统中采用不同寻址方式的目的主要是( B )。

A.实现存储程序和程序控制

B.缩短指令长度,扩大寻址空间,提高编程灵活性

C.可以直接访问外存

D.提供扩展操作码的可能并降低指令译码难度

14.某指令系统的指令字长为16位,每个地址字段占6位,用扩展操作码技术。若指令系统具有二地址指令15条、一地址指令48条,则最多有( C )条零地址指令。

A.64 B.256 C.1024 D.2048

15.某机器字长16位,主存按字节编址,转移指令采用相对寻址,由两个字节组成,第一字节为操作码字段,第二字节为相对位移量字段。假定取指令时,每取一个字节PC自动加1。若某转移指令所在主存地址为2000H,相对位移量字段的内容为06H,则该转移指令成功转移后的目标地址是( C )。

A.2006H B.2007H C.2008H D.2009H

16.为了缩短指令中某地址段的位数,有效的方法是采用( D )。

A.立即寻址 B.变址寻址 C.间接寻址 D.寄存器寻址

17.以下几种寻址方式中,( D )方式取操作数最快。

A.直接寻址 B.变址寻址 C.间接寻址 D.寄存器寻址

18.先计算后再访问内存的寻址方式是( D )。

A.立即寻址 B.直接寻址 C.间接寻址 D.变址寻址

19.以下几种寻址方式中,( D )方式对实现程序浮动提供支持。

A.基址寻址 B.变址寻址 C.间接寻址 D.相对寻址

解析:操作数与地址可以一起在主存中任意浮动

20.下列关于RISC的叙述中,错误的是( A )。

A.RISC普遍采用微程序控制器

B.RISC大多数指令在一个时钟周期内完成

C.RISC的内部通用寄存器数量相对CISC多

D.RISC的指令数、寻址方式和指令格式种类相对CISC少

解析:RISC采用硬步线方式,CISC采用微程序控制器

21.某指令系统采用32位单字长的指令,每个地址字段占12位,用扩展操作码技术。若指令系统具有250条二地址指令、那么还可以有( D )条一地址指令。

A.4K B.8K C.16K D.24K

22.某指令系统的指令字长为8位,每个地址字段占3位,用扩展操作码技术。若指令系统具有2条二地址指令、10条零地址指令,则最多有( B )条一地址指令。

A.20 B.14 C.10 D.6

23.在浮点数的编码中,( D )在机器数中不出现,是隐含的。

A. 阶码 B.尾数 C. 符号 D.基数

24.字长16位,用定点整数补码表示时,最小正整数是( A );

最大负数是( C )。

A. +1 B. +215 C. -215 D.-1

25.设指令字长为16位,存储器按字节编,CPU 读取一条单字长指令后,PC值自动加( B )。

A.1 B.2 C.4 D.0

26.能改变程序执行顺序的是( D )指令。

A.数据传送 B.移位操作 C.输入输出 D.转移

27.在堆栈中,保持不变的是( B )。

A.栈顶 B.栈底 C.堆栈指针 D.栈中的数据

28.数据传送类指令不包括( D )。

A.RR型 B.RS型 C.SS型 D.SI型

29.设[X]补=1.x1x2x3,当满足( A )时,X> -1/2成立。

A. x1=1,x2x3 至少有一个为1 B.x1=0,x2x3任意

C. x1=0,x2x3 至少有一个为1 D.x1=1,x2x3任意

30.在规格化浮点数中,保持其它方面不变,将阶码部分的移码表示改为补码表示,将使数的表示范围( C )。

A.增大 B.减小 C.不变 D.以上都不对

ppt3.6

1.下列的寄存器中, 汇编语言程序员可见的是( C ) 。

A.MAR B.MDR C.PC D.IR

2. 程序计数器取决于(A)。

A. 存储器的容量 B. 机器字长 C. 指令字长 D.存储字长

3.微命令发生器的作用是( D)。

A. 主存取出指令 B. 完成指令的分析功能

C. 产生控制时序 D. 产生各种微操作控制信号

4.微命令发生器的设计与下列因素基本无关的是( A )。

A. CPU寄存器数量 B. 指令系统 C. 数据通路 D. 机器字长

5.计算机操作的最小单位时间是( A )。

A. 时钟周期 B. 指令周期 C. CPU周期 D. 工作脉冲

6.从取指令开始到执行完成所需时间,称之为( B )。

A. 时钟周期 B. 指令周期 C. CPU周期 D. 访存周期

7.微程序存放在( A )中。

A. 控制存储器 B. 指令寄存器 C. RAM D. 内存

一、单选题

8.在取指令操作之后,程序计数器(即PC)的内容是( D)。

A. 当前指令的地址 B.程序中指令的数量

C. 操作数的地址 D.下一条指令的地址

9.一个节拍信号的宽度是指( A )。

A. 时钟周期 B. 指令周期 C. CPU周期 D. 存储周期

10.存放微指令的存储器包含在( D )中。

A. 外存 B. 内存 C. Cache D. CPU

11.以硬布线方式构成的控制器又称(A)。

A. 组合逻辑型控制器 B. 存储逻辑型控制器

C. 微程序控制器 D.运算器

12. 相对于微指令控制器、硬布线控制器的特点是(D )。

A 指令执行速度慢,指令功能的修改和扩展容易

B 指令执行速度慢,指令功能的修改和扩展难

C 指令执行速度快,指令功能的修改和扩展容易

D 指令执行速度快,指令功能的修改和扩展难

13. 冯•诺依曼计算机中指令和数据均以二进制形式存放在存储器中,CPU区分它们的依据是(C)

14. A.指令操作码的译码结果 B.指令和数据的寻址方式C.指令周期的不同阶段 D.指令和数据所在的存储单元

15. 下面有关程序计数器PC的叙述中,错误的是(C)

A.PC中总是存放指令地址

B.PC的值由CPU在执行指令过程中进行修改

C.转移指令时,PC的值总是修改为转移目标指令的地址

D.PC的位数一般与存储器地址寄存器MAR的位数一样

15. 下面叙述中,错误的是(B)

A.指令周期的第一操作是取指令

B.为了进行取指操作,控制器需要得到相应的指令

C.取指操作是控制器自动进行的

D.指令执行时有些操作是相同或相似的,如取指令、取操作数地址等

ppt4.4——4.6

1.以下器件中存取速度最快的是( C ) 。

A.Cache B.主存 C.寄存器 D.磁盘

2. 下列叙述中正确的是(A)。

A.主存可由RAM和ROM组成 B.主存只能由RAM组成

C.主存只能由ROM组成 D.都不对

3.CPU可以直接访问的存储器是( D)。

A.磁盘 B.磁带 C.光盘 D.主存

4. 某计算机主存容量为64KB,其中ROM区为4KB,其余为RAM区,按字节编址。现要用2K×8位的ROM芯片和4K×4位的RAM芯片来设计该存储器,则需要上述规格的ROM芯片数和RAM芯片数分别是(D)。

A. 1,15 B. 2,15 C. 1,30 D. 2,30

5. 用双稳态触发器的两个稳定状态表示1和0的存储器是(C)。

A. DRAM B. EPROM C. SRAM D. EEPROM

6. 某计算机字长为16位,主存容量为64KB,CPU按字寻址,

其可寻址范围的单元数(B )。

A. 64K B. 32K C. 64KB D. 32KB

7. 某计算机字长为32位,主存容量为4MB,CPU按字寻址,

其寻址范围是0到(A)。

A.220-1 B.221-1 C.222-1 D.223-1

8. 某计算机字长为16位,主存容量为256KB,CPU按字节寻址,其寻址范围是0到(D)。

A.221-1 B.220-1 C.219-1 D.218-1

9.有4个16K×8位的存储芯片,可设计(A)容量的存储器。

A.32K×16位 B.16K×16位 C.32K×8位 D.8K×16位

10.假定用若干个2 K×4位的芯片组成一个8 K×8位的存储器,则地址0B1FH所在芯片的最小地址是(D)

A.0000H B.0600H C.0700H D.0800H

15.下列有关RAM和ROM的叙述中,正确的是( A)

I.RAM是易失性存储器,ROM是非易失性存储器

II.RAM和ROM都采用随机存取方式进行信息访问

III.RAM和ROM都可用作Cache

IV.RAM和ROM都需要进行刷新

A.仅I和II B.仅II和III C.仅I、II和IV D.仅II、III和IV

16.下列各类存储器中,不采用随机存取方式的是( B ) A. EPROM B. CDROM C. DRAM D. SRAM

解析:

RAM-RamdomAccessMemory易挥发性随机存取存储器,高速存取,读写时间相等,且与地址无关,如计算机内存等。

ROM-Read Only Memory只读存储器。断电后信息不丢失,如计算机启动用的BIOS芯片

EPROM(Erasable Programmable ROM,可擦除可编程ROM)芯片可重复擦除和写入,解决了PROM芯片只能写入一次的弊端

CD只读存储器,意即只能读不能写,区别于CD RAM,可读写CD存储器

DRAM为动态RAM(Dynamic RAM/DRAM),DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,SRAM为静态RAM(Static RAM/SRAM),SRAM速度非常快,是目前读写最快的存储设备,但是它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU的一级缓冲,二级缓冲。

17.某计算机存储器按字节编址,主存地址空间大小为64MB,现用4M x 8 位的RAM 芯片组成32MB 的主存储器,则存储器地址寄存器MAR 的位数至少是( D )

A.22 位 B.23 位 C.25 位 D.26 位

ppt5

1.连接计算机与计算机的总线属于( C )。

A.内总线 B.系统总线 C.通信总线 D.都不是

2.连接在总线上的多个部件( B )。

A.只能分时向总线发送数据,并只能分时从总线接受数据

B.只能分时向总线发送数据,但可同时从总线接受数据

C.可同时向总线发送数据,并同时从总线接受数据

D.可同时向总线发送数据,并只能分时从总线接受数据

3.在总线上,同一时刻( A)。

A.只能有一个主设备控制总线传输操作

B.只能有一个从设备控制总线传输操作

C.只能有一个主设备和一个从设备控制总线传输操作

D.可以多个主设备控制总线传输操作

4.( )不属于系统总线接口的功能( C )。

A.数据缓冲 B.数据转换 C.状态设置 D.算术逻辑运算

5.系统总线中控制线的功能是( D )。

A.提供数据信息

B.主存和I/O设备的时序信号和控制信号

C.主存和I/O设备的响应信号

D.B和C

6.某系统总线在一个总线周期总并行传输4字节的信息,一个总线周期占用二个时钟周期,总线时钟频率10MHz,则总线带宽( B )MB/s。

A.10 B.20 C.40 D.80

7. 在三种集中式总线仲裁中,( A )方式对电路故障最敏感。

A.链式查询 B.计数器定时 C.独立请求 D.都一样

8.在各种异步通信方式中,( C)的速度最快。

A.全互锁 B.半互锁 C.不互锁 D.速度均等

1.主机与I/O设备传送数据时,主机与I/O设备是串行工作的,说明采用 ( A ) 。

A.程序查询方式 B.程序中断方式 C.通道方式 D.DMA方式

2.显示汉字采用点阵字库,若每个汉字采用16×16点阵表示,7500个汉字的字库容量是( B )。

A. 16K B. 240KB C. 320K D. 1MB

3.I/O端口的编址方式采用统一编址时,存储单元和I/O设备是靠( B )来区分的。

A. 不同的地址线 B. 不同的地址码

C. 不同的控制线 D. 都不是

4.下列叙述中正确的是( D )。

A. 只有I/O指令才可以访问I/O设备

B. 统一编址方式下,不能访问I/O设备

C. 访问存储器的指令,一定不能访问I/O设备

D. 具有专门I/O指令的计算机中, I/O设备才可能单独编址

5.鼠标适合( B )实现输入操作。

A.程序查询方式 B.程序中断方式 C.通道方式 D.DMA方式

6.中断的概念是指( A )。

A. 暂停正在运行的程序 B. 暂停对内存的访问

C. 暂停CPU运行 D. I/O设备的输入或输出

7.下列叙述中正确的是 ( D )。

A.程序中断方式使CPU和外设能够并行工作

B.程序中断方式下,CPU和外设直接交换数据

C.程序中断方式下,CPU会有额外的开销用于断点、现场的保护和恢复等

D.程序中断方式适合磁盘一类设备

8.在DMA方式中,由( A )发出DMA请求。 。

A. I/O设备 B. DMA控制器 C. CPU D. 内存

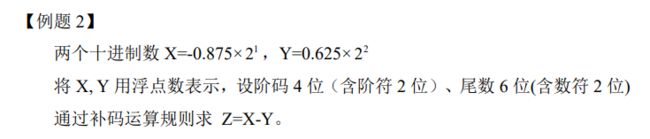

计算题:浮点数运算

步骤:

(1) 检测能否简化操作: 判操作数是否为 0

(2) 对阶:小数点实际位置对齐

首先把两个数写成规格化形式

对阶规则:小阶向大阶对齐

对阶操作:小阶阶码增大,尾数右移。

若: A E > B E A_E > B_E AE>BE ,则 B E + 1 B_E +1 BE+1 , B M B_M BM 右移, 直 到 B E = A E 直到 B_E = A_E 直到BE=AE

若: A E < B E , 则 A E + 1 , A M 右 移 , 直 到 B E = A E A_E < B_E ,则 AE +1 , A_M 右移,直到 B_E = A_E AE<BE,则AE+1,AM右移,直到BE=AE

(3) 尾数加减:做减法时,一定要变+为-,即减数变补

(4) 结果规格化

若 ∣ M ∣ < 1 2 |M| < \frac{1}{2} ∣M∣<21,应左移规格化(左规)

若 ∣ M ∣ > 1 |M| >1 ∣M∣>1,结果溢出,应右移规格化(右规)

舍入方法:(1) 0 舍 1 入 (2)末位恒置 1

综合题

1、名词解释,如

可能有:

CPU——Central Processing Unit,中央处理机(器),由运算器和控制器组成。

运算器:用于实现算术运算(如:加减乘除)、逻辑运算(如:与或非。

ALU——Arithmetic Logic Unit,算术逻辑运算单元,运算器中完成算术逻辑运算的逻辑部件;

ACC——Accumulator,累加器,运算器中运算前存放操作数、运算后存放运算结果的寄存器;

控制器:协调并控制计算机各部分执行程序的指令序列,包括取指令,分析指令和执行指令

PC——Program Counter,程序计数器,存放当前欲执行指令的地址

IR——Instruction Register,指令寄存器,存放当前正在执行的指令的寄存器;

CU——Control Unit,控制单元(部件),控制器中产生微操作命令序列的部件,为控制器的核心部件;

程序状态字寄存器 PSW(program status word):记录程序的运行状态、指示程序的工作方式。

MAR——Memory Address Register,存储器地址寄存器,保存当前 CPU 所访问的内存单元地址

MDR——Memory Data Register,存储器数据缓冲寄存器,主存中用来存放从某单元读出、或写入某存储单元数据的寄存器;

作为 CPU 与内存、I/O 设备之间信息传送的缓冲区,补偿其在速度上的差异。

堆栈指针寄存器 SP (Stack Pointer)

数据通路,操作时间表

扩展操作码,二进制码

指令流程(MOV,双操作数)

微程序和组合逻辑控制