Cadence SPB17.4 - DRC - error and warning

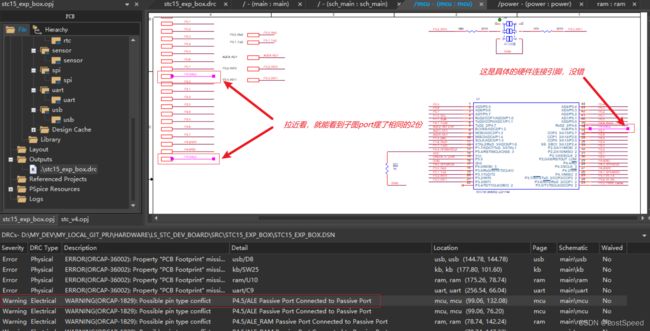

画好一张层次原理图,DRC检查时,发现巨多错误和警告。只是先画层次原理图,封装准备后续弄。所以除了封装报错,不应该有其他报错的:

ERROR(ORCAP-36002): Property "PCB Footprint" missing

尝试用排除法来修正除了封装报错之外的其他错误和警告

笔记

实验环境

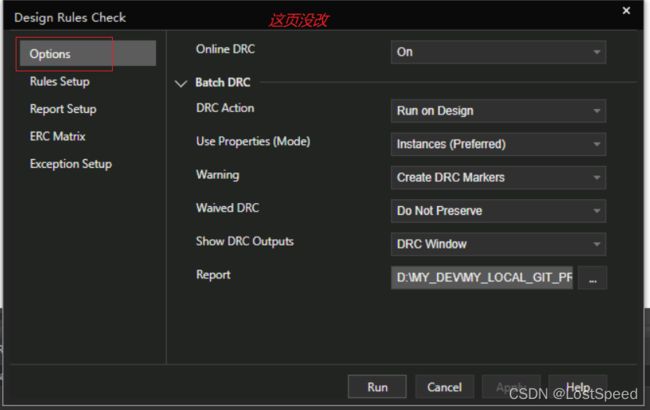

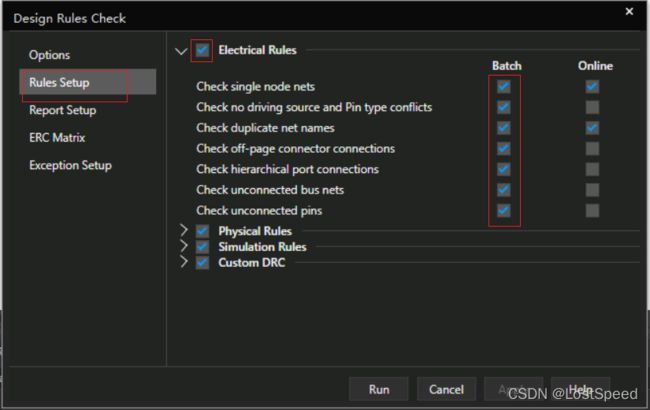

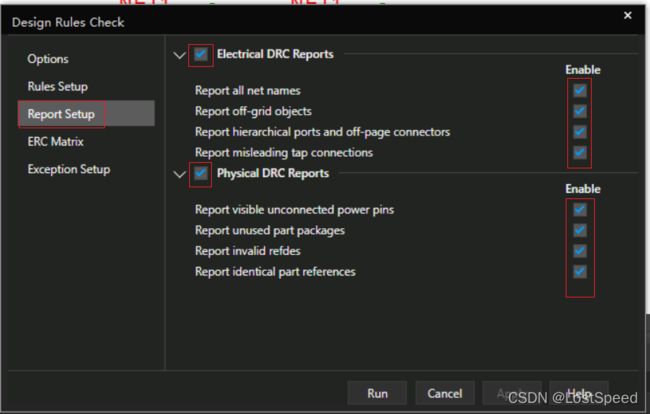

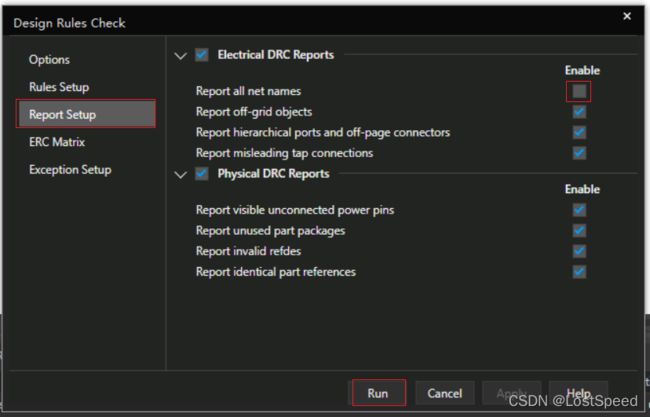

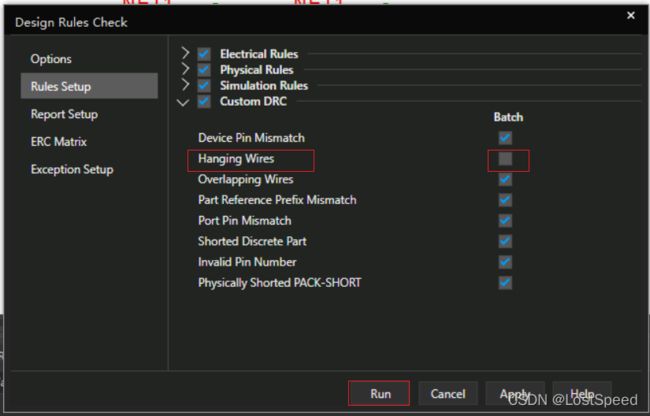

SPB17.4 + DRC规则都打开(能勾选的手工DRC选项都打开了):

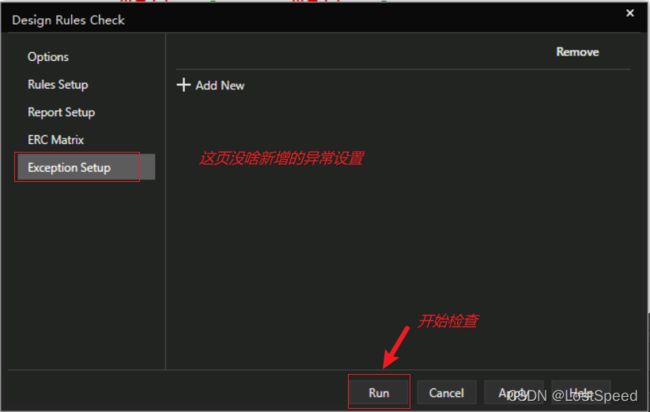

这个规则设置过一次就行,以后点击DRC菜单后,弹出DRC界面后,直接点击Run,检查的参数和上次都是一样的。

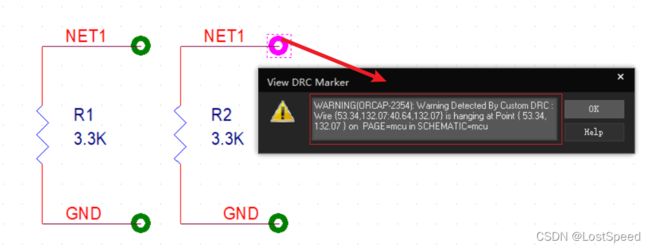

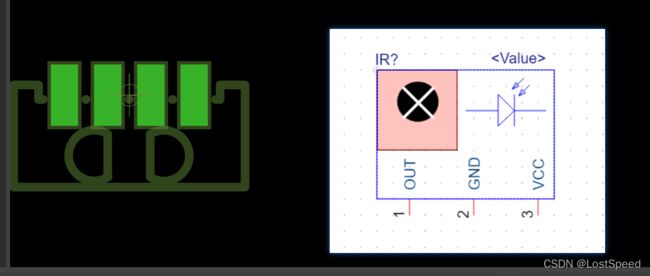

WARNING(ORCAP-2354) Wire is hanging at Point

测试用例:

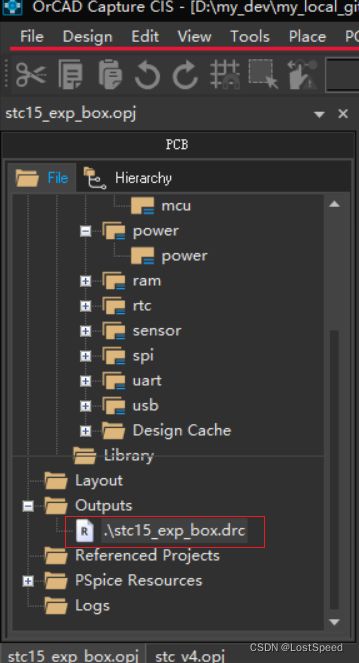

打开.drc,看到警告信息如下:

Checking for Hanging Wires

WARNING(ORCAP-2354): Warning Detected By Custom DRC : Wire {35.56,132.07:22.86,132.07} is hanging at Point { 35.56, 132.07 } on PAGE=mcu in SCHEMATIC=mcu

WARNING(ORCAP-2354): Warning Detected By Custom DRC : Wire {35.56,154.94:22.86,154.94} is hanging at Point { 35.56, 154.94 } on PAGE=mcu in SCHEMATIC=mcu

WARNING(ORCAP-2354): Warning Detected By Custom DRC : Wire {53.34,132.07:40.64,132.07} is hanging at Point { 53.34, 132.07 } on PAGE=mcu in SCHEMATIC=mcu

WARNING(ORCAP-2354): Warning Detected By Custom DRC : Wire {53.34,154.94:40.64,154.94} is hanging at Point { 53.34, 154.94 } on PAGE=mcu in SCHEMATIC=mcu

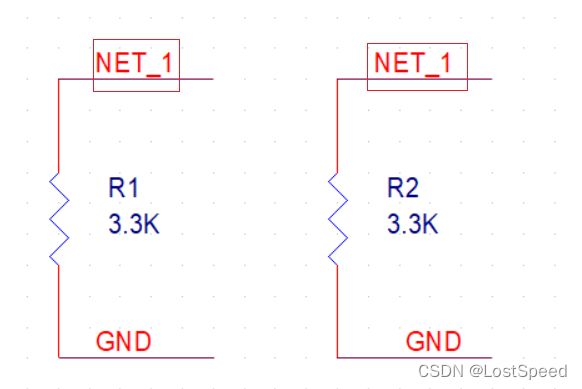

这个测试用例,没啥错误。为啥会出这样的警告呢?应该是DRC规则中检查了啥,去找下。看到DRC规则中,可选DRC规则中,勾选了"Hanging Wires",这个选项的官方说明如下:

这个选项的含义 : 检查所有未连接的线的末端。测试用例这个线虽然未连接到其他器件,但是元件出来的线上面有网络标号,等于是连接了。那么这个检查是可以不要的。去掉"Hanging Wires"勾选,点击"Run", 进行DRC检查:

这个警告消掉了, DRC窗口和DRC文件中都没有这个警告了。

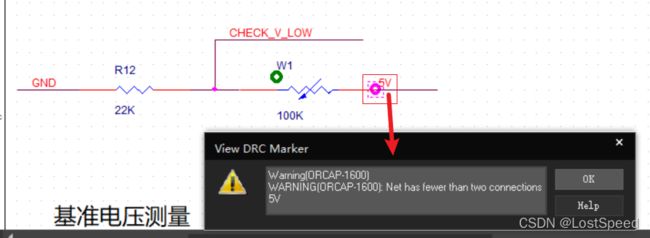

WARNING(ORCAP-1600): Net has fewer than two connections

这个警告明显,网络需要2个硬件连接才行。如果只在一个悬空的硬件连接上标注一个网络,也没意义啊。如果不是手误,那这个网络标号去掉,按X键,加上 NO Connect标记。如果是手误,就要在同网络的硬件连接上,加上相同的网络标号。按照正常逻辑,在一个硬件连接上,只有一个网络标号,那应该是逻辑出问题了,可能漏掉了其他元件上的网络连接。

测试用例1:

解决这个警告的方法:让一个网络标号,至少连接2个硬件连接。如下:

再运行DRC,此警告消失。

测试用例2:

在设计节点上Find 5V 字样,如下:

可以看到,5V的网络标号,是在不同子图中出现。网络标号只是在子图中有效。如果网不同子图中的同名网络标号都有效,需要在子图上添加子图端口来连接不同子图的同名网络标号。

测试用例3:

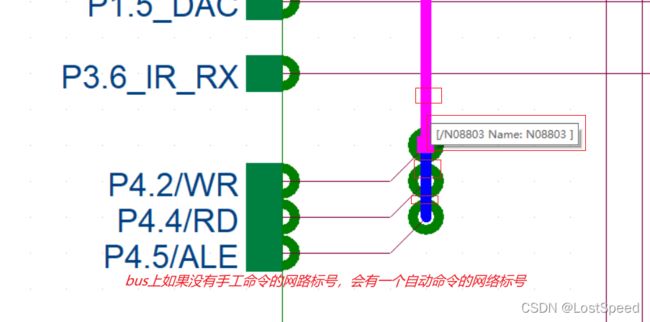

如果不给硬件连接填写网络标号,但是拉出一条线,也是会有自动命名的网络标号名称,将鼠标放到没放网络标号的线上,就能看到自动命名的网络标号。这时,就要根据实际情况考虑是放NODRC标记,还是加网路标号。补全同名网络,加了对应子图端口。再DRC, 此警告消失。

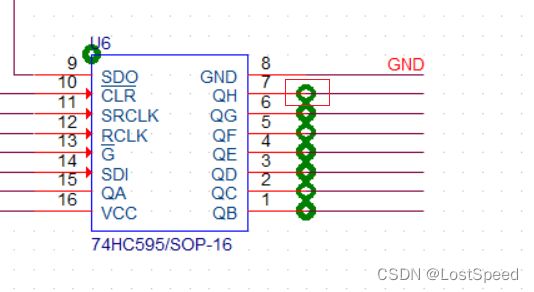

测试用例4:

在层次原理图中使用了bus, e.g. DAT[0…7] 或 DAT[0:7], 但是 硬件引脚上缺一个网络标号(e.g. DAT3没有,其他网络标号都有),也会出这个警告。因为bus的网络标号必须是连续的,针对这种情况,必须要将一个bus分成多个bus, 每个bus中包含连续的网络标号集合。e.g. DAT[0…7] 分为 DAT[0…2] and DAT[4…7]

ERROR(ORCAP-1631): Duplicate reference

出现这个错误,是说明元件位号重复了(多个元器件都使用一个位号),一般图大了,又没有自动重新分配位号,就会由于手误(元件拷贝来拷贝去,或者位号都是照着参考设计手工写的,或者放新元件时,SPB自动将上一次的相同前缀标识自动加1 e.g. U?, 自己忘了手工改位号)出现位号重复的问题。

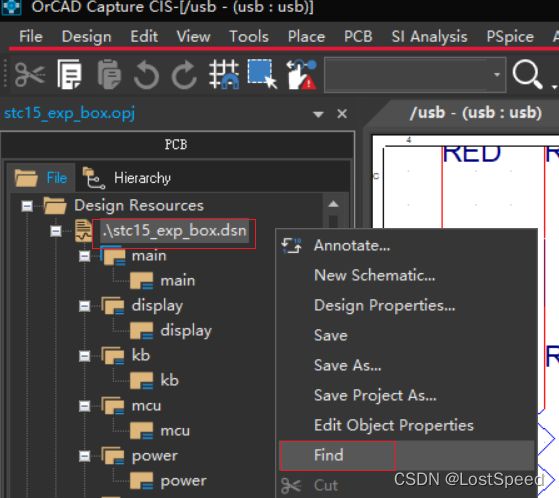

测试用例:

先找一个这种错误,放大图纸,由DRC窗口双击跳转到这个错误。可以看到这种错误,并没有一个DRC的错误标记(绿色小圆环)指示错误位置。只是用虚线框住了报错的元件。我们那已经知道这个错误是位号重复错误,看这个元件位号为J1。那么层次原理图的其他子图纸,可能有多个J1的位号,将J1位号都找出来并改过来。在设计节点上右击菜单上选Find:

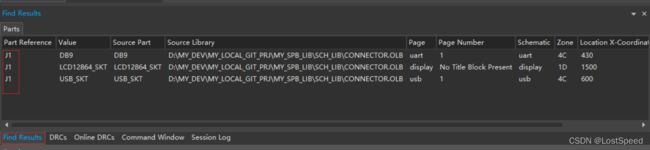

在IDE右面的查找面板上输入J1, 并勾上所有可能的选项,点击查找:

看IDE下面窗口,如果找到了任何目标条目,都会显示查找结果窗口:

可以看到,居然J1的位号有3个…手误的不忍直视…单击每一个重复位号,跳转到具体元件后,按照自己规划的实际正确位号填写修正。将所有元件位号都按照设计实际位号填好后,再DRC, 此种错误完全消失。

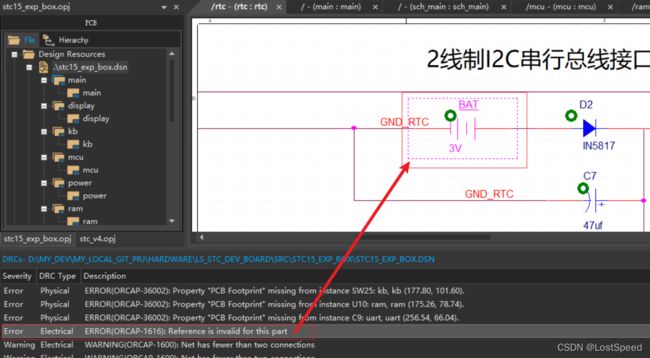

ERROR(ORCAP-1616): Reference is invalid for this part

测试用例:

这个元件的原理图库中的元件也叫BAT:

![]()

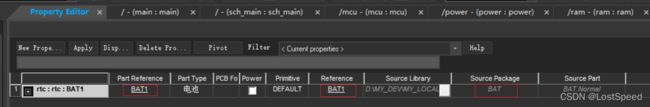

改成BAT1(让元件位号和原理图库元件名称不一样),如果这个元件位号非要叫做BAT, 那么将原理图库中的元件名改了也行(e.g. BATTERY)。从元件属性上看,就是要保持 "Part Reference"属性值和 “Reference”属性值和元器件封装名称不一样才行。改了元件位号, "Part Reference"属性值和 “Reference”属性值都变的和位号值一样了:

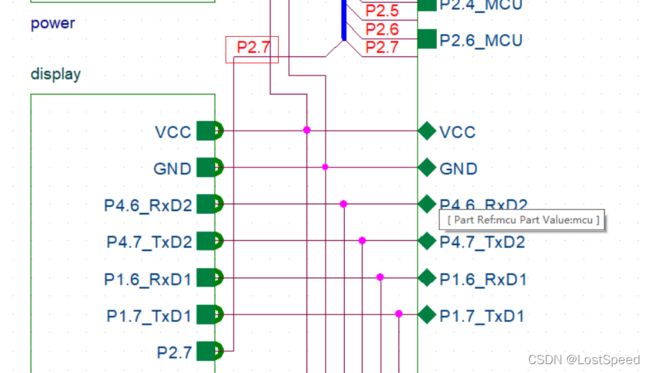

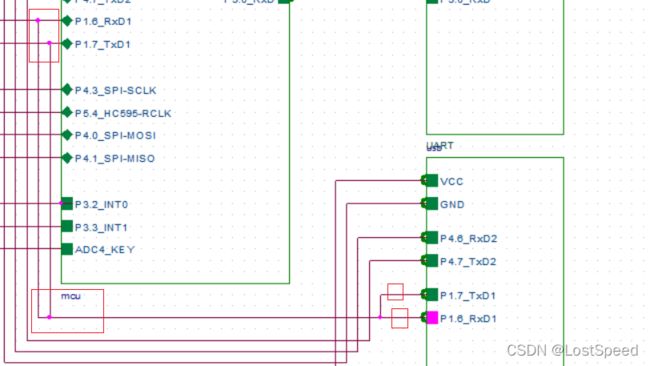

WARNING(ORCAP-1638): Port has no matching pin in part instance above

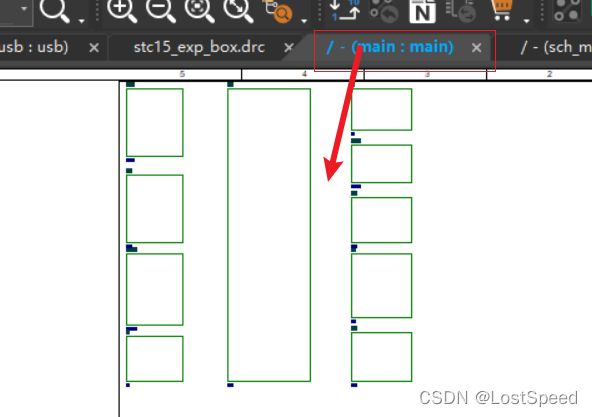

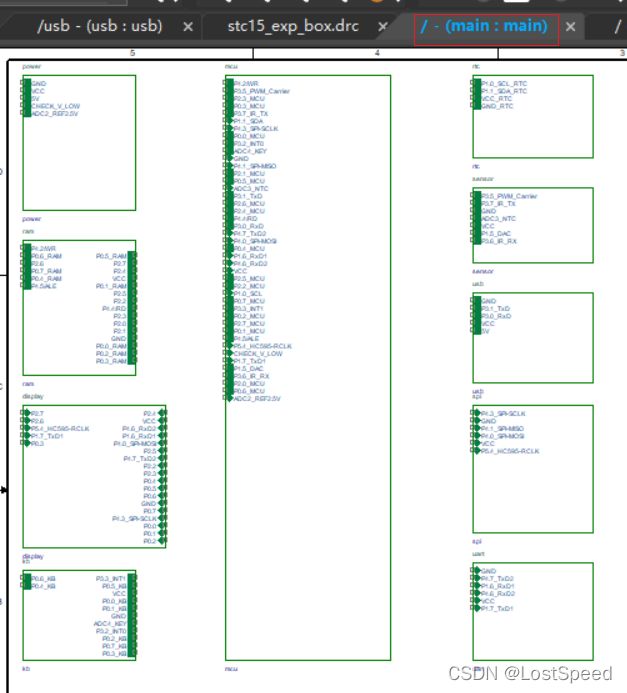

这个警告是说,子图端口没有连接到顶层图纸上的同名port。差不多就是说,port也要连接2张子图中的同名网络才行。如果这个port是在子图中孤立的port,或者顶层图纸中只有一个port, 就会出现这种警告。我现在画的设计图是测试用的,只新建了顶层图纸,然后分别生成底层子图,然后将需要排错的工程中的对应子图拷贝到对应子图。顶层图纸上并没有同步子图port, 所以会有这个警告。从底层子图回到顶层图纸:

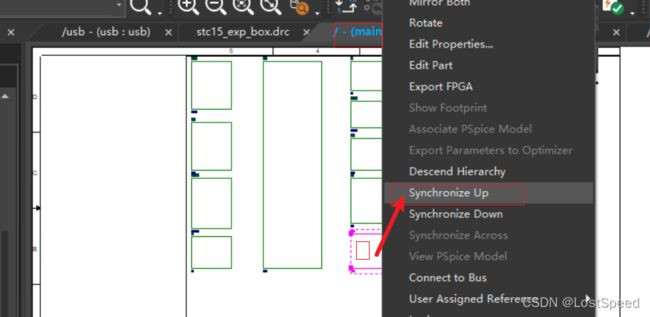

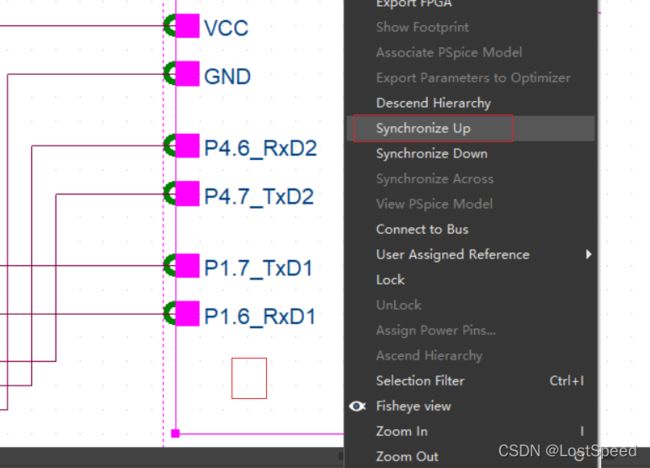

从顶层图纸上同步底层子图的port,分别点击顶层图纸上的每一个子图符号,然后右击选从子图到顶层图纸更新:

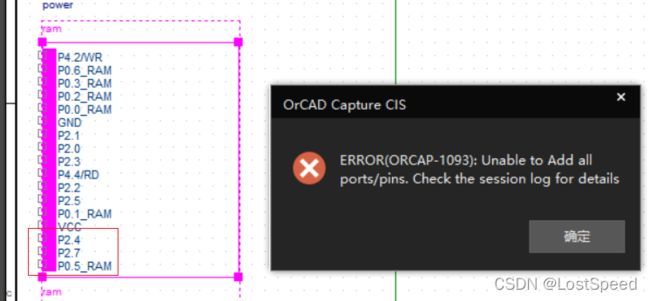

如果子图的高度方向比要更新的接口数量少,就会出现如下报错,说子图端口更新失败:

这时有2种解决方法:

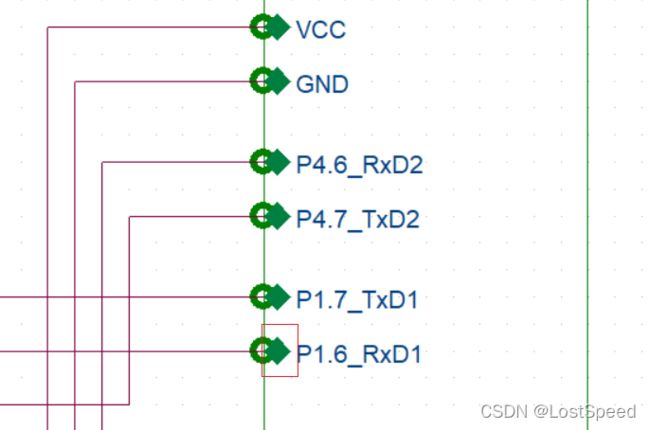

将子图符号的高度方向拉长到足以容纳下实际字符端口的数量,然后再更新,将上图左下角已经更新好的子图端口分别选中,用鼠标拖动到字符符号右边空白的边界上,这样子图符号左下角就空出地方出来了,可以继续更新字符端口。每个子图符号都更新完子图端口的顶层图纸如下

再DRC, 此种警告消失。

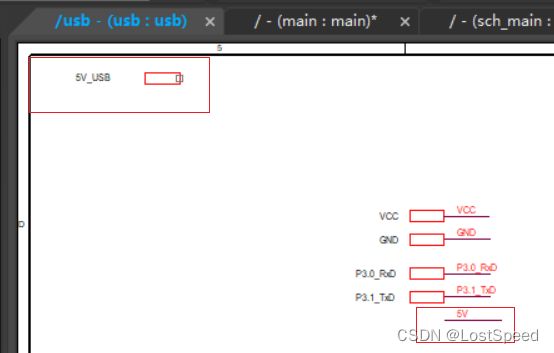

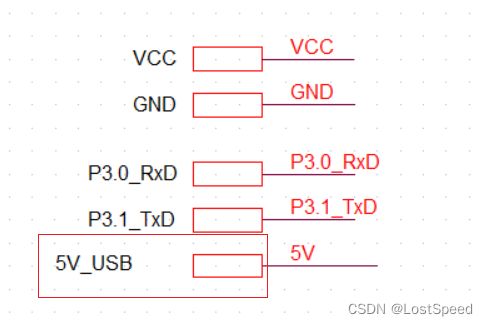

WARNING(ORCAP-1629): Multiple Hierarchical Ports of same name exist across Hierarchical Blocks

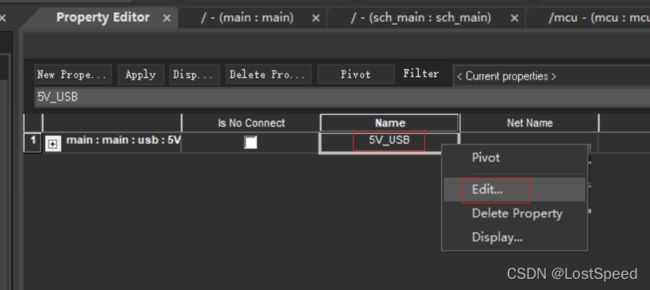

这个警告是说,一个图纸中的多个字符符号,不能有相同的子图pin名称。那将不同子图符号中的同名子图pin改成不同名的子图pin名称就行:

双击"5V"的子图pin, 在弹出的属性框中, 将5V改成"5V_USB":

双击"5V"的子图pin, 在弹出的属性框中, 将5V改成"5V_USB":

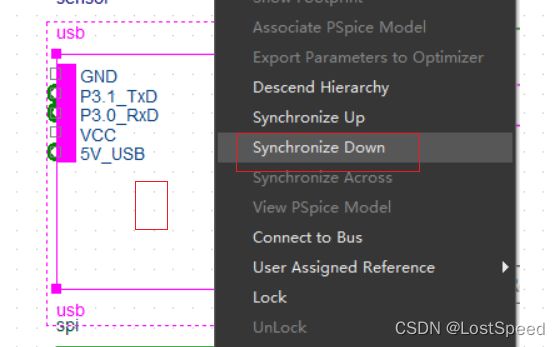

更新子图符号的子图pin到子图图纸的子图端口:

从顶到下更新后,自动跳到了子图。卡到子图port位置变了,在坐上角。将更新后的子图port放到正确的位置:

再DRC, 此警告消失,但是出了一个新警告(1589), 这个警告是说同一个连接有多个网络别名,容易引起短路。解决方法是将子图中所有的5V改成5V_USB, 这个警告先放着,稍后解决。

将其他的1629警告先都改了,在顶层图纸上的不同子图符号中的同名字符pin都改成不同名称,然后更新到子图(或者在子图中将子图prot改名,然后会顶层图纸更新),全部改完后,再DRC, 此警告消失。

WARNING(ORCAP-1589): Net has two or more aliases that might lead to a short. Ensure nets are not shorted together or nets do not have two or more aliases. This message is displayed because ‘Report all net names’ is set in Design Rules Check dialog.

这个警告原因是,我设置了网络不能重名的选项。在不同图纸上的相同电气连接的网络名称相同,按理说是可以。本来同名网络名称就是一个网络么,为啥要在不同子图中设置为不同的网络名称:

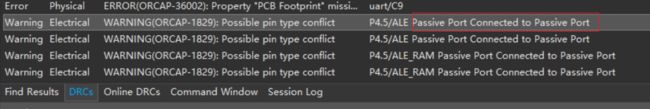

WARNING(ORCAP-1829): Possible pin type conflict

这个警告可能是摆子图端口时,一样的端口摆了2个。因为图纸大了,子图数量多时,可能会将端口摆重复。看看警告信息:

可以看到 Passive Port Connected to Passive Port 的提示信息。这说明是子图port和子图port之间有冲突。双击警告信息,跳到出错处看看具体情况:

可以看到相同的子图port由于手误,摆了相同的2份。将左边要导出到顶层图纸的子图port去掉一份,只留唯一的一份。再DRC, 此类警告消失。

初步完成原理图DRC检查

我将昨天DRC检查,巨多报错的原理图工程的错误已经在临时工程上消掉了除封装之外的全部错误。准备在昨天的正式图纸上试试,看看还有没有其他DRC报错。如果以后遇到其他DRC报错,如果能解决,一并补充到此文档作为总结。

补充 - 2022_0331_1206

工程另存之后文件输出文件夹中文件位置不对的问题,如果工程进行硬拷贝,很多工程文件都要自己改名,有可能改不动。SPB17.4有工程另存的功能:

另存过程中,还可以选择,是否将参考设计文件一并拷贝到新目录,指定另存的工程名称。但是另存后,输出文件夹中的文件名和位置,用的还是原始工程的:

这时,需要关闭工程,用文本编辑软件打开.opj, 搜索并替换原始工程的关键字即可。

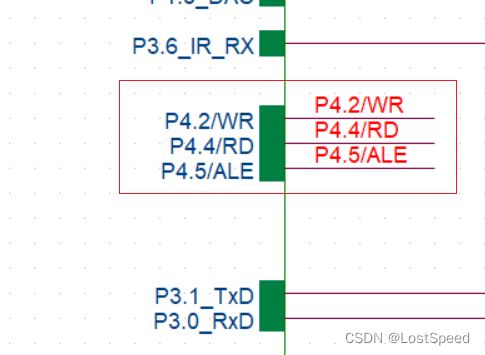

ERROR(ORCAP-1844): The tap may not be connected to the bus or the tap may be connected to a bus with a different base name.

这个错误是使用总线(bus)时,bus_entry2边的网络标号(bus上的网络标号,引脚上的网络标号)名称不匹配引起的问题。bus名称正常用法是:只能是网络序号连续的情况.e.g. DAT0, DAT1, DAT2 这样的网络名称 可以连接到总线 DAT[0…2],bus_entry两边的网络标号都没手工标注,也会出现这种报错。

测试用例:

只要bus_entry两边的网络标号都手工标注了,且元件引脚引出线的网络标号属于bus网络标号(集合)中的一种,这个警告就没了。

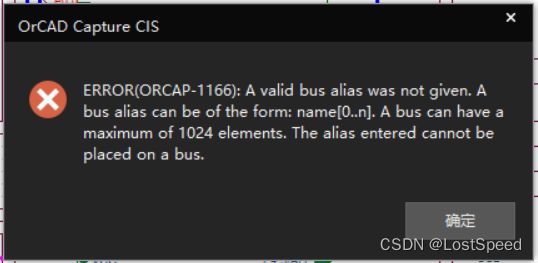

将一个合法的bus名称改成不合法的(e.g. DAT[0…7] 改为 DAT/ALE), 会有报错提示,我们可以看到bus的合法名称规则是啥:

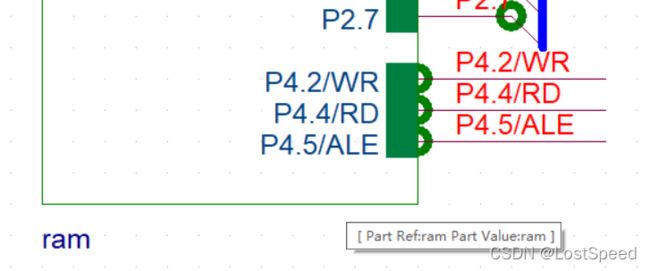

从报错信息可以看出,bus的命名必须是 name[0…n], 且n最多是1023。从bus的命令可以看出,如果网络标号不是一个集合中的网络标号,是不能通过bus entry连接到bus的。e.g. P4.5/ALE 这种,如果想连接到同名的P4.5/ALE, 只能单独拉线连接。而不能通过bus entry 连接到bus。

测试用例

改好的2个子图符号如下,再检查,这2个子图符号这里,就没有这种警告了:

测试用例:

下面的局部也有ORCAP-1844报错。原因是左边的P2.7的引出线上没有标注网络标号P2.7:

修正如下,再进行DRC, 此处就没有ORCAP-1844报错了:

WARNING(ORCAP-1603): Type of pin above does not match the pin type of corresponding port below

这个警告说的是 :子图pin类型不匹配

测试用例

可以看到,由于画图时的手误,将同一张子图的不同子图pin 连接到一起了。尝试将不同的子图pin的短路分开,如下:

再DRC还是有这个错误。尝试更新子图pin(从子图到顶层图):

更新完,可以看到子图pin由方形变成了菱形。这也许就是子图pin的type:

再DRC, 此警告消失。既然存在子图pin type不对,尝试对所有顶层图纸的子图pin都从下向上更新一次。

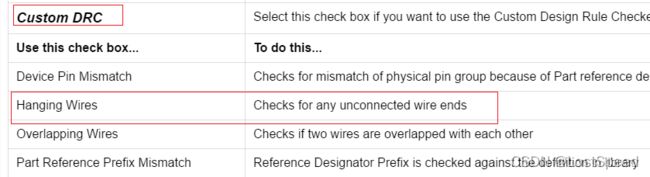

Custom DRC 警告

为了严格检查,我勾选了全部的Custom DRC选项,结果消不掉警告。只好去了2项:

如果不去掉这2项,在.drc警告信息中,可以看到 ”Custom DRC“, “Hanging Wires”, “Part Reference Prefix Mismatch” 这样的警告字样,因为是可选DRC选项,并不会在DRC结果窗口显示这些告警信息,但是会在原理图上有密密麻麻的绿色DRC错误的小环指示。这2个警告可以去掉的原因:

Hanging Wires

Checks for any unconnected wire ends

只要线的2端没连到元件(即使标注了网络标号),也会有警告。这个警告选项,只适合原理图全部用线来连接所有器件的情况。大部分原理图,会采用线的一边连接器件,一边拉出一条线,上边放一个网络标号:

Part Reference Prefix Mismatch

Reference Designator Prefix is checked against the definition in library

这个警告说的是器件位号的前缀和库中不一样,e.g. 库中的位号前缀为U? 画画原理图时,改为了T1. 这应该不算是问题。因为我们可能用了第三方库,或者自己画的库中的前缀位号不合适,需要在原理图中改一下,这个很正常。不能算是警告或错误。

Online DRCs

将DRC窗口的警告和错误都去掉了,但是Online DRCs窗口还有警告。

这说明原理图本身画的没错了。但是和封装有关的警告(其实是错误)还有。

WARNING(ORCAP-2435): Number of pins in footprint

这种错误说明:原理图器件的管教和封装的管教个数不一样或者引脚号码不一致。

例子:

WARNING(ORCAP-2435): Number of pins in footprint 'led-smd_sirab39r1' and instance 'U7' does not match.

原理图3个pin, 封装4个pin:

将原理图库的器件和封装库的器件引脚号码,引脚数量整一致了,这个警告就没了。

ERROR(SPMHNI-176): Device library error detected

从原理图导入网表到PCB时,出现的报错。

#1 ERROR(SPMHNI-176): Device library error detected.

ERROR(SPMHNI-190): Device problem '7SEGX4_LED-SEG-TH_12P-L30_0-W14_0-P2_54-S10_16-BL_7X4'. Package property error: 'VALUE'='7段数码管x4'. Illegal character(s) present in the name or value..

ERROR(SPMHNI-170): Device '7SEGX4_LED-SEG-TH_12P-L30_0-W14_0-P2_54-S10_16-BL_7X4' has library errors. Unable to transfer to Allegro.

好像是元件的值不能是中文的