「数字电子技术基础」6.触发器

目录

- 触发器

- RS触发器

-

- 引入(基本RS触发器)

- 时钟(电平触发RS触发器)

- 主从(脉冲触发RS触发器)

- D触发器

-

- 基本D触发器

- 电平触发D触发器

- 边沿触发D触发器

- JK触发器

-

- 脉冲触发JK触发器

- 边沿触发JK触发器

- T触发器和T'触发器

- 触发器的状态方程

- 不同触发器间的转换

触发器

触发器(Flip-Flop),从英语单词来看就是“翻转器”的意思。首先,数字器件只有01两种状态,因此数字电路工作的过程也就是01之间翻转的过程。为什么叫触发器呢?因为这个元件进行翻转,需要一个触发。按照触发的条件不同,可以将触发器分为无触发、电平触发(时钟触发)、脉冲触发、边沿触发。

不过比起触发方式,更加通用的分类方法是按照逻辑功能。这样可以分为RS、JK、D、T触发器。

RS触发器

R->Reset,清零

S->Set,置位

输入置位和清零信号,触发器给出相应的动作。

引入(基本RS触发器)

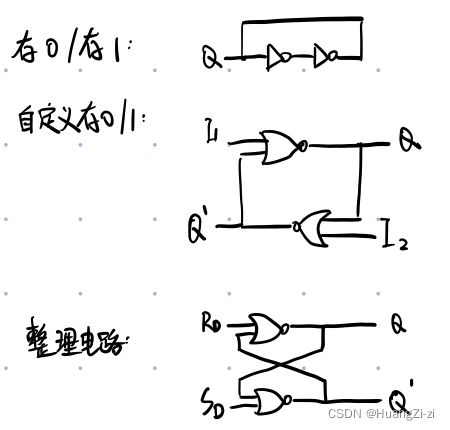

上图:如果要存一个状态(0或者1),可以采用两个非门串连。由于数字电路具有稳定性,最终的输出总会稳定到高质量的0或者高质量的1。

中图:但是只用两个非门的话到底存了0还是存了1呢?实际上是随机的。为了能够自主控制,将非门换成或非门。如果I1和I2输入0,那么与非门就退化成非门了。如果有输入1,也就会有相应的Q和Q’的输出。

下图:这样就构成了基本RS触发器

用Q来表达现在Q的状态,Q*表达Q的下一个状态

Rd->reset directly

Sd->set directly

不需要触发,可以直接改变输出。

详细的电路分析这里就不再赘述了。RS触发器的特性就是,R和S都无效时保持,只有一个有效时对应置位和清零,1两个都有效是应该避免的状态,因为可能产生不定。

除了用或非门,还可以用与非门构成RS触发器。

观察这个电路,发现用了非门,这是为了保持高电平有效。但实际上也会有低电平有效的电路。这里就展示封装好的原理图了。

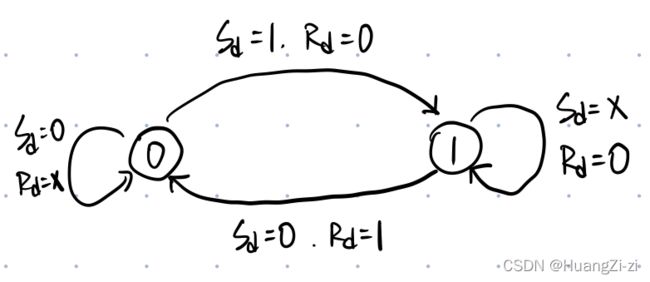

状态转换图

在圈里写的是Q的状态,从一个状态指向另一个状态,这条线上的是发生这个转换的条件。

在圈里写的是Q的状态,从一个状态指向另一个状态,这条线上的是发生这个转换的条件。

状态方程

Q ∗ = S + R Q ‾ S R = 0 Q^*=S+R\overline Q\newline SR=0 Q∗=S+RQSR=0

时钟(电平触发RS触发器)

看了之前的基本RS触发器结构发现,只要输入发生改变,输出就会有相应的变化,那也就意味着不论有什么干扰,都会被反应到输出上面。所以我们想要控制它什么时间工作,什么时间不工作。也就是引入一个控制信号。控制不同的模块协同工作的脉冲信号就叫做时钟信号。

通过与非门控制,当时钟为高电平,与非门退化成非门。而当时钟为低电平,与非门就不通了,达到了控制的作用。

不管怎么改,这些我们接触到的触发器核心都是RS触发器,也就是可以直取首级,通过异步SD和RD直接清零和置位的。不过有的时候为了简便就不写了。

这样一来,解决了一半的干扰问题,也就是时钟的低电平区间,输出稳定了,但是时钟的高电平区间依然面临干扰。而且SR=0的限制也并没有解除。

主从(脉冲触发RS触发器)

下面这个故事应该能有助于大家理解主从结构。

假如你是一个面试官,面试一个人安排了十分钟。但是面试者可能会提前到,直接推门进来打断前面的面试。也可能打开门的时候请进来的是一个路过的路人。

为了保证面试尽量少的被干扰,可以采取这样一种方式:

设置一个只能容纳一人的等待室。那么等你下次开门的时候进来的就一定是等待室里面的这个人了。

这就是主从结构的要点:用一个触发器担任等待室,接收外部的信号。用另一个触发器担当输出,输入经过前级触发器处理过的信号。

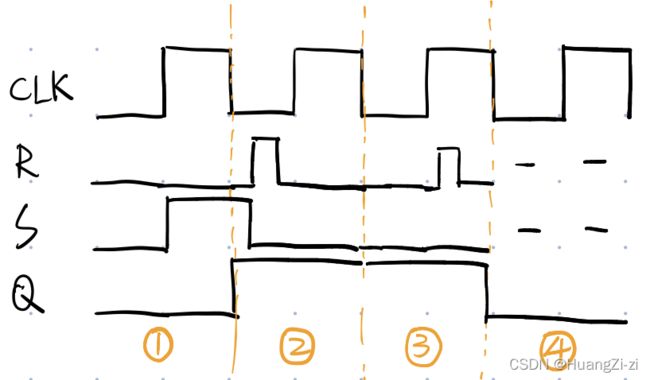

观察这个电路图,当CLK处于高电平,前面的SR触发器(主触发器)处于接收信号的状态,也会有产生相应的相应。但是后面的SR触发器(从触发器)输入为00,处于保持状态,输出稳定。当CLK处于低电平,前面的SR触发器处于保持状态,外部扰动不影响输出,这样后面的触发器就能取道稳定的数据,保持输出稳定。

解释一下为什么这样构成的叫做脉冲触发。从CLK的上升沿开始,到CLK的下降沿,这是一个脉冲。在这个脉冲内,主触发器接收信号。直到CLK的下降沿,从触发器输出新状态。在这个脉冲周期内的所有输入都有可能影响输出。举个例子:

在(1)段,CLK高电平整个过程中都是置位有效清零无效,因此CLK下降沿Q输出1;

在(2)段,CLK高电平整个过程中都是置位无效清零无效,因此CLK下降沿Q保持之前的状态;

在(3)段,虽然CLK下降沿瞬间是保持,但是由于在脉冲周期内,是先清零,再保持,因此CLK的下降沿Q将输出0;

RS触发器的常见结构就这些了,最终发现输入的限制仍旧没有解除,需要在输入的时候格外注意,保证SR=0。为了解决输入的限制,采用了两种新的思路。

D触发器

D->Data(也有一个版本叫Delay)

输入数据信号,将这个数据信号输出(因为有传输延迟时间所以Delay也挺贴切的)

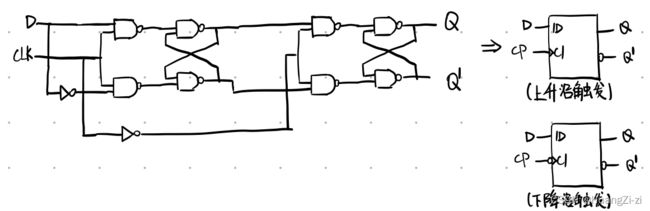

如果要保证SR=0,那么我让S=D,R=D’,这样两个量永远处于相反状态,限制就解除了。以这个思路制作D触发器。

基本D触发器

具体是不是叫这个名字还有待考证。总之就是没有时钟的D触发器。在实际中应该是完全见不到的。

电平触发D触发器

满足:Q=D(clk高电平)

在满足时钟控制的前提下解决了输入限制的问题。但是也带来了新的问题:RS触发器输入00代表保持。而由于D触发器的结构,00是不可能出现的。也就是失去了保持的功能。要想保持,就必须不断输入相应的信号。

边沿触发D触发器

这个触发器也是主从结构,但是怎么就变成边沿触发了呢?因为D触发器是没有保持功能的。所以在CLK边沿来临的时候,输入是什么,输出就是什么。它和脉冲触发的区别就在于脉冲触发需要看整个脉冲周期,而边沿触发只要看边沿的瞬间就可以了。

这里补充一个知识点:延迟的存在

在(2)段,虽然上升沿时D也变化,但是由于延迟的存在,我们认为上升沿采样时D还没有来得及变化。也就是当输入和触发同时变化时,取输入的原态

JK触发器

关于JK两个字母的由来有许多版本。其中比较可信的是,某个大佬在表达触发器输入的时候,采用了AB,CD,EF,GH,JK这一组字母(I可能留给其他的输入了)因此也就有了J输入和K输入的概念。

JK触发器采用和D触发器不同的设计理念。D触发器是从输入下手,杜绝了同时输入有效的情况。而JK触发器则是更改了电路结构,通过引入反馈,使得同一时刻只有一个输入有效,而另一个输入无效。

脉冲触发JK触发器

虽然最外面的JK输入是11,但到内层,RS的输入只存在00,01,10的情况。解决了限制。

不过这也引入了新的问题。不管JK触发器处于什么状态,它要么保持,要么向相反方向翻转。但是如果受到干扰,意外翻转了,那么是没有办法再翻转回来的。因此抗干扰的能力比较弱。

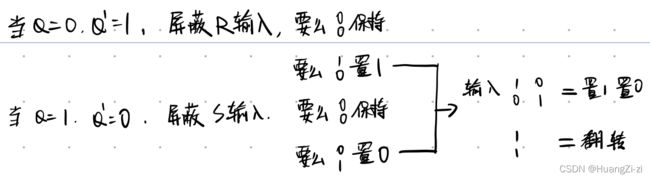

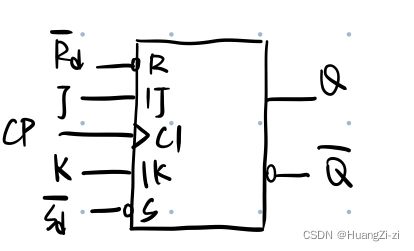

边沿触发JK触发器

内部结构比较复杂,也不需要掌握只需要识别>符号代表边沿触发,不取反表示上升沿,取反表示下降沿就可以了。

T触发器和T’触发器

T->Toggle(翻转)

不太重要的两个触发器,内部结构也不再介绍。左边是T,右边是T’

触发器的状态方程

这个内容非常重要。前面的电路结构,触发方式都是背景知识。真正使用触发器的时候,是使用它的状态方程的。

不同触发器间的转换

首先明确一点:所有触发器都可以由JK触发器转化而成

这里举两个例子:

1.用D触发器加逻辑门构成JK触发器

这代表了第一种思路:通过状态方程,求解触发器的输入。有可能有一些简单的转换是不需要外加门电路的,直接将输出引回某个输入就可以了。

2.使用与门和D触发器构成T触发器