汽车芯片的可靠性设计:控制亚稳态,提升稳定性

【作者简介】Dr. Roy 复睿微 IC后端工程师,南开大学与韩国首尔国立大学联合培养博士。博士期间发表高水平学术期刊论文多篇,其中一作一区封面文章2篇;授权发明专利5项。同时,在先进工艺大芯片的静态时序分析、芯片设计流程提效优化、SPICE仿真等领域拥有丰富的工作经验。

【摘要】汽车电动化、智能化、物联化对汽车电子的安全性提出了更高的要求。为了避免不可靠数据的产生与传播而造成芯片功能安全风险,设计者可以采用同步器处理跨时钟域信号交互的问题。这需要设计者对亚稳态的产生与恢复、同步器的原理与表征方式有更加全面地认识。

【关键词】汽车电子、可靠性、同步器、亚稳态

引言

在人工智能、5G、先进半导体等技术引领下,汽车电动化、智能化、物联化发展已成必然趋势。从需求端来看,随着消费者对安全舒适、经济稳定、娱乐交互等方面的需求提高,消费者对汽车产品智能化的需求显著增加,驱动汽车不断朝电动化、智能化和物联化方向发展,汽车电子在汽车整车中的占比越来越高。然而,与消费电子相比,汽车电子关系到驾驶员和乘客的生命安全,同时也面临更加严苛的使用条件。因此,人们对于车载芯片的产品质量要求更为严格。

芯片作为汽车的核心控制部件之一,为了适配不同的应用场景,通常有许多并行运行的独立功能或计算单元,而每个单元通常使用自己的局部时钟。因此,对于大规模的芯片来说内部的时钟域数量十分庞大。

当不同时钟域之间存在数据交互时,为了降低亚稳态的产生概率,保证可靠的数据传输,设计人员通常会采用插入同步器的方式进行时钟数据的同步处理。这些同步器一般由多个级联的主从触发器构成;通过增加触发器的级数可以大大提高芯片可靠性。但是,同步器会增加数据传输的延迟,因此需要在增加的延迟和同步器可靠性之间进行权衡。表征同步器电路以估计其可靠性对于帮助做出此权衡决策非常重要。

亚稳态

什么是亚稳态?从字面上看,亚稳态是指一种“不太稳定”的状态,轻微的扰动就会使系统失去状态。在数字电路中除了逻辑“1”和“0”状态以外,还有一个中间状态--处于“1”和“0”之间未能被正确识别的状态。该状态是由于锁存器的固有反馈设计,输出可能会漂移一段时间。

从设计的角度来看,亚稳态可能会产生以下后果:

1. 如果不稳定的数据被馈送到设计中的其他地方,可能会导致局部高电流,最坏的情况下甚至会烧毁芯片。

2. 不同的扇出锥可能会读取不同的信号值,并可能导致设计进入未知的功能状态,从而导致设计出现功能问题。

3. 目标输出可能会稳定到新值,也可能会返回到旧值。但是,传播延迟可能会很高,从而导致时序问题。

以互耦反相器环为例简单阐述一下亚稳态的产生与恢复过程。图1(a)和(b)分别表示互耦反相器的原理图和晶体管级互连示意图,第一个反相器的输入由第二个反相器的输出驱动,反之亦然。当顶部反相器的输出(N2)为“1”时,M4和M1导通。同样,当输出为 “0” 时,M3 和 M2 导通。如果输出反相器的电压保持在 VDD 或 GND 以外的任何值,则 M4 和 M1 会尝试将输出拉向 “1”,而另外两个晶体管将其拉向 “0”。最终设定值(”0“ 或 “1”)取决于其初始值拉力的强弱。但是,如果 M4 和 M1 的初始拉力组合等于 M3 和 M1,则输出不会移动。在维持平衡之前,输出可能会保持在该水平一段时间。

如图1(c)所示的输出曲线,如果系统受到扰动,强行改变了输出值,即使是很小的值,它也会经过反馈调节,输出会稳定在 “0” 或 “1”,具体取决于强制改变的方向。这种干扰可能是由于外部因素(例如外部强制电压)或内部因素(例如串扰)造成的。所以,如果任由它自己脱离亚稳态,脱离亚稳态的时间是未知的。

图1. 互耦反相器(a)原理图,(b)晶体管互连图,(c)输出曲线

数字电路中的所有寄存器都定义了信号时序要求,每个寄存器需要在其输入端正确捕获数据并产生输出信号。为确保可靠运行,寄存器输入必须在时钟边沿之前稳定至少一段时间(寄存器建立时间,tSU),并在时钟边沿之后稳定最短时间(寄存器保持时间,tH)。如果数据信号转换违反了寄存器的 tSU 或 tH 要求,则寄存器的输出可能会进入亚稳态,如图2所示。在亚稳态下,寄存器输出在高电平状态和低电平状态之间的某个值上徘徊一段时间,这意味着输出到定义的高电平或低电平状态的转换延迟会超过时钟端到输出端的延迟要求( tCO)。

图2. D触发器的(a)输入与(b)输出,其中信号S2, S3,S4会产出亚稳态输出[1]

同步器与跨时钟域路径

在同步系统中,设计者可以通过合理的时序约束文件对芯片进行约束,输入信号必须始终满足寄存器时序要求,因此不会出现亚稳态,如图3(a)所示。但是由于芯片覆盖场景越来越多,芯片不可避免的会出现跨时钟域路径。当信号在不相关或异步时钟域中的电路之间传输时,通常会出现亚稳态问题,如图3(b)所示。在这种情况下,设计人员无法保证信号满足 tSU 和 tH 要求,因为信号可以相对于目标时钟随时到达。但是,并非每个违反寄存器 tSU 或 tH 的信号转换都会导致亚稳态输出。寄存器进入亚稳态的可能性和返回稳定状态所需的时间取决于用于制造设备的工艺技术和操作条件。在大多数情况下,寄存器将快速返回到稳定的定义状态。

图3. 同时钟域路径(a)与跨时钟域路径(b)电路示意图

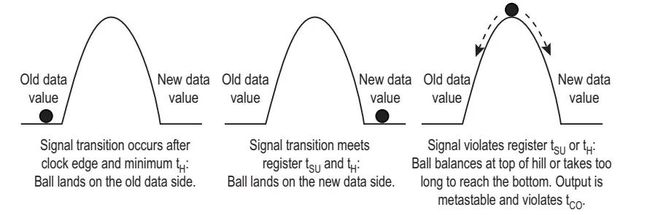

如图 4所示,在时钟边沿对数据信号进行采样的寄存器可以看作是一个球落在山上。山的两侧代表稳定状态——在信号转换后的旧数据值和新数据值——以及山顶代表亚稳态。如果球落在山顶,它可能会在那里无限期地保持平衡,但实际上它会稍微落到山顶的一侧并滚下山坡。球离山顶越远,它越快到达底部的稳定状态。如果数据信号在时钟边沿和最小 tH 之后转换,则类似于将球掉到山的“旧数据值”一侧,并且输出信号在该时钟转换期间保持原始值。当一个寄存器的数据输入在时钟边沿和最小 tSU 之前转换,并保持在最小 tH 之后,这类似于将球落在山的“新数据值”一侧,输出达到稳定的新状态足够快以满足定义的 tCO 时间。但是,当寄存器的数据输入违反 tSU 或 tH 时,就类似于将球扔到山上。如果球落在山顶附近,则球到达底部的时间太长,这会增加从时钟转换到超过定义的 tCO 的稳定输出的延迟。

图4. 小球落在山上类比时钟与数据的信号相位关系[2]

为了保障芯片正常工作,设计者通常会采用插入一种被称为同步器的特殊结构来避免亚稳态问题。常用的同步器结构都是多级同步寄存器,允许同步器有足够的时间振荡并稳定下来,确保在目标域中获得稳定的输出。如图5展示了一个简单跨时钟域路径,其中DFF2与DFF3组成了两极同步寄存器用于同步信号B。这种结构在设计中主要用于单比特和多比特控制信号以及单比特数据信号。多位数据信号需要其他类型的同步方案,例如 MUX 再循环、握手和 FIFO。

图5(b)阐述了两级同步器的同步过程,由于第二级寄存器DFF3的存在,在下一个clock2时钟上升沿DFF3捕捉到信号B并识别为高电平,输出信号Sync B,但是在下下个clock2时钟上升沿时,信号B已从亚稳态电平恢复到稳态电平即正确的低电平,那么经过DFF3再次采样会输出和B完全同步的Sync B信号,也就是解决了亚稳态问题[3]。这种额外的同步触发器提供的额外时间增加了亚稳态解决的可能性,并降低了设计失败的可能性。与此同时,同步器的成本则是增加了设计延迟。

图5. 两级同步器电路结构示意图(a)及其时序图(b)

同步器电路的可靠性

同步器降低了亚稳态事件导致系统故障的可能性;同步器的级数越多,电路的可靠性越高。然而,在任何非纯同步的系统中,永远无法完全避免亚稳态问题,而且同步器的级数也不能无限制的增加。设计者通常使用平均故障间隔时间 (MTBF) 指标来量化由于亚稳态导致系统故障的可能性[4,5]。MTBF值越大,芯片的可靠性就越高。

其中fd,fc分别表示数据时钟域和接收时钟域的频率;t0表示寄存器的时间窗口即(tSU+tH);表示信号电平重新恢复位逻辑可识别状态所需的特征时间常数,可以通过仿真得到。

而对于N级同步寄存器,其MTBF可表示为:

其中第一项即分母项可表示亚稳态的产生阶段;第二项即分子项是关于同步器级数、时钟周期等因子的一个指数函数,可表示亚稳态的恢复阶段,表示第i级寄存器的时钟端到输出端之间的延迟,表示第i+1级寄存器的建立时间要求,表示金属网络上的延迟。MTBF与正相关,与其他有关因子负相关。

考虑到最悲观的场景,各级同步器之间的建立时间检查刚好满足预设的裕量要求,即setup slack=0。下表列出了特定场景下的MTBF值与同步器级数之间的关系,不难发现,同步寄存器的级数增加,能大大的提高芯片的可靠性。

表1. MTBF与同步器级数对应关系示例

N级同步寄存器的MTBF公式可用于指导芯片设计:

1. 同步器类型的选取方面,需要综合考虑同步器单元延迟及其时间窗口大小;

2. 同步器级数设计方面,需要根据芯片对MTBF可靠性要求进行预估;

3. 后端物理实现方面,需要预设时序裕量、时序检查、同步器类型检查、MTBF计算等操作。

结语

芯片的可靠性是一个永恒的话题,亚稳态的产生虽然无法避免,但是设计者可以通过反馈机制、冗余设计等方式保证关键功能不出错。本文介绍了亚稳态的产生过程,并列举了一种最简单的减小亚稳态影响的方法,即同步器链。除此以外的握手反馈机制、异步FIFO格雷码等方式可能会消耗更多的资源,需要设计者对各种方式的优劣势与芯片可靠性需求进行权衡决策。

reference

1. Seo, Hwa-Jeong, and Ho-Won Kim. "Always Metastable State True Random Number Generator." Journal of information and communication convergence engineering 10.3 (2012): 253-257.

2. Altera Corporation, “Understanding Metastability in FPGAs-White Paper”:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/wp/wp-01082-quartus-ii-metastability.pdf

3. Cummings, Clifford E. "Clock domain crossing (CDC) design & verification techniques using SystemVerilog." SNUG-2008, Boston (2008).

4. Golson, Steve. "Synchronization and Metastability." SNUG Silicon Valley (2014).

5. Reiher, Justin James. Synchronizer analysis and design tool: an application to automatic differentiation. Diss. University of British Columbia, 2020.

关于复睿微

复睿微电子植根于创新驱动的文化,通过技术创新改变人们的生活、工作、学习和娱乐方式。公司成立于2022年1月,目标成为世界领先的智能出行时代的大算力方案提供商,致力于为汽车电子、人工智能、通用计算等领域提供以高性能芯片为基础的解决方案。

目前主要从事汽车智能座舱、ADS/ADAS芯片研发,以领先的芯片设计能力和人工智能算法,通过底层技术赋能,推动汽车产业的创新发展,提升人们的出行体验。

复睿微电子拥有一支业内顶级,能够全流程覆盖芯片的研发设计、解决方案、市场销售、服务支持等完整架构的车规级大算力芯片团队。团队集聚全球顶尖数字芯片人才,核心成员拥有在海内外领先的优秀企业的工作经验。