【Mitigating Voltage Attacks in Multi-Tenant FPGAs 论文笔记】

减轻多租户FPGA中的电压攻击

- 摘要

- 引言

- 内容

-

- 背景和相关工作

- INTEL STRATIX 10 FPGA上的PDN攻击

- Stratix 10 PDN特性

- 定位电压下降

- 片上监控和攻击抑制

- 结论和未来工作

-

- 结论:

- 未来工作

作者:GEORGE PROVELENGIOS, University of Massachusetts Amherst, MA, USA

DANIEL HOLCOMB, University of Massachusetts Amherst, MA, USA

RUSSELL TESSIER, University of Massachusetts Amherst, MA, USA

摘要

恶意的云FPGA用户可以精心设计故意浪费电力的电路,并将其部署以导致拒绝服务和故障注入攻击。

FPGA云服务使用的主要防御策略包括检查用户提交的已知的严重消耗电力的电路结构设计,但是时长会有新的恶意电路结构被设计。

本文的贡献:

- 评估了通常不会被FPGA云计算供应商强加的设计规则检查所标记的电路功耗技术

- 识别定位基于功率浪费器的电压攻击源,在导致板重置之前阻止攻击

引言

随着FPGA在逻辑容量和性能方面的增长,其在各种应用程序中的使用也急剧增加。而所有基于FPGA的核心逻辑共享相同的配电网络(PDN)。研究表明,攻击者引起的芯片上电压降可以驱动基于FPGA的电路板复位[14]或在相邻电路中引发时序故障[1,20,24,27]。

本文的贡献:

描述并评估了一种 易于实现 很难扫描检测 (隐蔽)功耗电路

检查了Stratix 10设备对我们的隐形功耗电路突然激活的电压响应。

在Stratix 10电路中实现了优化的FPGA 隔离激活电压攻击的位置 传感器网络。

最后,提出并开发了一个实用系统,通过停用FPGA逻辑区域中的时钟信号来实时减轻电压攻击

总结:使用Stratix 10设备,我们扩展了攻击定位技术,并引入了一种机制,以抑制怀疑恶意功耗的区域中的设计时钟。

手稿的其余部分组织如下。

第2节描述了我们的威胁模型和FPGA电压攻击、传感器、监控和缓解技术的背景。

第3节介绍了我们使用片上电压传感器检测功率波动的方法,

第4节介绍了如何使用我们的方法来定位Stratix 10器件中的不稳定性源。

我们的片上电压传感和实时攻击缓解系统在第5节中进行了描述。

第6节总结了手稿,并为未来的工作提供了方向

内容

背景和相关工作

威胁模型:

恶意的第三方知识产权(IP)内核

多个租户同时共享使用FPGA设备

电压操纵攻击:

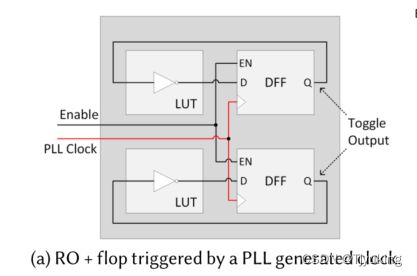

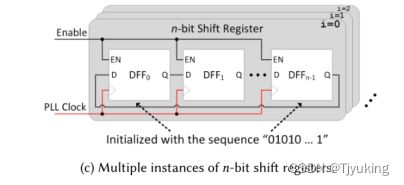

一个租户可能试图通过基于查找表(LUT)的移位

寄存器[41]或故意短路[29]恶意诱导电源电压的局部不稳定,也可能利用电网谐振。

FPGA电压攻击补救方案:(已有的抑制方案)

Krautter等人提出了比特流扫描来定位功耗电路,如RO[21]。

Shen等人[31]在运行时使用了时钟边沿抑制器来抑制用户设计引起的电压尖峰。

Zick等人证明了使用通过管芯收集的电压信息来识别攻击[40]. 提出了抑制攻击的硬件电路,但未进行演示。

WS EC2 F1使用命令fpgadescape local image通过其运行时管理工具提供功率监控,尽管测量仅以每分钟一次测量的时间粒度提供给用户

INTEL STRATIX 10 FPGA上的PDN攻击

电感器导致功率浪费器激活时的大量的瞬时电压降,随后是持续的片上电阻降。

对抗功耗电路

定性和定量地评估了五种这样的同步和异步功率浪费器。

3.1.3基于AES的功率浪费器。

3.1.4评估基于AES的功率浪费器的有效性

三角形的两边表示最慢和最快的路径到达AES浪费的每一轮的时间,循环次数不断增加。时钟周期的开始用左侧的数字标记。三角形的灰色阴影区域描绘了120轮浪费中信号活动发生的时间。红色阴影区域表示信号活动的最大重叠。增加时钟频率会增强链的前几轮中的信号转换重叠

时钟频率为4和50MHz的120轮AES浪费器的每轮功耗。随后的几轮增强了激励,导致每轮功耗增加

Stratix 10 PDN特性

使用基于RO和AES的功率浪费器来评估Stratix 10 的 电压对 瞬时激活浪费器的 反应。由片上电压传感器获取电压信息。

片上电压传感器:

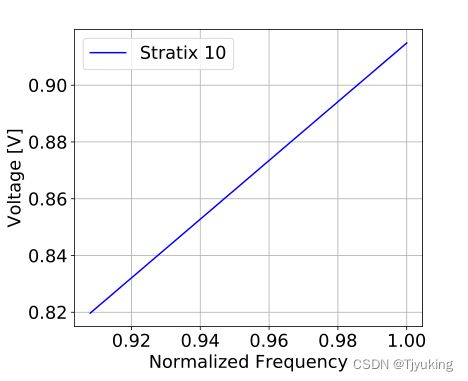

为了确定片上电压,我们使用基于环形振荡器的电压传感器测量PDN的选定位置处的电压。

传感器网络的架构图如下:

频率与电压相关的最终校准曲线如下图

PDN对功耗的响应:

每个传感器测量的电源电压首先下降、下冲,然后稳定回到低于标称0.9 V的稳态电压,距离较远的传感器观察到类似的行为,但电压幅值较小。

图10a所示的曲线图是用30000台基于基于RO的废电器生成的

图10b中的图是用95个循环的基于AES的废电器生成的。

图10c显示了10个循环的基于AES电路的电源电压效应。

定位电压下降

由上部分内容得知,最接近功耗的电路经历最大的电压降,并且电压降越远越小(图10)。电压传感器的空间分布网络可以使资源管理器能够监测电压梯度并识别发生的任何攻击的源。

传感器网络:

通过多次实验和得出电压与Stratix 10装置上攻击中心距离的关系(均以观察到的传感器的最小电压绘制)

尽量减少传感器数量:

研究了使用不同数量的传感器可以精确定位攻击者,使用给定传感器子集的x个位置预测的平均值与利用所有218个传感器的x个定位预测的平均之间的欧几里德距离。每种配置的距离误差以LAB表示。实验表明,传感器数量于距离的关系如下:(当使用所有218个传感器时,70个传感器预测平均预测攻击中心距离预测中心14个LAB)

片上监控和攻击抑制

增强了上部分中描述的电压传感网络,以包括直接补救措施来阻止电压攻击。该网络增加了处理能力和时钟节流电路,用于疑似功耗区域。我们的解决方案是使用一个试图使基于FPGA的电路板崩溃的基于AES的浪费器进行评估的。

方法:在攻击开始时快速响应FPGA电压的显著下降,一旦超过预期的电压降,立即停用相关区域的时钟缓冲器,从而抑制攻击。

5.2.1 时钟区域和传感器

5.2.2阈值校准

5.2.3攻击检测和补救

5.3系统评估

5.4限制

结论和未来工作

结论:

评估了潜在攻击者可以在多租户FPGA平台中实现的功耗电路,对电路的功率效率进行了评估。

描述了一种新的基于FPGA的补救方法,该方法实时收集来自多个租户的电压值,并将时钟停用到任何涉嫌恶意行为的区域。我们的方法可以在21µs内响应攻击,并成功防止了导致电路板复位一系列电压攻击。

未来工作

虽然我们的方法可以抑制电路板复位,但其速度不够快,无法防止相邻电路中的功耗导致的定时故障

本文中讨论的监控系统评估检查了浪费者被限制在单个租户区域的攻击场景,并且可以扩展到考虑具有多个恶意租户的场景。