DC使用教程系列2-时钟的概念与环境接口面积约束脚本

文章目录

- 1、时钟约束的概念

- 2、 DC中的时序约束

- 3、环境、设计规则和面积约束

-

- 3.1 环境设置选择**set_operatting_condition**

- 3.2 设置线负载模型set_wire_load_model

- 3.3 设置驱动强度(set_driving_cell)

- 3.4 设置电容负载(set_load)

- 3.4 设置设计规则约束

- 3.5 面积约束

- 4 官方脚本解读

-

- 1、 set lib_name cb13fs120_tsmc_max

- 2、current_design TOP

- 5、reset_design

- 9、set_clock_uncertainty 0.2 [get_clocks clk]

- 12 supressed_message UID-401

- 13 set_driving_cell -library $lib_name -lib_cell sdcfq1 [remove_from_collection [all _ inputs ] [get_ports clk] ]

- **什么是为设计指定输入端口的驱动强度?**

- 14、 set_input_cell 0.1 -max -clock clk [remove_from_collection [all_inputs] [get_ports clk] ]

- 18、set_output_delay 1 -max -clock clk [all_outports]

- 命令掌握

- 参考文章

时间又拖拖拖,随着追寻DFT的进度,DC的进度在经历了.dynopsys_dc.setup后,就停滞不前了,接下来本文就来介绍DC的约束篇目,在我理解来看vcs是不带时序信息的,而DC就是尽量满足符合实际工作环境来建立一个数字电路的模型,也就是说他会尽量的接近实际的工作环境来建立模型。所以约束,就有用了,不仅仅是环境约束,告诉DC综合出来的芯片要工作在什么环境下面等等。

1、时钟约束的概念

我们必须定义时钟周期(也就是-period这个选项)和时钟源(端口或引脚)(也就是设计中的clk),也可以加上一些可选项(option)来定义时钟的占空因数(duty cycle),偏移(offset/skew)和时钟名( clock name),我们可以通过man create_clock 来查看命令的相关选项。

一旦定义了时钟,对于寄存器之间的路径,我们已经做了约束。我们可以用report_clock命令来查看所定义的时钟以及其属性。然而单单定义一个时钟周期进行约束寄存器与寄存器之间的路径很显然是过于理想的,需要再添加其他的时钟属性,在添加之前,需要知道时钟的偏移(skew)、抖动(jitter)、转换时间(transition)、延时(latency)这几个概念和属性。因为毕竟现实中不是理想的时钟,包括时钟的0->1或者1->0这些跳变都是需要一定的时间。

同步电路的理解

看是不是同步电路,以本博主的观念来看,关键还是看两个domain的时钟是否具备了某种固定关系。当然百度百科上面说的是最简单的一种,情况,有的概念,个人觉得也未必就是对的,毕竟在抄抄抄环境下。所以本博主认为关键还是看两个domain的时钟是否具备了某种固定关系。

比如说,来自于两个时钟源,但这两个时钟源频率一样,相位一样,那就是同步(当然,不太可能两个晶振不可能同时发出相位一样的时钟)。再来,一个时钟经过了分频电路,是2与4倍关系,那每个大周期都固定的包含了小周期的是时钟,所以也是同步,但是三倍频率,那就不同步了,因为你现在的周期,与另一个周期,在每个周期上的相位并不是固定的某种关系。

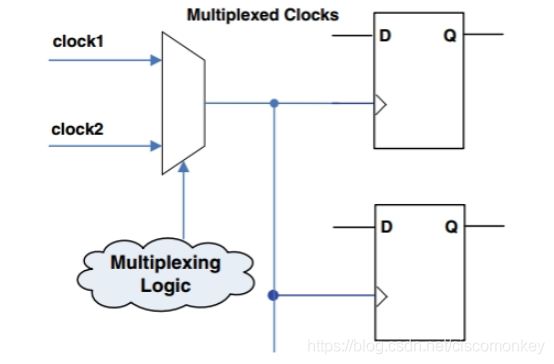

时钟树的概念

时钟树,是个由许多缓冲单元(buffer cell)平衡搭建的网状结构,它有一个源点,一般是时钟输入端(clock input port),也有可能是design内部某一个单元输出脚(cell output pin),然后就是由一级一级的缓冲单元搭建而成,具体的多少级,根据你的设置以及所使用的单元而定,目的就是使所用终点的clock skew(一般最关心这个)、insertion delay以及transition了,满足设计要求

①时钟的偏移(skew):时钟分支信号在到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。此外,时钟skew与时钟频率并没有直接关系,skew与时钟线的长度及被时钟线驱动的时序单元的负载电容、个数有关,时钟的偏移如下图所示:

②时钟抖动(jitter):相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动,如下图所示:

![]()

·随机抖动的来源为热噪声、Shot Noise和Flick Noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动;

·固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。

jitter与时钟频率无直接关系

时钟的偏移和时钟的抖动都影响着时钟网络分枝的延迟差异(相位差异),在Design Compiler里面,我们用时钟的不确定性(uncertainty)来表示这两种情况的影响。

③时钟的转换时间(transition) :时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间,这个时间并不是如左下图所示那样完全没有跳变时钟的,而是像下图那样,时钟沿的跳变时间就是时钟的转换时间。

时钟的转换时间与与单元的延时时间(也就是器件特性)还有电容负载有关

④时钟的延时(latency) :时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency)

时钟源延迟(clock source latency),也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间,上图是3ns。

时钟网络的延迟( clock network latency)是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency),上图是1ns。

我以前也看到过在FPGA中用内部的逻辑,自己手写了一个分频器,然后供给了别的时序逻辑的时钟端口(在always的敏感列表里面),这种方式是不建议的。因为自己手写的逻辑生成的时钟可能并不是很稳定,存在亚稳态的风险,如果是setup和hold都留了较大的margin的话,应该问题还是不大,另外就是这种方式的驱动能力的问题。所以Xilinx的FPGA有设计专门让时钟走的铜线。

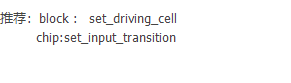

多路复用时钟

在一个系统里面,很有可能会用到多个时钟轮流驱动一些触发器,为了适应不同的数据速率要求,进行时钟切换。有时为了节约功耗,也会把高速时钟切换到低速时钟,或者进行时钟休眠操作。另外我补充一下的就是功耗消耗在哪里,很大一部分就是消耗在reg的Q值翻转上面。多路时钟如下图所示:

这样的时钟一般情况下也会导致一些问题,比如时钟切换时导致后面驱动的寄存器建立时间不足,当满足一定的条件时,这种多路复用器的时钟也是可以使用的。要么就是在clock1结束后处于一段复位时间。否则就有产生glitch的风险,这在DFT可测试性分析中,就会遇到这种风险。假设clock1和clock2都来自scan_clock的时候,就会有glitch,因此需要用scan_mode让其固定的选择一路信号。不懂DFT的就忽略我说的吧。

门控时钟

如上图所示,是最开始门控时钟的思想,这里我先简单介绍一下ICG,ICG的类别还是很复杂的。以后专门写一篇文章来总结。毕竟本文的任务是DC的约束。上面与门,一个pin是异步的,所以这样很容易产生glitch。这种方式的思想就是为了关闭后面的时钟,从而减小了后续的reg翻转。

因此我们就可以通过设置一种电路,让门控使能信号在通过这个逻辑电路之后,仅仅在时钟低电平的时候进行翻转,而在时钟高电平的时候,不能翻转也就是保持。从而我们就想到了低电平触发的锁存器,使能信号通过低电平的锁存器之后,如果使能信号在高电平跳变,锁存器的输出信号是不会改变的,电路图如下所示:

当门控使能信号是高电平有效的时候,也就是高电平打开门控时钟,低电平关闭门控时钟,那么就使用上面的电路,也就是:低电平触发的锁存器+与门。

当门控使能信号是低电平有效的时候,那么就要换成:高电平触发的锁存器+或门。

一般情况,在进行芯片设计的时候,我们不必自己设计门控时钟,大多是ASIC/SoC生产商都有对应的门控时钟单元。这里可以通过command,来让工具自动插入ICG。

行波时钟

行波时钟,也就是一个触发器的输出用作另一个触发器的时钟输入,经常用在异步计数器和分频电路设计中,如下图所示

这种连接的netlist,我还真的见过不少。但是非常困惑,这次明白了,原来真的有这种设计的。后续再来补充介绍。

双边沿时钟

这种在DDR里面非常常见。

然而一般情况下,我们不建议使用双边沿时钟,这是因为:

由于上下沿都用,要求时钟的质量很高,一般的时钟源很难达到,成本高。

由于时钟的抖动等不确定因素的存在,容易使时钟的占空比发生改变,因此容易引起建立时间和保持时间的违规。

当使用的双沿时钟之后,时钟的约束变得复杂,此外当某处发生违规之后,违规的路径的查找难度比单沿时钟大。

还有一点就是测试难度比较大,双沿电路的测试电路必定有别与单沿的测试电路。进行扫描测试时,上下沿的时钟先都得插入多路复用器进行选择。

2、 DC中的时序约束

在默认的情况下,逻辑综合时,即使一个时钟要驱动很多寄存器,DC也不会在时钟的连线上加时钟缓冲器(clock buffer)以加强驱动能力,时钟输输入端直接连接到所有寄存器的时钟引脚,也就是说,对于高扇出(high fanout)的时钟连线,DC不会对它做设计规则的检查和优化。在时钟连线上加上时钟缓冲器或作时钟树的综合(clock tree synthesis)一般由后端(back end)工具完成,后端工具根据整个设计的物理布局(placement)数据,进行时钟树的综合。加入时钟缓冲器后,使整个时钟树满足skew, latency和transition的目标。

图1为preCTS ,图2为postCTS

由于DC在逻辑综合时候并不知道,(抖动)jilter,延迟(latency)和时钟的偏差(skew)及转变时间(transition)默认值为零。显然,理想时钟网络与实际的情况不同,使用理想时钟网络将产生过于乐观的时间结果。为了能在综合时比较准确地描述时钟树,我们需要为实际的时钟树建模,使逻辑综合的结果能与版图(layout)的结果相匹配。

我们用下面的命令建立时钟那几个属性模型:

create_clock

set_clock_uncertainty

set_clock_latency

set_clock_transition 分别进行时钟的周期、偏移、延时、转换约束:

set_clock_uncertainty:对时钟的偏移和抖动进行建模,也就是对时钟的偏差进行建模,具体使用为:

假设时钟周期为10ns,时钟的建立偏差为0. 5ns,用下面命令来定义进行约束:

create_clock -period 10 [get_ports CLK]

set_ clock_ uncertainty -setup 0.5 [get_clocks CLK]

set_ clock_ uncertainty -hold 0.5 [get_clocks CLK]

上述是对setup和hold的uncertainty进行了建模:

理想的时钟:

对建立时间的uncertain进行约束:

对建立时间和保持时间都进行约束:

还可以通过下面的方式对下降沿也进行时序约束,如果是双边沿,比如DDR,那下面的方式肯定是需要的。

set_ clock_ uncertainty -rise 0.2 -fall 0.5 [get_clocks CLK]

时钟转换时间的建模:

由于时钟并不是理想的方波,用set_ clock_ transition来模拟时钟的转换(transition)时间。默认的上升转换时间为从电压的20%上升至80%的时间,下降的转换时间为从电压的80%下降至20%的时间。如果set_clock_transition命令中不加开关选项“-setup”或“-hold" ,那么该命令给时钟赋予相同的上升和下降转换时间。一般情况下,我们只约束最大的转换时间,如最大转换时间是0.2ns,那么就加上-max选项:

set_clock_transition -max 0.2 [get_clocks CLK]

时钟延迟的建模:

时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency)。我们使用set_clock_latency进行时钟延时的建模。一般情况下,我们把时钟源延迟(source latency)和时钟网络的延迟(network latency)分开来,因为时钟源延时需要建模,是因为DC是真的不知道这延时是多大,但是对于时钟网络的延迟,DC在布局布线前不知道,但是在布局布线后就可以计算出来时钟网络的延时了,因此在布局布线之后进行综合时,就没有必要对时钟网络进行延时,因此就要把这两个延时分开来进行约束。

先说布局布线之前:时钟周期为10ns,时钟源到芯片的时钟端口时间是3ns,时钟端口都内部触发器的时间是1ns,如下图所示

![]()

那么就用下面的命令进行建模:

create_clock -period 10 [get-ports CLK]

set_clock_latency -source 3 [get_clocks CLK]

set_clock_latency 1 [get_clocks CLK]

通常情况下,我们约束最大的延时,也就是加上-max的选项,表示最大延时是多少(如set_clock_latency -source -max 3 [get_clocks CLK] 就是时钟源到芯片时钟端口最大的时间是3ns)

transition就不介绍了,下面直接总结的pre CTS前后的模型基本command:

3、环境、设计规则和面积约束

在综合之前,你必须要定义好你的设计期望处于一个怎么样的环境之中,比如你的芯片是航天级别的芯片,那肯定工作环境是不一样的,你如果不进行约束,最后综合出来的结果,你将无法在宇宙环境中实现,所以这里再次提醒一句,DC相当于就是你去告诉他现实是怎样的一个环境,他根据你的实际环境尽量去建模,以期望综合出来的芯片能够在实际环境中工作。

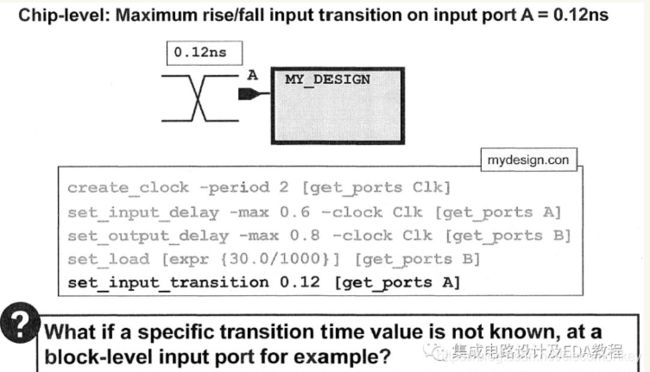

如下图所示, 定义一款芯片的环境是通过operatting condition ,system interface characteristics and wire load model(仅当DC没在topo模式下面时)

3.1 环境设置选择set_operatting_condition

虽然我们foundry提供了三种不同的库文件,slow nomal fast 三种,这三种库文件都有规定的PVT,我们如果要让电路在不同于“nominal”电压和或温度的条件下工作,我们需要为设计设置工作条件(Operating Conditions),我们可以用set_operating_conditions命令把工作条件加入到设计上。综合时,原来按"nominal”环境计算出的单元延迟和连线延迟,将按工作条件作适当的比例调整。

相当于告诉DC工具,比如你现在工作温度125度的高温环境(slow),仍然满足不了我,我现在要工作在一个温度更高的环境比如150°,从而你去里面给我找符合我要求的cell出来综合满足我。

我的company的工艺库位于

/rsc/library

指的是PVT: process、voltage、temperature

通常来说工艺角会考虑进去,电压的变化常常伴随着复杂的计算,通常会被考虑为线性关系,温度在一些亚微米工艺中有时候是非线性运算。通常,我们最常见的图如下。注意,我所示的nominal就是每个操作环境下面的中间值

通过set_operating_condition 来指定工作环境。

3.2 设置线负载模型set_wire_load_model

在计算时序路径时候,除了知道门单元的延迟外(由foundry的cell提供),还需要知道连线net的延迟,用wire load model—WLM估算,WLM是厂商根据多种已经生产出来过的芯片进行统计,在同样的工艺下,计算比如负载扇出为2的平均长度是多少,负载扇出为3的平均长度是多少,也就是说她是根据负载的扇出的平均长度来估计的。

如果要查看工艺库中的WLM,可以使用命令:report_lib $lib_name,进行综合时,综合工具会默认根据设计面积和节点处的负载自动选择合适的连线负载模型,如果要关掉自动选择WLM,那么可以使用命令:

set auto_wire_load_selection false

然后手动选择线负载模型的命令是:

set_wire_load_model -name $WIRE_LOAD_MODEL -library $LIB_NAME

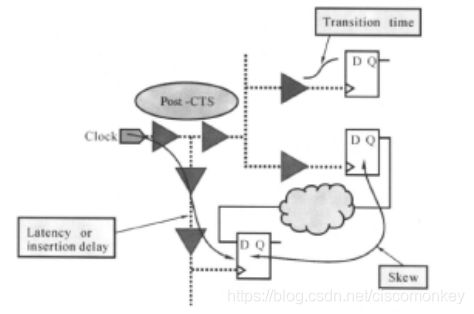

3.3 设置驱动强度(set_driving_cell)

驱动强度、电容负载这些约束是要经验的,一方面是对I/O口进行约束,属于I/O口的约束,为时序约束与时序分析提供了路径,更是为输入/输出路径延时约束的精确性提供保证;一方面是对I/O口对外的环境进行约束,可以算是属于环境约束

为input或者inout的端口设定驱动。Set_drive以电阻值为计量,0表示最大驱动强度,通常为时钟端口;而set_driving_cell则以模拟端口驱动的器件形式计量,说明输入端口是由一个真实的外部单元驱动。

为什么要需要为input或者inout的端口设定驱动?这是因为,对于输入端,为了精确计算输入电路的延时时间,DC需要知道到达输入端口的转换时间

在默认情况下,DC假设输入端口上的外部信号转换时间是0 ,也就是从上升沿跳变到下降沿或者下降沿跳变到上升沿的时间是0,这是不符合实际情况的。通过设置驱动强度,就告诉DC这个设输入端口实际上是由一个真实的外部单元驱动的,不是理想的;DC就会计算输入信号的实际转换时间,仿佛指定某一个库单元正在驱动输入端,下面是输入端IN1 由FD1的输出引脚驱动的例子:

3.4 设置电容负载(set_load)

3.4 设置设计规则约束

set_max_transition

set_max_fanout

set_max_capacitance

3.5 面积约束

什么是芯片的门如何衡量?

https://mp.weixin.qq.com/s?__biz=MzU5NzkxNzI0Mg%3D%3D&idx=1&mid=2247483980&scene=21&sn=c845204ef291d090244cd32206845b80#wechat_redirect

4 官方脚本解读

以下脚本选自DC workshop 的Lab1,下面,我来逐个击破讲解介绍,往后有了自己的模板过后,这些就是填空即可,当然,你得能看得懂,并且能记住个大概。更多的需要训练自己多一份耐心去查看syn2 和syn3手册以及ug。

1、 set lib_name cb13fs120_tsmc_max

是变量名替换,一般用set,没有用set_app_var就要怀疑是不是自己定义的变量名了。

2、current_design TOP

指定顶层文件是TOP,如果你只敲current_design就是查看当前的设计是谁。

如果你想看你读入了哪些设计,然后将其设置为current_design。可以使用list_designs,如果你想要移出掉当前指定的current_design,你可以remove_design

5、reset_design

代表重新设置针对该设计的所有的属性、时钟、路径等约束

8、create_clock -period 2 [get_ports clk]

设置在port clk的时钟周期约束,也可以定义占空比非50%的波形,如下图所示,创建一个时钟约束在PH1上面,周期为10ns ,波形 5ns的地方上升,9.5纳秒的地方下降。值得注意的是 -waveform{ }里面第一个是上升沿,第二个是下降沿。

9、set_clock_uncertainty 0.2 [get_clocks clk]

关于这个值设置为多少?,下面我搜索了一些答案

https://www.zhihu.com/question/50599344

http://bbs.eetop.cn/thread-412544-1-1.html

12 supressed_message UID-401

用print_suppressed_messages,可以查看所有被压制的message.

然后想要开启这个message,可以取消压制的这个message,使用unsuppress_message

13 set_driving_cell -library $lib_name -lib_cell sdcfq1 [remove_from_collection [all _ inputs ] [get_ports clk] ]

指定一个cell作为作为时钟的驱动,这个我在我司的tcl中并没有看到这样的脚本,而且我如何判断用哪一个cell作为输入驱动呢?下面将会说明。

什么是为设计指定输入端口的驱动强度?

我们需要知道的是一个的延迟与两个内容有关系,一个是output load。

因此,对于整个设计的输入端口input port而言,input transition关乎着cell delay。

一般来说DC工具,默认所有输入端口设置合理的驱动能力或者transition时间非常重要。

这里DC提供了三种对input transition的方法:

1、set_driving_cell

定义输入端口的驱动能力可以是标准单元库中的一个缓冲器或者反向器件(buffer/inv)单元,实用set_driving_cell命令设置输入端口前面是什么驱动单元驱动它的,EDA工具会从指定的库中查找得出真实的transition。

2、set_drive

可以直接指定电阻值

3、set_input_transition

直接指定转换时间

下面进行详细说明:

我在网上找到了如下讨论:

set_driving_cell

应用: Block Level

通常应用于block,我们通过set_driving_cell命令来设置某个输入端口前面是什么驱动单元来驱动它,EDA工具会从指定的库中找出真实的transition时间来代替零transition。(如果是block与block之间的)

下面在ug里面有说明,使用set_driving_cell的时候你可以不用-library选项,工具会自动匹配符合操作环境的所有library。

![]()

如下图所示,因为我们的block设计人员对接好,输出的cell是什么,如果是在chip层的话,建议使用inv或者buffer即可,如果没有商量好的话,可以事先假设用inv、buffer或者驱动。

set_drivre的用法

应用场景:chip level

set_drive命令通过为输入端口指定电阻值的方法来为其定义外部驱动强度。对于芯片chip级别的设计(顶层设计而言),它的输入端口的驱动能力很难用工艺库中的某个驱动单元去量化,因此一般不在使用set_driving_cell来指定驱动强度。

由于在顶层,要驱动的是负载较大的IO单元,故需要的驱动能力较强,典型的值是0.05,单位取工艺库中电阻的单位,一般为kΩ;

· 阻抗resistance:非负的驱动阻抗,该值越小表示驱动能力越大。(一个MOS管的开关模型是一个电阻串联一个开关,驱动一个MOS管栅极的是上一级MOS管的漏端,它总是通过该电阻连接到电源或者地,这里设置的是MOS管等效电阻的大小);

· 端口名列表port_list:设置为哪些输入端口设置驱动电阻。

由于通常情况下,设计的时钟和复位端都由驱动能力很大的单元或树形缓冲来驱动,所以可以用set_drive命令将这两个端口的驱动电阻设置为0,也就是驱动强度为无穷大(该命令对当前设计有效)。

举例:

例1:给设计的输入端口A、B和C指定2.0 kΩ(单位一般是kΩ,跟库中定义有关)的电阻,可以用该命令:

set_drive 2.0 {A B C}

例2:为设计中的所有输入端口指定12.3 kΩ的电阻,可以用该命令:

set_drive 12.3 [all_inputs]

例3:将ddfs的时钟和复位端的驱动设为无穷大,即驱动阻抗设为零:

current_design ddfs

set_drive 0 {clk, reset}

set_input_transition命令

应用场景:chip_level

我们可以用set_input_transition命令为输入端口指定一个固定的transition时间,工具就会用该transition时间来计算它驱动的逻辑电路的延迟。

什么是驱动能力?

![]()

下面有两条比较实用的建议:

http://bbs.eetop.cn/forum.php?mod=viewthread&tid=295634&page=1

https://www.cnblogs.com/ASIC-Horizon/p/10053487.html

总结

下面总结

set_driving_cell

set_drive

set_input_transition

的区别

以上三种方式都可以用来指定输入端口的驱动。

set_driving_cell是首选的方法,因为他是最真实的模型,当我们的设计是block时候,我们的设计前面一般还有其他的design,我们可以根据外围电路的输出cell来给自己的模块指定驱动强度。这个就需要与其他的designer商量好,保险的方式,你可以暂时先用inv或者buffer来驱动。

采用设置输入驱动能力,驱动能力越大,转换时间越小,驱动能力越小,转换时间越大

当我们的设计是chip时候,芯片外围电路要驱动的是负载较大的IO单元,因此一般驱动能力也比较强。,一般选择set_drive命令。但是这个电阻也不太好衡量,一般时钟port可以设置为0,无穷大。

但我看我司的脚本用的是set_input_transition来在chip层次设置固定的transition,没有看到set_drive的命令,如果以后遇到了,再补充

讲了这么多,现在又再次回到官方的脚本

14、 set_input_cell 0.1 -max -clock clk [remove_from_collection [all_inputs] [get_ports clk] ]

如下图所示,时序路径的约束有下面四种,现在我们要约束的是输入端口到寄存器的值

路径的特性是存在延时,也就是说,路径1、2、3、4都存在有延时,延时最长的一条路径称为关键路径。一般情况下,路径1、2、3是最常见的,路径4比较少见。

有人建议的原则是 3/7 原则,外面设置70%,里面留30%

所以有人给DD的建议是输入输出都采用DFF

我司的设置如下:

![]()

最后,总结得出设置在40%到60%之间,并且建议Design IC人员遵循输入输出采用DFF的形式,否则就会有一段不预期的组合逻辑存在。

参考:

https://mp.weixin.qq.com/s/5KaY0XY-WUznIn-JWn_0Ww

下面再来总结一下:set_input_delay

也就是说你告诉工具Tclk-q+Tm是多少,然后DC在综合的时候会对组合逻辑N和第一个FF的延迟进行优化和约束(比如算法上简化逻辑,比如选用更牛x的cell以满足时序)等等,所以一般建议DD输入输出均选用DFF,这样可以避免组合逻辑的N造成的延时。

此外还有多输入路径,以及负沿触发等等不同的情况,详细见:

https://mp.weixin.qq.com/s/5KaY0XY-WUznIn-JWn_0Ww

18、set_output_delay 1 -max -clock clk [all_outports]

下面再来总结一下out_put_delay

我们通过指定外部逻辑用了多少时间,也就是Tt+Tsetup用了多长时间,从而退出留有多少时间给内部逻辑。上图可以简化为如下:

不管是输入还是输出,只要把握好时序分析的经典图形,就可以很好的理解了。

另外其实有没有发现,不管是set_input_delay也好还是set_output_delay也好,都是等效于看作时序分析中的经典两级寄存器图。对于input,就是通过DC去约束输入reg和logic,对于output就是去通过DC约束输出reg和logic

参考:

https://www.cnblogs.com/IClearner/p/6624722.html

上面图里面怀疑表述错误,应该是40%,不知怎么冒出来的20%

19、set_load [expr [load_of $lib_name/an02d0/A1] * 15] [all_outports]

参考:

https://blog.csdn.net/weixin_30929295/article/details/94959984?utm_medium=distribute.pc_relevant_t0.none-task-blog-BlogCommendFromMachineLearnPai2-1.channel_param&depth_1-utm_source=distribute.pc_relevant_t0.none-task-blog-BlogCommendFromMachineLearnPai2-1.channel_param

命令掌握

以下命令,是本节博客中需要积累的。

list_libs [lib_list] 列出当前在内存中的吃进去的lib

list_designs

查看当前读入了哪些设计

set_operating_conditions syn2 P2747

-max_library max_lib

Specifies the library containing definitions of the operating conditions for maximum delay analysis. This is either a library name or a collection. The tool selects the first library in the collection containing the definitions.

-max max_condition

Specifies the operating condition to use for maximum delay analysis.

set_driving_cell

set_input_transition

参考文章

为了表示对原创作者的尊重,特此声明,并表示感谢

本博文主要参考了以下优质文章,并对其做了进一步的读解,和补充

参考文章:

https://www.cnblogs.com/IClearner/p/6624722.html

https://www.cnblogs.com/IClearner/p/6628729.html

https://www.cnblogs.com/IClearner/p/6440488.html

http://bbs.eetop.cn/forum.php?mod=viewthread&tid=295634&page=1

https://www.cnblogs.com/ASIC-Horizon/p/10053487.html

https://www.zhihu.com/question/50599344

http://bbs.eetop.cn/thread-412544-1-1.html

https://mp.weixin.qq.com/s?__biz=MzU5NzkxNzI0Mg%3D%3D&idx=1&mid=2247483980&scene=21&sn=c845204ef291d090244cd32206845b80#wechat_redirect

https://blog.csdn.net/weixin_30929295/article/details/94959984?utm_medium=distribute.pc_relevant_t0.none-task-blog-BlogCommendFromMachineLearnPai2-1.channel_param&depth_1-utm_source=distribute.pc_relevant_t0.none-task-blog-BlogCommendFromMachineLearnPai2-1.channel_param

http://bbs.eetop.cn/thread-306407-6-1.html

https://www.cnblogs.com/IClearner/p/6624722.html

https://mp.weixin.qq.com/s/5KaY0XY-WUznIn-JWn_0Ww

另外我问了一个问题,verilog model是什么东东,每次都要吃这个。

下面总结一下就是说Verilog model包括有sram ip 模拟 三种情况都有可能,即使你是ip,你看不到里面的内容,工具是可以看得到的。然后有了这个verilog model,工具就可以跑仿真。

下面说说模拟.v 文件,模拟的.v只是模拟的工程师根据DD的需要对verilog-a进行建模,从而提供给DD的人员跑仿真,但是真正的具体实现,需要另外再做,因此verilog-a可以写不可综合的语言,并且省略了模拟的很多细节东西。