xilinx A7芯片介绍

1,Power&Ground

VCCAUX是为辅助电路供电的引脚,1.8V;VCCAUX_IO_G#是为辅助I/O电路供电的引脚,1.8v或者2.0v(只有HP bank有此引脚);VCCINT是给内核逻辑供电的引脚,0.9v或者1.0v;VCCO_#是给输出驱动供电的引脚,以bank为准;VCCBRAM是给block ram供电的引脚,1.0v;VCCADX_0是给xadc供电的引脚。

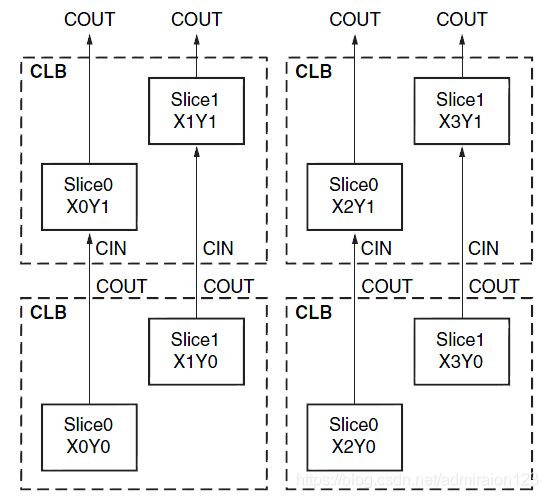

2,CLB可配置逻辑模块

CLB(configurable logic block)是xilinx fpga的基本模块。其结构如下图所示,通过switch matrix矩阵开关连接,x是横坐标,y是纵坐标。一个CLB模块由两个slice模块构成。slice分为SLICEL和SLICEM,只有后者才可以配置为分布式内存distributed memory或者移位寄存器SRL(shifted register)。一个slice又由4个lut6、8个flipflop以及算术进位链(arithmatic carry logic)、选通开关multiplexer构成,当然还包含一些控制信号sr、clk、ce等。xilinx芯片资源统计时有一项是logic cells,它等于lut*1.6,具体可参考https://forums.xilinx.com/t5/Virtex-Family-FPGAs/logic-cell-vs-CLB/td-p/743699。

另外,xilinx 7系列器件中既有同步复位触发器FDRE,也有异步清零触发器FDCE,但它们两都是高电平有效,因此写代码时最好使用高电平复位,避免加入多余的反相器;并且xilinx官方文档还推荐使用同步复位,因为7系列器件的异步复位会占用更多资源。

3,Block RAM

xilinx A7系列的Block RAM为36Kb(RAMB36E1),也可以分配为两个18Kb(RAMB18E1),可以配置为单口ram、双口ram等,写模式可分为write first、read first和no change模式,读模式可选择输出寄存。另外,采用built in技术,用户可快速构造大型的fifo,无需自己写比较、状态信号等的逻辑,支持标准和fwft模式。

4,DSP

xilinx A7系列单个乘法器DSP48E1支持25*18的乘法运算,并提供48位分辨率输出。

5,SelectIO

xilinx A7系列的IO管脚分为高性能HP(high perfomance)和高范围HR(high range)两种,按bank分布在fpga两侧。HP口支持高速内存接口以及芯片间的接口,电压<=1.8v。HR口支持的电压范围广,<=3.3v。selectIO的结构如下图所示,HR没有ODELAYE2模块。IOB模块用于控制输入、输出、三态以及IO buffer、中端等;delay模块用于控制进出fpga的延时;logic用于控制ddr和sdr功能;serdes则用于串并转换引脚。7系列一个bank包含50个IO口,其中24对可用作差分对(以IO_LXXY_#命名,L表示差分对,Y的取值为P/N),top和bottom两个io口不能(以IO_XX_#命名)。如果芯片包含HP BANK,那么每一个HP BANK还包含VRP和VRN引脚,用于DCI(digital controlled impedance),调节该bank io阻抗。

A7系列 xilinx中io可支持各种电平,TTL、CMOS、HSTL、LVDS、SSTL、TMDS等,具体各种电平的范围以及应用可查看ug471和ds181。比较关注的点有:a,电平(例如lvds,a7系列由于只有HR BANK,所以用于lvds传输的bank需要2.5v供电,但可以接收1.8v lvds输入信号;)。b,速度,a7系列 -2速度等级支持的ddr lvds可达1.25Gb/s。c,终端电阻,如果a7系列HR BANK没有2.5V供电,那么使用lvds时必须关闭内部终端。

6,GTP

xilin A7系列中GTP按quad划分,具体数量依据型号不同而不同。1quad包含4对收发通道,每个通道最高支持6.6Gb/s。一对收发通道的具体结构如下图所示。

7,Clock

8,Configuration

7系列fpga配置模式有jtag only模式,串行模式(master/slave,用外部烧写器配置),master spi模式(x1,x2,x3,配置flash),master bpi模式(nor flash,并行),selectmap模式(master/slave,用外部烧写器,并行)。具体模式由M[2:0]配置引脚决定,如下图所示。

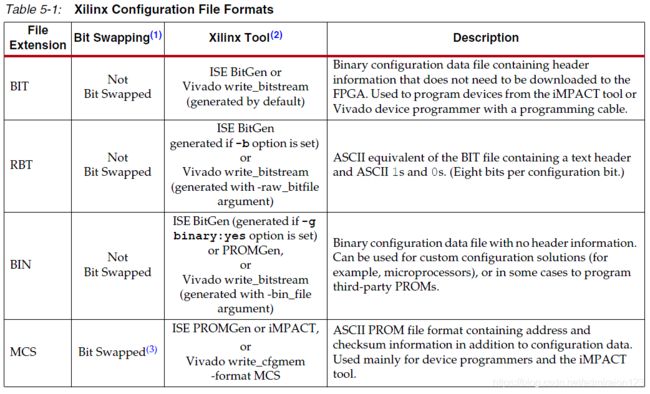

7系列配置文件常用的有bit文件,bin文件,mcs文件,前两个文件为二进制文件,后一个是ASCLL码文件。bit文件带有头信息和数据信息,用于JTAG在线调试;bin文件只包含数据信息,可以烧写进flash;mcs文件包含地址、数据、校验信息。具体如下图所示。另外,7系列位流文件一般结构为bus width auto detect+sync+data。bus width auto detect字段用于并行模式配置探测位宽,串行配置可以忽略,sync字段用于同步。

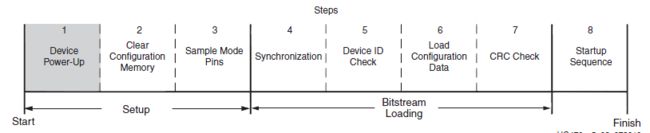

项目中一般采用master spi模式,配置文件存储在spi flash里。大体到的上电流程:上电,program_b一直为低,清除配置信息,此外将program_b拉低也可以进入复位序列;此阶段init_b为输入引脚,一直拉低该引脚可以延迟配置,表示fpga在配置复位阶段,此外复位结束后,此引脚变为OD输出,当fpga检测到额配置错误时,此信号也会拉低。当两者都为高时,采样M[2:0]引脚,得到配置模式;然后在cclk的驱动下,开始配置序列。配置完成后,done引脚拉高。具体配置流程如下图所示。

multiboot,flash存储程序的区域分为golden区和update区,golden区域用于存储固定不变的程序,该程序保证fpga能正常工作;update区用于存储升级程序,在线升级时更新此处程序。升级过程失败时,fpga跳转到golden区加载程序,以保证fpga在能正常启动。具体流程如下图所示。上电后,fpga从地址0读取golden镜像区的头,执行IPROG(internel program)后,跳转到WBSTAR(warm start address)所指示的地址,执行加载update镜像;如果加载过程出错(加载完后,bit文件尾部有一个Check CRC指令,并伴随一个CRC校验码,设备会比较该码与自己计算的CRC码,与不同则出错),则执行fallback,拉低init_b和done引脚,清除配置内存,跳转到golden区,重启配置流程;在fallback流程中,会忽略掉wbstar和iprog,直接加载程序。特别的,7系列可添加两个barrier images(timer),检测不到同步字时(update头部被擦除或者破坏)或者加载出错(update中间被破坏),产生超时fallbak。

对于A7芯片,采用spi flash模式启动,其multiboot流程如下:

1,准备一个update工程,该工程为需要升级的工程,在xdc约束文件中添加以下约束,然后生成bit文件,该文件大小如果灭有添加压缩选项,则可以查询ug470,如果添加了,则直接查看生成后的文件大小。注意timer一定要在bit文件添加,否则timer1不起作用。

a,set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

b,set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

c,set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 1 [current_design]

d,set_property BITSTREAM.CONFIG.TIMER_CFG 0x001312d0 [current_design]

e,set_property BITSTREAM.CONFIG.CONFIGRATE 6 [current_design],默认加载配置时钟为3Mhz

f,如果使用的flash>=256Mb,还需要添加set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design]

2,从网上下载xapp1247,然后得到multiboot_adress_table.tcl,使用vivado tcl shell工具执行它,输入相关参数,最后生成Timer1.bin和Timer2.bin。并得到golden.bit,timer1.bin,update.bit,timer2.bin的地址空间。

3,准备一个golden工程,该工程为升级失败后,执行fallback的程序,该程序应该具有升级功能,在xdc约束文件中添加以下约束,注意地址寄存器的值为timer1.bin的存储地址。

a,set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

b,set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x0007fc00 [current_design]

c,set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

d,set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 1 [current_design]

e,set_property BITSTREAM.CONFIG.CONFIGRATE 6 [current_design]

f,set_property BISTREAM.CONFIG.TIMER_CFG 0x001312d0 [current_design]

g,如果使用的flash>=256Mb,还需要添加set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design]

4,使用tcl指令或者tools->generate memory configuration file生成mcs文件。