计算机原理与应用第六章——总线技术

第六章——总线技术

文章目录

- 第六章——总线技术

-

- 一、总线的基本概念

-

- (一)总线的概念

- (二)具体读写操作

- (三)实例:PC XT总线

- (四)总线的性能指标

- (五)总线时序

- (六)串行总线

- (七)总线的标准化

- 二、常用扩展总线

-

- (一)SPI(串行外设接口)

- (二)I^2 C总线

- (三)USB(通用串行总线)

- (四)其他

- 三、ARM总线

-

- (一)SoC总线

- (三)AMBA

- (三)AHB(ASB)/APB

- (四)其他

一、总线的基本概念

(一)总线的概念

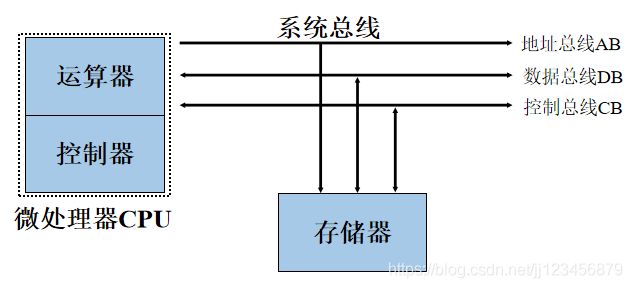

总线,是在计算机的各设备之间传输数据和进行控制的技术和系统。

总线结构:

- 早期:并行、多分支(multidrop)、共享式结构。(需要传送信息的设备都连接到一组公共的并行通信线上,这一组通信线划分为数据总线、地址总线、控制总线)

- 当前:串行、点对点、交换式结构。

但是这里我们学以前的结构:

- 数据线(Data Bus):用于承载总线设备之间传送的数据。

- 双向通信

- 数据线宽度:数据线的条数。直接连接CPU的总线的数据线宽度一般与CPU的字长相同。

- 地址线(Address Bus):用于识别通信对象或数据位置。

- 单向通信

- 地址线宽度:决定了系统管理的地址空间的大小,n位地址线管理2^n字节地址空间。

- 控制线(Control Bus):由若干独立的信号线组成,用于指示当前总线的操作。

- 基本组成:存储器读信号线(MEMR)、存储器写信号线(MEMW)、IO读写信号线(IOR/IOW)。

- 总线中,除地址、数据、控制线外,一般还包含有支持DMA、中断、仲裁等功能的信号线,以及必须的电源、时钟等。

(二)具体读写操作

CPU首先向地址线发送存储器或I/O设备的地址,然后从控制线发出命令(读或写)。

在读操作时,CPU等候一段时间,从数据线上获取数据;存储器或I/O设备随时判断地址线上的地址是否是自己的地址(地址译码),如果是,则根据控制线的命令,向数据线提供数据。

在写操作时,CPU将数据驱动到数据线上,并持续一段时间,以便目标设备可靠地接收;存储器或I/O设备随时判断地址线上的地址是否是自己的地址(地址译码),如果是,则根据控制线的命令,从数据线接收数据。

具有发起总线操作能力的设备,称为总线主设备(master)。

不具有这样的能力,只服从总线命令的设备,称为从设备(slave)。

除CPU之外,DMA控制器也是一种常见的总线主设备,存储器、IO设备等通常都是从设备。

(三)实例:PC XT总线

PC XT总线是IBM在其PC XT计算机中使用的总线,后来被扩展成ISA总线。

8位总线,包含62根信号线,其中包括:

- 8根数据线;

- 20根地址线;

- 若干控制线,主要包括存储器读、存储器写、IO读、IO写、时序控制信号;

- 支持中断和DMA功能的信号线;

- 电源、时钟、复位等。

(四)总线的性能指标

- 带宽/吞吐量

- 总线单位时间内最大的数据传送能力,称为总线的带宽(bandwidth)或吞吐量(throughput)。若总线数据宽度为w(字节),时钟周期为T(秒),则吞吐量最大的可能值为w/T(字节/秒)。

- 现代总线,通过突发等技术,可以接近在每个时钟周期传送一次数据,即吞吐量接近w/T。由于总线周期的交替、协议开销等原因,总线周期不止一个时钟周期,实际传送数据的速率通常不会达到w/T。

- 举例:

ISA总线宽度为2字节,时钟频率为10MHz,则其最大可能吞吐量为20M(字节/秒)。

若ISA总线周期由2个时钟周期组成,则其吞吐量为20/2=10M(字节/秒)。

- 灵活性和扩展能力

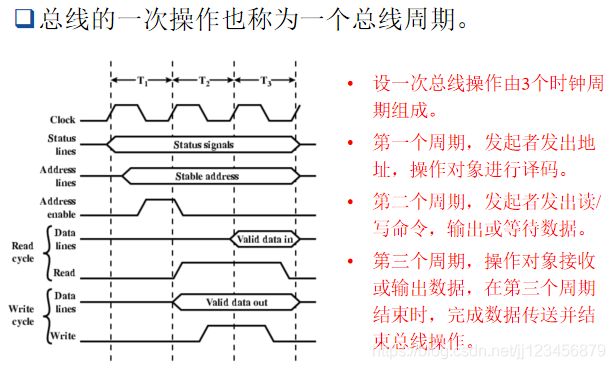

(五)总线时序

为保证数据可靠地在设备之间传递,接收数据的设备需要知道有效数据何时出现在数据线上,而发送数据的设备需要知道何时数据被可靠地接收。总线通过规定明确的操作时间关系来保证传输的可靠性,这种时间关系称为时序。

- 同步总线:总线使用一个统一的时钟,可以规定所有设备根据这个时钟的周期进行操作。

- 异步总线:总线操作不需要统一的时钟,需要在总线中增加状态信号线以表明数据的状态(数据是否被送出或接收)。【需要明确,在总线操作中,发起者不一定是发送数据的一方。如在存储器读操作中,由存储器(操作对象)发出数据,由CPU(发起者)接收数据。】

- 半同步总线:总线按照统一的时钟工作,但总线周期并不完全固定其中可以插入1个或多个时钟周期(称为等待周期),这样高性能的可以按最快的工作,低性能的可以适当延长周期。这类总线称为半同步总线。

总线仲裁:

在共享式总线中,当总线上存在多个主设备时,需要保证一个时刻只有一个主设备操作总线,这就需要仲裁。

- 集中仲裁:总线主设备在操作总线之前,需要首先向仲裁器提出申请(request),并在收到许可(grant)后使用总线。仲裁器在同时收到多个申请时,按照某种优先级原则,向申请者发出许可。

- 分布式仲裁:不使用独立的集中仲裁器,每个主设备需要附带一个实现仲裁功能的组件。在需要使用总线时,由各自的仲裁组件交互信息,使用选举或其它原则决定总线的使用权。

DMA:

上文提到总线上存在多个主设备,除了CPU,DMA也是主设备。

I/O设备与存储器之间的大量数据传送,如果用CPU读写,会占用大量的CPU处理时间。此时我们就采用了DMA功能(直接存储器访问),可以直接进行数据传送,此时CPU能够执行其他任务。DMA需要的DMA控制器就是一个独立的总线主设备。

DMA传输特点:

在存储器和外设或外设和外设之间建立直接传输通路,传输数据无需CPU中转。

需专门的DMA控制器(DMAC),DMA传输期间由DMAC控制总线。

适合高速大批量数据传送的场景。

硬件复杂、成本较高。

总线操作阶段:

申请、裁决、传送、结束。

实例:PCI总线

- 基础的PCI总线是32位宽度,时钟为33MHz的同步总线。

- 总线宽度可扩充到64位,支持64位寻址。

- 具有较高的吞吐量,最大数据传输率133MB/s(266MB/s)。

- 时钟同步方式 。

- 具有隐含的中央仲裁系统。

- 支持突发方式,具有完备的多个主设备支持,能够实现自动配置(即插即用)。

- 兼容性好,独立于CPU。

- PCI是同步总线,所有操作有总线时钟CLK同步。PCI支持突发操作,一个周期中,可以从一个地址开始顺序传送多个数据。

- 采用集中仲裁:PCI总线主设备具有独立的总线请求信号REQ#和总线允许信号GNT#。设备使用它的REQ#信号提出总线请求,经仲裁器经过裁决,通过GNT#允许某个申请的设备使用总线。

(六)串行总线

按照信息传输形式,总线可分为并行总线和串行总线。串行总线使用差分信号线串行传送信号,所有要传送的地址、控制、数据信息,都逐比特地在一对差分线上顺序传送。

差分线可以达到数Gbps的速率。2.5GHz的串行通信线,去掉必要的开销和复用的地址、控制信息,其数据吞吐量接近1Gbps。

由于信号完整性的要求,与并行式完全不同,串行通信线只能点对点地连接两个设备。总线拓扑呈现出以多个集线器为中心的星型结构的互联形态。

构成连接多个设备的总线结构时,需要使用集线器(hub)或交换器(switch)芯片。这些芯片具有多个端口,不同端口的数据在芯片内部进行交换和缓冲。在外部,每个端口连接一个总线设备,设备间的数据通过集线器中转传输。

串行总线操作:

总线一次操作所需要的地址、数据、命令等信息,需要包装成一个具有特定结构的“报文”进行传输。

接收设备在接收完整的报文后,提取其中的信息并完成要求的操作。接收设备还可以发送一个应答报文以确认总线操作的成功。

串行总线规范:

串行总线规范一般分为多个协议层次来定义。

- 物理层:规定串行比特电平和时间特征

- 链路层:规定报文结构和校验

- 交互层:规定通过报文序列、总线操作

串行总线使用点对点的连接取代了共享的多分支连接,不同设备之间的操作不再共用物理介质,因此不存在冲突问题,也就不需要仲裁机构。

串行总线实例:PCIe

PCIe(PCI Express)是一种高速串行总线标准,由PCI SIG颁布

PCIe拓扑结构:

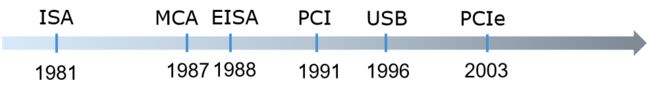

(七)总线的标准化

总线需要连接不同制造商的设备,因此必须成为制造商共同遵循的标准。

计算机总线标准一般由一些有影响力的企业组成的合作组织制定。

二、常用扩展总线

总线的层次结构:

计算机系统内使用多种不同技术的总线,组织成层次的结构,以满足不同的数据传输要求。

一般情况,在层次结构中,靠近CPU的总线,具有更高的性能,连接高带宽和低延迟要求的设备,如CACHE,主存储器;而性能要求较低的设备,则可以使用低成本和较为传统的总线接入系统;不同技术的总线之间,使用桥接芯片连接并转发总线操作。

扩展总线:

计算机中存在很多简单的、性能要求不高、成本敏感的设备,需要灵活的低成本的总线。完成这种任务的总线,通常称为外部总线(external bus)或扩展总线(extended bus)。

扩展总线通过总线桥路接入到较高性能的系统总线。

嵌入式微处理器通过芯片内部的桥路功能和外部引脚,直接扩展出多种总线,方便地连接各种简单设备和模块,能灵活和低成本地提供多种功能。

(一)SPI(串行外设接口)

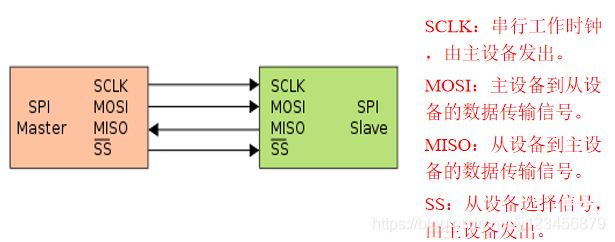

SPI(Serial Peripheral Interface)是一种同步串行总线,采用全双工主从方式工作。

总线中有1个主设备,可以连接多个从设备。

总线有4根信号线构成。

SPI工作时,主设备需要首先配置时钟频率,选择一个从设备支持的频率。

SPI主设备还需要设置工作模式(mode),即设置两个配置比特:CPOL和CPHA,以确定时钟跟数据的相位关系。

多个从设备的SPI总线可以使用两种连接方式:

- 独立连接方式:每个从设备有单独的SS信号,主设备需要提供多个不同的SS信号

- 链式连接方式:从设备的数据输入输出顺次相连,主设备是需要一个SS信号,总线所有设备均同时传送数据。

(二)I^2 C总线

I²C (Inter-Integrated Circuit)是一种异步、支持多个主设备和从设备的串行总线。

I²C由两根集电极开路(OC)或漏极开路(OD)信号组成,分别是串行数据线SDA(Serial Data Line)和串行时钟线SCL(Serial Clock Line)。

I²C时钟工作速率有100KHz的标准模式和400KHz的快速模式,后续的版本定义了1MHz和3.4MHz的高速模式。

I²C的操作的基本单元是消息(message)。消息有起始信号(start),若干地址、数据和应答比特以及停止信号(stop)构成。

(三)USB(通用串行总线)

USB(Universal Serial Bus)是连接计算机和外部设备(键盘、移动存储设备、数码设备等)的总线标准。目前使用的主要是2.0和3.x版本。

USB的主要特点:

- 使用方便,即插即用

- 高速传输速率

- 连接灵活

- 独立供电

USB设备使用点对点的串行连接,使用**集线器(hub)**扩展出多个端口连接多个设备。

USB系统中,只有一个USB主机(USB HOST),主机管理USB总线设备,控制总线的操作。在传送数据时,主机通过设备的地址信息指定与哪个设备进行通信,而不关心该设备具体连接在哪个位置,也不管理数据在HUB中的交换和路由。因此从逻辑上看,所有设备都直接连接到主机。

-

USB是一种轮询总线,所有USB操作都由主机发起。

-

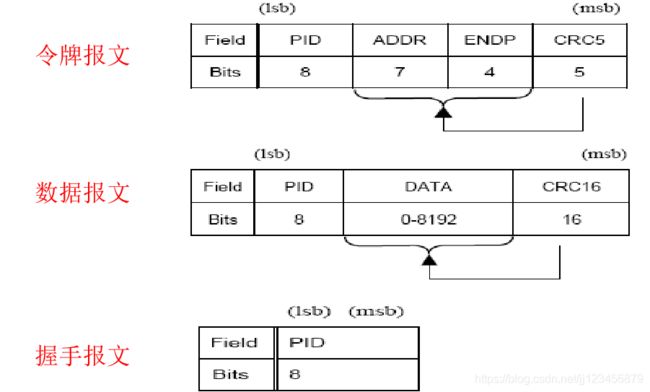

数据通过分组方式传送,这些报文称作USB报文。

-

大多数数据传输由三个USB报文组成的序列完成:

- USB主机首先发出一个令牌报文(token packet),指明传输的类型、方向(IN: 设备至主机,OUT:主机至设备),USB设备的地址以及端点(endpoint)编号,

- 由主机或被寻址的设备发出数据报文(data packet),

- 接收数据的设备发送一个握手报文(handshake packet),指明本次传输是否成功。

-

USB的数据有四种基本的传输类型:

- 控制传输(Control Transfers):用于在连接阶段配置设备,或是传输配置信息或命令状态信息。传输的数据不允许丢失。

- 批量数据传输(Bulk Data Transfers):是在有大量或突发性数据时采用的传输方式,它可利用USB的可用带宽,通过差错检测和重传保证数据的可靠传输,但不保证传输时延和传输间隔。

- 中断数据传输(Interrupt Data Transfers):用于传输及时的、限定时间延迟的数据。可以用来报告事件、发送(pointing device)的坐标等信息。

- 准同步传输(Isochronous Transfers):也被称为流模式实时传输,是按预先商定的速率和时延进行的传输。收端自动识别传输速率。

USB 3.2版本极大地提高了USB总线的性能。

USB 3.2中包含了两条总线,其一是USB 2.0总线,另外增加了更高速率的信号的3.2总线。

USB 3.2的物理接口中,新增加了支持SS速率的两对或更多的差分线,使用单向的全双工方式工作。

(四)其他

- SCSI(Small Computer System Interface,小型计算机系统接口)定义了一种在计算机和外部设备之间传输数据的物理接口和协议,主要用于连接硬盘和磁带机等存储设备,广泛用于服务器,工作站和RAID系统。

- ATA(AT Attachment)是一种并行接口,主要用于计算机中连接硬盘、固态盘等存储设备。sATA(Serial ATA)使用串行连接取代ATA,提供了更高的性能和扩展的功能,如热插拔。

- CAN(Controller Area Network Bus)是一种用于嵌入式控制器之间通信的总线标准。

- 1553B是由美国国防部定义的一种高可靠串行总线标准(MIL-STD-1553)。用于军用航空器上的设备通信,也用于其它需要高可靠性的场合。

- 系统级的互联:大型数据中心、云计算等场合,经常以集群的方式使用计算机和服务器,以提供更高的性能、扩展性和灵活性。提供集群内部通信能力的技术包括infiniband、fiber channel、高速以太网等,这些技术部分地具有总线的特征,也经常称作总线。

三、ARM总线

(一)SoC总线

- 随着半导体技术的发展,集成电路的规模和性能显著提高。当一个芯片可以容纳以往的一个系统的能力的时候,就诞生了soc (system on a chip,片上系统)。

- SoC总线技术就用于soc芯片内部的功能模块之间的通信。

- 芯片内部连接资源相对丰富和灵活,一般没有驱动能力、相互干扰问题和延迟差异问题,因此即使是高性能的通信,仍然可以使用并行信号方式,甚至支持宽达1024比特的数据线。

(三)AMBA

- AMBA (Advanced Microcontroller Bus Architecture,先进微控制器总线结构)是由ARM公司提出的,用于芯片内部功能互联的总线规范,支持芯片内多个处理器和众多功能模块的连接。

- 早期的AMBA采用类似计算机中的系统总线、扩展总线的方式,分为高性能的ASB(Advanced System Bus)/AHB(AMBA High-performance Bus)和连接外设功能的APB(Advanced Peripheral Bus)。

- 为提高总线性能,AMBA 3中增加了AXI(Advanced Extensible Interface),并在后续的AMBA 4和AMBA 5中增加了ACE(AXI Coherency Extensions)和CHI(Coherent Hub Interface),提供总线操作CACHE一致性支持。

(三)AHB(ASB)/APB

-

AHB定义了具体总线接口规范。

-

AHB的特征:

- 支持突发传送

- 不使用三态逻辑实现

- 支持很宽的可配置的数据总线宽度 -

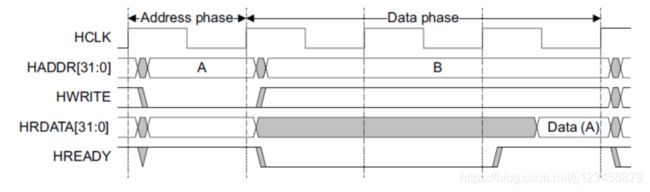

AHB操作:

- AHB的基本操作很简单,分为地址和数据两个阶段,在地址阶段,主设备给出地址和控制信号,在数据阶段接收数据。

- 从设备可以使用hready信号延长数据阶段。

-

AHB连接:

AHB上存在多个主设备时,可以使用交叉连接矩阵将主从设备连接起来。

交叉连接矩阵是一个交换式连接矩阵,可以支持不同的主从设备之间并行通信。这种连接方式称为AHB的多层结构(multi-layer)。

在交叉连接矩阵内部,增加了多个主设备连接到同一个从设备的仲裁器。当不同主设备同时操作一个从设备时,由该仲裁器决定操作的顺序。

性能要求不高的外设一般连接到APB,AHB和APB之间用称作APB桥路(APB bridge)的AHB从设备连接。

APB信号和操作与AHB类似,但不支持突发等高性能操作,简化了设计要求。

APB BRIDGE是APB上唯一的主设备,并提供设备选择(PSEL)和设备使能(PENABLE)信号以方便外设功能的连接。

(四)其他

- AXI

AXI定义了一种新的高性能低延迟的接口,替代AHB连接功能实体,提高了AMBA的性能。

AXI是一种点对点的连接,操作的地址阶段和数据阶段分离,读写操作使用独立的物理通道。

AXI连接由5个独立的通道(channel)组成:读地址、读数据、写地址、写数据、写应答。5个通道使用相似的信号线和基本数据传送方式。 - ACE/CHI

ACE是AXI的扩展,用于从硬件上保持多个处理器中的cache一致。

ACE接口难以满足大量的CPU、GPU等高性能处理的集成要求,ARM在AMBA 5中定义了能够提供更高互联性能的CHI接口,它定义了具有多个层次的分层通信模型,并使用基于报文的通信方式。