FPGA面试题目笔记(五)—— 代码覆盖率、BCD码、带宽

文章目录

本文对 大佬博文中的题目进行整理,将常见及不熟悉题型记录下来。

紫光展锐选择题

1、关于地址线和数据线

[单选题] 数据位宽8bit,地址位宽13bit的RAM,其大小为多少?

A.4KB

B.8KB

C.16KB

答案:B

解题:

8bit = 1byte = 1B 1KB = 1024 B

因此 RAM大小 = 8bit * 2^13bit = 65536 bit = 65536 bit / 8 = 8192 B = 8192 / 1024 KB = 8KB

用2048x12的ROM芯片,最多能实现()个输入 ()个 输出的组合逻辑的数。

答案:11,12

解析:2048=2^11,2048深度是11位地址位,12表示12位输出数据(ROM只能输出)。

某个SRAM共12根地址线A11~ A0,32根数据线D31~D0, 如果要实现1MB的Memory,需要()块这样的SRAM?

答案:64

解析:12根地址线,存储深度为2 ^12,32根数据线有4 字节,即一个SRAM存储2^14 Bytes,1MB = 2 ^20 字节,共需 2 ^20 / 2 ^14 = 2 ^6 = 64 块。

解析:16K = 16 * 1024 B = 2^14,则需要14根地址线,数据线8根,共22根

2、[单选题]linux下,删除文件命令

A.mkdir

B.rm

C.mv

D.del

答案:B ,该题目进行SOCFPGA设计的时候会用到。

A:创建指定的名称的目录(make directory)

B:删除一个文件或者目录(remove)

C:为文件或目录改名、或将文件或目录移入其它位置(move file)

D:删除(delete),它不是lunix下的命令

3、[单选题]一个八位D/A转换器最小电压增最为0.01V,当输入10011100时,输出电压为( D )V。

A.1.28

B.1.45

C.1.54

D.1.56

解: 10011100 ,表示十进制 156,输出电压 = 156 * 0.01 V = 1.56V

4、[单选题]在verilog HDL的always块语句中的语句是如何执行的( D )

A.顺序

B.并行

C.顺序或并行

D.不一定

解题:时序或者组合逻辑均可采用always块,块中的语句如何执行看阻塞还是非阻塞

5、[单选题]项目后仿阶段,不需要哪个文件? ——D

A.标准单元库

B.网表

C.SDF

D.RTL

后仿真即时序仿真

6、[单选题] 一个D锁存器用了多少逻辑门(仅与非和非门)?——B

A.4

B.5

C.6

7、[单选题]In Verilog_hdl,a=4’b1011,so &a=?——D****

A.4’b1011

B.4’B1111

C.1’b1

D.1’b0

解题:按位与

8、学习下面几个概念

initial begin

........ //顺序执行,中间的延时也是顺序累加

end

fork……join内的并行语句都要执行完后,才能执行$display(“dislpay fork”);

initial

fork

..... //并行执行,延迟时间也是并行的

join

$display("dislpay fork");

例子:

reg A;

reg B;

initial begin

fork

begin

A = 1;

#20 A = 0;

#30 A = 1;

#50 A = 0;

end

begin

B = 1;

#20 B = 0;

#30 B = 1;

#50 B = 0;

end

join

end

fork……join中的语句并行执行,因此两个begin……end同时执行,但begin……end中的语句顺序执行。

因此若运行40ns,则A=B=0;

fork……join_none 遇到阻塞被挂起

begin

fork

$display("dislpay fork1");

join_none

fork

$display("dislpay fork2");

join_none

#5ns;

fork

$display("dislpay fork3");

join_none

#10ns;

end

运行结果:

dislpay fork1

dislpay fork2

原因:遇到了时间阻塞

#9、[单选题]下列语句( D )不能在module中独立存在。

A.task

B.initial

C.always

D.forever

解题:forever必须写在initial块中

10、A=(0.8125)10,十进制转二进制,则A=(A)

A(0.1101)2

B.(0.0101)2

C.(0.1011)2

D.(0.1111)2

解题:参考十进制到R进制转换即可,注意是小数形式的十进制。整数部分为0,小数部分一直乘以2.

11、[单选题]运算assign SUM=a[7:0]+b[7:0] +c[7:0] +d[7:0]+e[8:0],为了SUM没有溢出,SUM的位宽最小为多少 B

A.10

B.11

C.12

D.13

解题:分别取位宽能表示的最大值来计算,8bit取255,9bit取511,则255*4+511=1531<2047,即11bit。

12、关于代码覆盖率的问题

[多选题]代码覆盖率主要包含(ABE)

A.行覆盖率

B.条件覆盖率

C.toggle覆盖率

D.功能覆盖率

E状态机覆盖率

[多选题]在验证中下列关于代码覆盖率描述错误的是(CD)

A.代码覆盖率包括语句覆盖率

B.代码覆盖率包括条件覆盖率

C.代码覆盖率包括功能覆盖率

D.代码覆盖率达到100%说明所有Bug已消除

下述关于覆盖率收集结果的描述正确的是(ABD)

A.代码覆盖率高、功能覆盖率低,需要加强功能点的覆盖

B.代码覆盖率低、功能覆盖率高,往往是一个危险信号,说明功能覆盖率建模还不完善

C.功能覆盖率达到100时,代码覆盖率一定已经全部覆盖

D.代码覆盖率高,功能覆盖率高,往往标志验证正处于收敛状态,需要加强各边界点和异常点的测试

Coverage is usually used to evaluate the verification quality, please identify all code coverage related items from following options. ___ABEFG

A. Branch coverage.

B. Condition coverage.

C. Function coverage.(功能覆盖)

D. Toggle coverage.

E. State coverage.

F. Expression coverage.

G. FSM coverage.

分析代码覆盖率时,verilog语句 if(a||b&&c) 有哪几个条件需要覆盖?请用表格列出每种状况下a/b/c的值(a/b/c均为bit类型,如果是0或1都无所谓,请用“-”表示)。(逻辑与优先于逻辑或)

| A | B | C | A 或 B&&C |

|---|---|---|---|

| 1 | - | - | 1 |

| 0 | 0 | - | 0 |

| 0 | 1 | 0 | 0 |

| - | 1 | 1 | 1 |

【大疆】代码覆盖率包括:语句覆盖,判定覆盖,条件覆盖,路径覆盖、翻转覆盖率

13、[多选题]EDA验证中,下面哪种方式可以对时序进行检查(BCD)

A.即时断言 —— 基于时间的,无时序关系

B.并发断言——基于时钟的

C.建立时间约束

D.保护时间约束

华为选择题

1、

modelsim命令在tb中的执行顺序:

Vlib建立仿真库/Vmap映射/Vlog编译/Vsim仿真

2、

关于状态机编码,如下描述中正确的是(ACD)

A 状态编码用parameter定义

B 状态机必须有default态

C 用组合逻辑和时序逻辑分离的风格描述FSM

D 用case语句描述状态的转移

解题:状态机中用到case语句,那么就有default,但是对于case包含完全的状态机,可以不用default态,所以B错误;

但建议只要用了case语句,就加一句default,避免锁存器的生成。

3、

在模块实例语句中,悬空端口可通过将端口表达式表示为空白来指定为悬空端口,模块的输入端悬空值为(D)

A. 0

B. X

C. 1

D. Z

4、

下面4项关于奇偶校验的描述正确的是( C )。

A 奇偶校验可以避免误码的发生

B 奇偶校验一定可以检测错误

C 奇偶校验使用1bit校验位

D 奇偶校验可以检测多bit误码

解题:奇偶校验能检验错误,但是不能避免错误码发生,B太绝对。

奇偶校验采用1bit校验位,只能对1bit码进行检测。

5、

下面关于$ display,$ strobe,$monitor的区别描述正确的是( C )。

A $ strobe直接立刻输出,$ monitor是等稳定后输出,$ display是发生变化时输出

B $ strobe直接立刻输出,$ display是等稳定后输出,$monitor是发生变化时输出

C $ display直接立刻输出,$ strobe是等稳定后输出,$monitor是发生变化时输出

D $ display直接立刻输出,$ display是等稳定后输出,$strobe是发生变化时输出

解析:$ display()和$ strobe()用法和文本基本一致

$ strobe()在该时刻所有事件处理完成才打印文本(稳定后)。

$monitor()监控和输出参数列表中的表达式或变量值(发生变化时)。

6、

用8421码表示的十进制数45,可以写成( B)。

A [101101]BCD B [01000101]BCD C [101101]2 D 45

解析:8421码就是BCD码,每个十进制数都用4位进行表示。4:0100;5:0101

7、

电路设计中需要关注PPA,分别指(ABC)

A.功耗 Power

B.性能 Performance

C.面积 Area

D.成本

8、

在IC设计中,复位设计面临的主要问题包括(ABCD)

A.时钟域的同步

B.去毛刺

C.可否做STA检查

D.对时钟的依赖程度

9、

在Verlog HDL中对于initial语句,说法错误的是(B)

A. 在仿真过程中只执行一次

B. 可用于给实际电路赋初值

C. 在模拟的0 时刻开始执行

D. 多个 initial 块并行执行

分析:通常用于仿真的Testbench模块中对激励矢量的描述或用于给寄存器变量赋初值,而在实际电路中赋初值是没有意义的,在综合时会被忽略;多个initial块在0时刻开始并行执行,只执行1次,且各自独立;

10、

二输入与非门当输入变化为(C)时,输出可能有竞争冒险。

A.00—>10

B.10—>00

C.01—>10

D.11—>01

11、关于实现线与功能的门电路

下列几种 TTL 电路中,输出端可实现线与功能的门电路是()

A. 或非门

B. 异或门

C. 与非门

D. OC门

解析:线与:

OD门:漏极开路门(open-drain),直接线与

OC门:集电极开路(open-collector),须接电源和上拉电阻

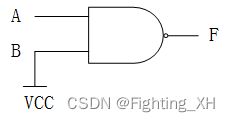

【大疆】将二输入的与非门当非门使用时,另一端的接法应该是

如下图,假设A为输入,F为输出,当A = 0时,F = 1;当A = 1时,要实现非门,则F应该为0,要想F为0,B必须为高电平。

如下关于“线与”逻辑的描述,错误的是:B

A. 可以使用OC门来实现“线与”.

B. “线与”逻辑必须在输出端加一个下拉电阻.

C. “线与”逻辑是两个输出信号相连可以实现“与”的功能.

D. 可以用OD门来实现“线与”.

乐鑫

1、

下列属于异步总线的是 ( C )

A:SPI

B:USB

C:UART

D:IIC

属于高速串行接口的是:PCIE,USB,SPI,RapidIO

2、

在芯片设计流程当中,通常会进行后仿真(post-simulation),关于后仿的作用,以下说法不正确的是 (B)

A:抽检netlist是否和RTL功能一致

B:抽检电路中是否出现有害的glitch

C:抽检时序是否有违规

D:抽检电路中是否存在亚稳态

解析:后仿真也就是时序仿真,检查设计时序与实际的FPGA运行情况是否一致,确保设计的可靠性和稳定性

3、

衡量数字通信系统传输质量的指标是 (D)

A:信噪比

B:噪声功率

C:语音清晰度

D:误码率

4、

若要将一异或非门当做反相器使用,则输入端A,B的连接方式是(B)

A. A和B并联使用

B. A或B中有一个接“0”

C. A或B中有一个接“1”

D. 不能实现

解析:代数验证

填空题:

5、

verilog 当中 a=4’b10x1; b=4’b10x1; 那么逻辑表达式 ab 为(x)a=b为(1);

解析:逻辑等于:参与比较的两个操作数必须逐位相等,其相等比较的结果才为 1, 如果某些位是不定态或高阻值,其相等比较得到的结果是不定值

逻辑全等:是对这些不定态或高阻值的位也进行比较,两个操作数必须完全一致,其结果才是 1,否则结果是 0

6、

4bit的信号输入和8bit的信号输入的乘法器内部计算输出信号至少需要(12)bit的位宽;

4bit的信号输入和8bit的信号输入的加法器内部计算输出信号至少需要(9)bit的位宽;

7、

通常情况下,芯片工作温度较(低),工作电压较(高),速度最快。

代码:

8、

使用verilog编写一根单向导线wire_a仿真模型,此导线的传输延迟为5ns,且不会过滤此波形。

`timescale 1ns/10ps

module wire_a_tb(

input in,

output out

);

reg out_reg;

always@(*) begin

out_reg <= #5 in;

end

assign out = out_reg;

endmodule

选择题

9、

下面关于PLL电路表述正确的是:

A. PLL属于模拟电路,无法用全数字电路实现

B. PLL相对于参考时钟,可以输出分频、倍频、分数频的时钟

C. PLL输入的参考时钟jitter,在PLL输出是会变大,也有可能变小

D. PLL的jitter值等于同步数字电路中clock uncertainty的设定值

10、

以下关于FIFO描述正确的是

A. 空信号是在写时钟域产生的,满信号是在读时钟域产生的

B. 外部可以直接操作FIFO的读写地址

C. FIFO可以分为同步FIFO和异步FIFO

D. FIFO是先进先出的存储器

解析:C:写满,读空。D:外部不可以直接操作FIFO的读写地址

11、

下面是芯片中有关GPIO的叙述,不正确的是:A

A. GPIO一般只具有0态和1态,不具有高阻状态

B. GPIO的引脚一般是多功能复用的

C. GPIO作为输出接口时具有锁存功能

D. GPIO作为输入接口时具有缓冲功能

12、

如下为verilog HDL描述的一段程序,请选择对它产生波形描述正确的是:AD

always begin #5 clk = 0; #10 clk = ~clk; end

A.周期为15

B.clk=0

C.clk=1

D.占空比1/3的时钟

联芸科技

1、

解释D触发器和锁存器的区别,解释同步复位和异步复位的区别及优缺点。

D触发器:

由边沿触发,属于同步控制,不易产生毛刺。

锁存器:

由电平触发,属于非同步控制,容易产生毛刺。

同步复位:

复位信号与时钟信号同步,当时钟边沿到来的时候,复位信号才有效。

.

优点:能带来更好的时序,提高信号的抗干扰能力,有利于仿真器仿真,可滤掉毛刺

.

缺点:复位信号必须大于Tclk才能被真正识别,从而实现复位。需要考虑复位延时等。逻辑器件库内的D触发器一般都只有异步复位端口,采用同步复位需要加入组合逻辑,因此耗资源。

异步复位:

复位信号与时钟信号无关,不管时钟边沿是否到达,只要复位信号有效即可实现复位。

.

优点:相对同步复位来说,逻辑资源库中有含异步复位的D触发器,因此节约资源且设计简单。异步复位信号识别方便,便于使用FPGA全局复位端口。

.

缺点:异步复位抗干扰能力差,复位信号释放的时候如果刚好没满足建立保持时间要求,则易导致触发器输出出现亚稳态。易出现毛刺。

.

针对异步复位,我们一般采用异步复位同步释放的方式来解决。

2、

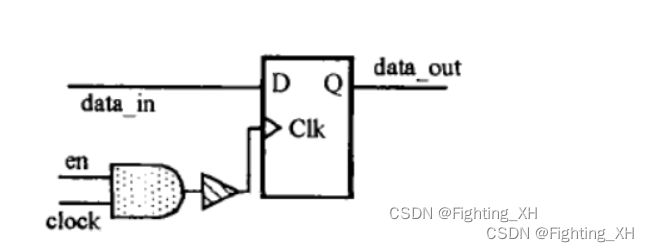

解释什么叫clock gating?并说明一下通常情况下为什么要做clock gating?简单列举通常实现的方法有哪些?

首先掌握降低功耗的知识。

clock gating:时钟门控,它是一种简单且有效的降低功耗的方法。

.

时钟门控的好处:时钟门控通过组合逻辑门来生成时钟,从而可以实现开关性,因此就可将暂时用不到的时钟关闭,避免无用时钟翻转带来的功耗。,从而起到降低功耗的作用。

.

实现方法:设置一个en信号,让clock和en信号与运算。

3、

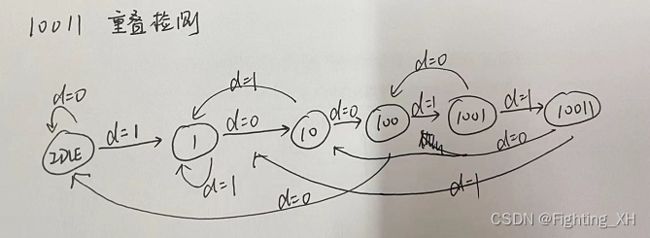

画出10011序列检测的状态图(重叠检测)

掌握不重叠和重叠检测。

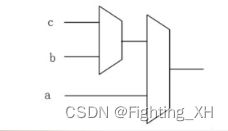

4、现有三个输入信号分别是a,b,c,并且前级DFF Clock到a,b,c的延时分别是Ta,Tb,Tc(Ta>Tb>Tc),请用两个二输入选择器对a,b,c实现三输入选择输出,画电路图并解释设计思路,不需要考虑Clock Skew的影响。

题解:由于Ta>Tb>Tc,因此a延时最大,c延时最小,因此电路图如下:

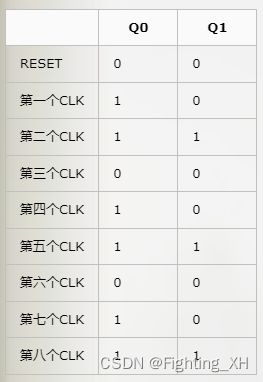

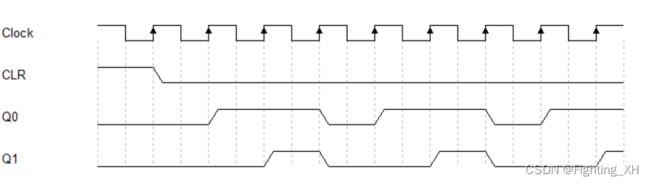

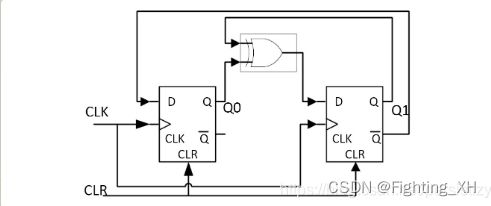

5、请画出下列数字电路D触发器输出Q0,Q1的波形图(复位之后Q0,Q1均为0,画出复位后8个时钟周期)。

首先分析Q0和Q1的值,然后画出波形图。

其中 Q0(n+1) = ~Q1(n) ;

.

Q1(n+1) = Q0(n)^ Q1(n)= ~ Q1(n-1)^ Q1(n)异或运算。

[联发科]

题目1:十六进制的A8D6用八进制的数表示——124326

A8D6 = 1010100011010110 = 124326。

先转二进制,再转八进制

大疆

1、Verilog HDL中哪些结构是不可综合的(列举常用)

(1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。

(2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。

(3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

2、面积和速度优化

面积优化:资源共享,逻辑复制,串行化;

速度优化:流水线,关键路径法,寄存器配平;

3、时序检查中对异步复位电路的时序包含什么?

对于时钟和异步复位信号,分析recovery恢复时间和removal移除时间

recovery恢复时间:在有效的时钟沿来临前,异步复位信号保持稳定的最短时间;

.

removal移除时间:在有效的时钟沿来临后,异步复位信号保持稳定的最短时间;

4、无损定点化的学习

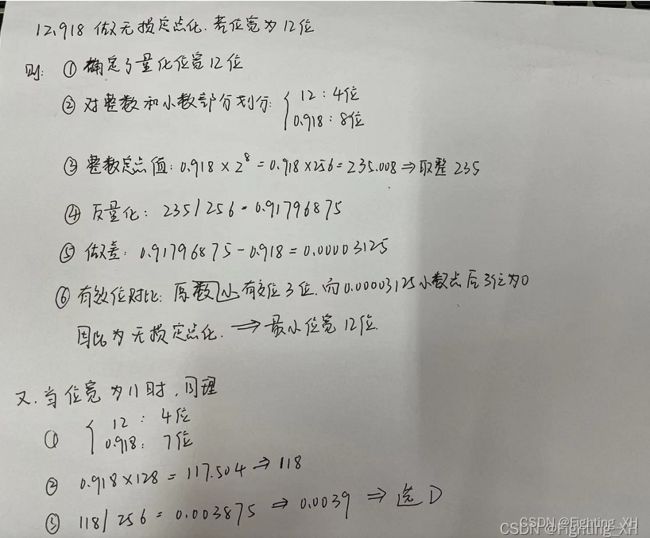

对12.918做无损定点化,需要的最小位宽是多少位,位宽选择11位时的量化误差是多少?

A. 12位,0.0118. B. 13位,0.0039. C. 12位,0.0039. D. 13位,0.0118.

5、组合逻辑中的冒险是由于(D)引起的

A. 电路中有多个输出. B. 电路未达到最简. C. 逻辑门类型不同. D. 电路中的延时.

在组合逻辑电路中,某个输入变量通过多条(两条及以上)途径传到输出端,由于每条途径延迟时间不同,到达输出门的时间就有先有后,这种现象称为竞争

NVIDIA

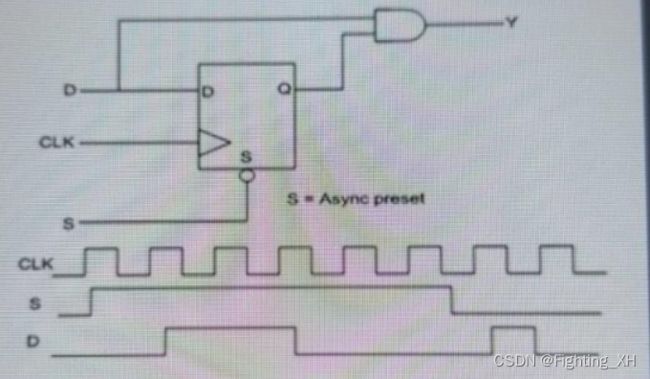

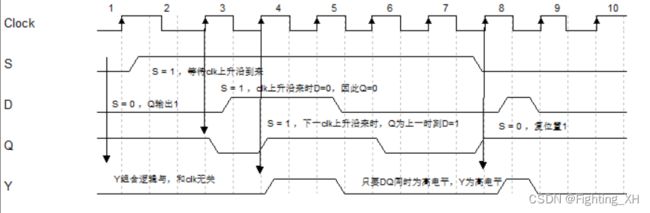

解析:区别异步置位和异步复位。

Async preset:异步置位,当复位的时候,输出为1; Async

Async reset:异步复位,当复位的时候,输出为0;

图片可看出是低电平复位

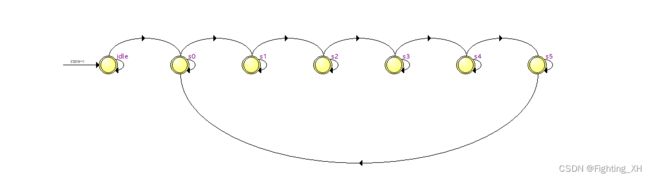

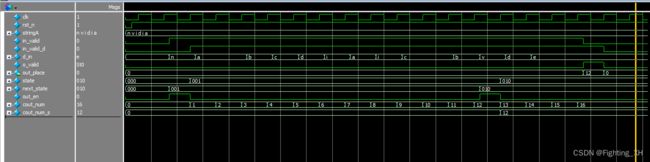

2、编写支持以下功能的verilog代码: 对于字符串A,检测其字符串内字母在字符串B中的位置,并输出最后检测到的字母在字符串B中的位置。举个例子,字符串A是“nvidia”,字符串B是“naabcdiaiccbvde” ” B 中最后检测到的字母是 v,所以输出 13。

解题:该题相当于序列检测器,共有七个状态,idle,S0(n),S1(v),S2(i),S3(d),S4(i),S5(a)。

代码如下:

module test(

input clk,

input rst_n,

input in_valid,

input [7:0] d_in,

output reg [4:0] cout_num_s,

output o_valid,

output [4:0] out_place

);

wire [7:0] stringA[0:5];

assign stringA[0]="n";

assign stringA[1]="v";

assign stringA[2]="i";

assign stringA[3]="d";

assign stringA[4]="i";

assign stringA[5]="a";

parameter idle=3'b000;

parameter s0=3'b001; // "n"

parameter s1=3'b010; // "nv"

parameter s2=3'b011; // "nvi"

parameter s3=3'b100; // "nvid"

parameter s4=3'b101; // "nvidi"

parameter s5=3'b110; // "nvidia"

reg [2:0] state,next_state;

reg out_en;

reg [4:0] cout_num;

always@(posedge clk or negedge rst_n)

if(!rst_n)

state <= idle;

else

state <= next_state;

always @(*)

case(state)

idle: if(d_in==stringA[0] & in_valid) begin

next_state = s0; //001

out_en = 1;

end

else begin

next_state = idle;

out_en = 0;

end

s0: if(d_in==stringA[1] & in_valid) begin

next_state = s1;

out_en = 1;

end

else begin

next_state = s0;

out_en = 0;

end

s1: if(d_in==stringA[2] & in_valid) begin

next_state = s2;

out_en = 1;

end

else begin

next_state = s1;

out_en = 0;

end

s2: if(d_in==stringA[3] & in_valid) begin

next_state = s3;

out_en = 1;

end

else begin

next_state = s2;

out_en = 0;

end

s3: if(d_in==stringA[4] & in_valid) begin

next_state = s4;

out_en = 1;

end

else begin

next_state = s3;

out_en = 0;

end

s4: if(d_in==stringA[5] & in_valid) begin

next_state = s5;

out_en = 1;

end

else begin

next_state = s4;

out_en = 0;

end

s5: if(d_in==stringA[0] & in_valid)begin

next_state = s0;

out_en = 1;

end

else begin

next_state = s5;

out_en = 0;

end

default:begin

next_state=idle;

out_en=0;

end

endcase

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cout_num <= 5'd0;

else if(in_valid)

cout_num <= cout_num + 1;

else

cout_num <= cout_num;

end

//将检测到的字符位置缓存

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

cout_num_s <= 5'd0;

else if(out_en)

cout_num_s <= cout_num;

else

cout_num_s <= cout_num_s;

end

reg in_valid_d;

always @( posedge clk or negedge rst_n ) begin

if(!rst_n )

in_valid_d <=1'b0;

else

in_valid_d <= in_valid;

end

//下降沿检测并延迟一个高电平

assign o_valid = (~in_valid) & in_valid_d;

//将最后检测的字母的位置输出(计数从0开始)

assign out_place = o_valid ? cout_num_s : 0;

endmodule

tb测试文件:

`timescale 1ns/1ps

module test_tb();

reg clk;

reg rst_n;

reg in_valid;

reg [7:0] d_in;

wire o_valid;

wire [4:0] cout_num_s;

wire [4:0] out_place;

test u1 (

.clk(clk),

.rst_n(rst_n),

.in_valid(in_valid),

.d_in(d_in),

.cout_num_s(cout_num_s),

.o_valid(o_valid),

.out_place(out_place)

);

initial clk = 0;

always #10 clk = ~clk;

initial begin

rst_n = 0;

#5;

rst_n = 1;

end

initial begin

in_valid = 0;

d_in = 8'b0;

#34;

in_valid = 1; //给出一组序列naabcdiaiccbvde 可看到最后检测到的字母v,位置是13

d_in = "n" ; //计数器0开始,因此应该输出12

#20;

d_in = "a" ;

#40;

d_in = "b" ;

#20;

d_in = "c" ;

#20;

d_in = "d" ;

#20;

d_in = "i" ;

#20;

d_in = "a" ;

#20;

d_in = "i" ;

#20;

d_in = "c" ;

#40;

d_in = "b" ;

#20;

d_in = "v" ;

#20;

d_in = "d" ;

#20;

d_in = "e" ;

#40;

in_valid = 0;

#50;

$stop;

end

endmodule

AMD

1、

Please select the 4-state unsigned integer types(BC) 无符号整型

A. bit. B. logic. C. reg. D. shortint.

2、

Choose the right descriptions of the different between latch and flip-flop listed below(C)

A. Flip-Flop saves area. B. Latch can’t avoid glitch(毛刺). C. Flip-Flop is easier for timing closure(时序收敛). D. Latch run slower than Flip-Flop.

解析:锁存器也能避免毛刺出现,比如门控时钟。

.

锁存器是电平触发,其优点:

1、面积比触发器小;2、速度比触发器快;

缺点:1、电平触发,非同步设计,易受走线延迟影响,易出现毛刺输出;2、使静态时序分析变得复杂;

.

触发器优缺点:

优点:1、边沿触发,同步设计,不易受毛刺影响;2、时序分析简单;

缺点:面积比latch大;消耗的门电路多;

3、

Which of the following items can help reduce test time(AB)

A. Increase Operation Voltage.

B. Increase scan shift clock frequency.

C. Utilize more scan IOs.

D. Insert gating logic.

解析:增大电压能缩短延时,提高时钟频率,可降低工作时间。扇出越多延时越大,组合逻辑越多延时越大。

4、Cell Delay can be calculated based on:( AD)

A. input transition. B. input load. C. output transition. D. output load.

5、

7nm工艺中的7nm指的是(C)

A. 芯片中最小晶体管的源极长度.

B. 芯片中最小晶体管的源极宽度.

C. 芯片中最小单元的沟道长度.

D. 芯片中最小单元的源极宽度.

6、

Assume A[3:0]=4’b0101,B[3:0]=4’b1111,which statement is correct( B )?

A. if C=&(A|B),then C=1’b0.

B. if C=(|A)&(|B),then C=1’b1.

C. if C=|(A&B),then C=1’b0.

D. if C=(&A)|(&B),then C=1’b0.

7、

We need to define clock specifications in SDC file,using commands like below:create_clock -name GFXCLK -period 600 -waveform {0 300}.What can we know from this command? ——ABD

A. Clock frequency. B. Clock duty cycle. C. Clock source latency. D. Clock name.

寒武纪

1、

SRAM面积大小与那些因素相关(ABCD)

A、 容量,即总的bit数目

B、地址译码方式

C、禁布区

D、BIST电路

2、

自底向上(Bottom-Up)综合策略的优点是(BCD)

A.需要进行多次迭代

B.可以根据不同模块的不同特点和要求单独进行优化

C.对内存要求较小并且可以在多个机器上并行执行

D.某个模块修改后不必重新综合整个设计,减少了综合时间

商汤科技

1、如果线网类型变量说明后未赋值,起缺省值是(z)?

2、某设计中使用了DDR3-1066,数据位宽32bit,FPGA工程中实现的DDR3 controller时钟为800MHz, 应用端时钟为200MHz, 数据位宽为128bit,请问,应用端DDR3可用的理论带宽为(B)

A、4264MB/ s

B、3200MB/ s

C、6400MB/ s

D、2132MB/ s

解析:带宽是电路可以保持稳定工作的频率范围。

带宽 = 时钟频率 * 总线位数 /8

应用端带宽 = 200mhz * 128 bit / 8 = 2300MB/s